ВОПРОСЫ К ЭКЗАМЕНУ ПО ДИСЦИПЛИНЕ «ПРОГРАММИРУЕМЫЕ ЦИФРОВЫЕ УСТРОЙСТВА»

История появления микросхем программируемых цифровых устройств. Предшественники ПЛИС.

Интегральная схема создана в 1959г. в США (Fairchild Motorola).

Первые программируемые логические устройства создавались на основе технологии биполярных программируемых ПЗУ с дополнительными логическими возможностями и свойствами. Фирма Signetics выпустила в 1972 году биполярную микросхему программируемой логической матрицы. Совершенствование архитектуры привело к созданию фирмой Monolithic Memories Inc. (MMI) в 1975–1976 годах микросхем программируемой матричной логики (PAL), монтируемых в 20- и 24-выводные корпуса и способных заменить до 20 имевшихся в продаже логических вентилей. В 1984-м фирма Altera выпустила первую микросхему CPLD содержащую 300 вентилей. И уже сегодня логическая емкость микросхем ПЛИС с конфигурационной флэш-памятью превышает 1 млн вентилей. К классу программируемых логических приборов относятся простые и сложные ПЛИС (SPLD и CPLD, соответственно), а также программируемые пользователем базовые матричные кристаллы (FPGA).

Программируемые логические интегральные схемы (ПЛИС) позволяют в сжатые сроки создавать высокоскоростные периферийные модули, шинные интерфейсы (PCI, USB), сетевые устройства, контроллеры и др.

ПЛИС - это цифровая интегральная схема с программируемой структурой.

Виды ПЛИС:

1. программируемые логические матрицы (PLA)

2. программируемая матричная логика (PAL)

3. базовые матричные кристаллы (GA)

Микросхемы типа программируемая логическая матрица. Их основные параметры. Упрощенная схема.

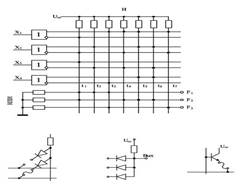

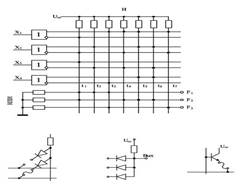

Программируемые логические матрицы (ПЛМ) появились к восьмидесятым годам. Основой служат последовательность программируемых матриц элементов «И» и «ИЛИ», а также блоки входных и выходных буферных каскадов (БВх и БВых).

Структура ПЛМ:

Основные параметры ПЛМ:

- Число входов t;

- Число термов 1;

- Число выходов n;

- матрица И - конъюнкторы;

- матрица ИЛИ - дизъюнкторы.

Число формируемых термов равно числу коньюнкторов (И). Число дизьюнкторов (ИЛИ) равно числу вырабатываемых функций n.

ПЛМ реализует дизъюнктивную нормальную форму (ДНФ) воспроизводимых функций (двухуровневую логику).

Какие именно термы будут выработаны и какие комбинации этих термов составят выходные функции, определяется программированием ПЛМ.

Схемотехника ПЛМ:

Выпускаются ПЛМ как на основе биполярной технологии, так и на МОП-транзисторах. В матрицах имеются системы горизонтальных и вертикальных связей, в узлах, пересечения которых при программировании создаются или ликвидируются узлы связи.

Реализуемые функции можно усложнять, вводя например один из выходов на вход. Тогда можно реализовать более сложную, скобочную форму функции.

Базовая ячейка БМК.

БМК — кристалл, на прямоугольной поверхности которого размешены внутренняя и периферийная области (ВО и ПО). Во внутренней области по строкам и столбцам (в виде матрицы) расположены базовые ячейки. Элементный состав базовой ячейки допускает реализацию некоторого множества схем определенного класса, каждая из которых соответствует определенной функциональной ячейке. Для выпускаемого в продажу БМК создается библиотека функциональных ячеек, т. е., рисунков межсоединений.

Базовая ячейка (БЯ) - некоторый набор схемных элементов, регулярно повторяющийся на определенной площади кристалла. Этот набор может состоять из нескоммутированных элементов, а также из частично скоммутированных. Базовые ячейки внутренней области БМК именуются матричными базовыми ячейками (МБЯ), ячейки периферийной зоны — периферийными базовыми ячейками (ПБЯ). Применяются два способа организации ячеек БМК:

· из элементов МБЯ может быть сформирован один логический элемент, а для реализации более сложных функций используются несколько ячеек;

· из элементов МБЯ может быть сформирован любой функциональный узел, а состав элементов ячейки определяется схемой самого сложного узла.

Функциональная ячейка (ФЯ) – функционально законченная схема, реализуемая путем соединения элементов в пределах одной или нескольких БЯ.

Библиотека функциональных ячеек - совокупность ФЯ, используемых при проектировании. Библиотека содержит большое число функциональных элементов, узлов и их частей. Библиотечные элементы имеют различную сложность (логические элементы, триггеры, более сложные узлы или их фрагменты). В состав библиотечного элемента могут входить одна или несколько БЯ. Площадь библиотечного элемента кратна площади БЯ.

Микросхемы типа «система на кристалле» (SoC).

Слияние двух путей развития микропроцессоров и ПЛИС в единое целое и размещением на одном кристалле, связанных между собой микропроцессорного ядра и массива вентилей ПЛИС привело к разработке СБИС класса SоC (Sistems On Chip), т. е. «систем на кристалле».

Фирма Atmel в октябре 1999 г. выпустила первое семейство СБИС.

Миниатюрность обеспечивается за счет размещения основных компонентов системы на одной микросхеме (ПЛИС или СБИС). В состав SoC входит микроконтроллер, память и контроллер памяти.

Универсальность заключается в возможности использования системы на кристалле в различных устройствах с минимальными изменениями схемотехники SoC. Основные изменения выполняются в программе микроконтроллера, который программируется на языке Си или ассемблере.

Особенностью данной системы является то, что кроме шины процессора, на которую можно присоединять внешние устройства, есть ещё 3 внешних независимых канала DMA (Direct Memory Access - прямой доступ к памяти). Это позволяет быстро обмениваться данными между процессором и внешними устройствами. Характеристики основных компонентов системы на кристалле:

Микроконтроллер. 8-ми битный RISC процессор с раздельной памятью программ и оперативной памятью.

Шина микроконтроллера. Это шина данных, адреса и набор контрольных сигналов для управления чтением и записью.

Контроллер памяти. Контроллер обеспечивает связь процессора с оперативной памятью, а так же содержит в себе DMA-контроллер с 3 независимыми каналами для подсоединения внешних устройств.

DMA-контроллер. 8-ми битный DMA-контроллер с 3 каналами.

Внешнее устройство (устройства) пользователя. Типовое включение внешнего устройства следующее: обмен данными происходит через DMA-каналы; контрольная информация и данные управления отображается на регистрах контроллера. Разработанная система на кристалле может использоваться для преобразования различных (в том числе и высокоскоростных) интерфейсов, сложной цифровой обработки и решения задач в области коммуникаций, промышленной автоматизации и мультимедиа технологий.

Макроячейка ПЛИС типа CPLD.

МЯ может быть запрограммирована на сброс или предустановку по включению питания. Регистр МЯ может быть сконфигурирован как D-триггер, Т-триггер, регистр-защелка или не задействован, если МЯ необходима для реализации комбинаторной функции. Каждый из указанных выше триггеров может тактироваться от любого из восьми источников сигнала или его инверсии. К этим источникам тактового сигнала относятся: 2 глобальных тактовых сигнала, выбранные из четырех глобальных сигналов, поступающих напрямую от контактов микросхемы; общий сигнал синхронизации (терм от одного из ФБ кристалла); локальные термы управления (из данного ФБ) - LCT[4:7]; терм синхронизации РТС. В МЯ существует две мультиплексные связи с переключающей матрицей ZIA. Один мультиплексор выбирает либо выход мультиплексора VFM, либо выход регистра. Другой мультиплексор выбирает либо выход регистра, либо сигнал с контакта микросхемы. Когда контакт ввода-вывода используется как выход, выходной буфер задействован, линия обратной связи МЯ может быть использована для реализации обратной связи внутри МЯ. Когда контакт ввода-вывода используется как вход, выходной буфер переведен в третье состояние и соединение контакта ввода-вывода с переключающей матрицей осуществляется через линию обратной связи ячейки ввода-вывода. Если контакт микросхемы используется как регистровый вход, то соединение контакта и входа регистра осуществляется по линии прямой связи, что обеспечивает минимальное время установки сигнала. Если регистр МЯ сконфигурирован как регистр-защёлка, вход разрешения тактирования регистра МЯ не функционирует.

Числовые типы

В VHDL поддерживается два основных типа для представления чисел: целочисленный и тип с плавающей запятой.

Тип Integer

Для представления целых чисел используется тип integer. Этот тип позволяет представить числа в диапазоне от —2 до 2

Тип Real

Для представления действительных чисел используется тип Real. Он имеет диапазон от -1.0Е+38 до 1.0Е+38.

Физические типы данных

Для представления физических величин (таких как длина, масса, время), в языке VHDL используются так называемые физические типы. Данные, принадлежащие к физическому типу, определяются своим значением и единицей измерения. Для одного и того же физического параметра может использоваться множество единиц измерения.

Организация физических типов в VHDL позволяет установить соответствие между различными единицами измерения. К физическим типам может быть применено большинство арифметических операторов, но с некоторыми ограничениями.

Описание времени

VHDL поддерживает встроенный физический тип time для описания времени.

Перечислимые типы данных

Перечислимые типы могут задаваться двумя способами: диапазоном и списком значений.

Подтипы

Нередко модель содержит объекты, которые могут принимать значения только в строго ограниченной области из множества возможных значений какого-либо типа. Тип таких объектов можно определить на базе основного типа. Он будет называться подтипом этого типа. Использование подтипов облегчает понимание модели.

Массивы

Массив представляет собой набор элементов одного и того же типа. Позиция каждого элемента задается скалярным значением — индексом.

Задание начальных значений массиву на языке VHDL. Ассоциирование.

Начальные значения объектам типа массив могут задаваться тремя способами.

Прямое определение - начальные значения элементов могут задаваться списком, в котором первое значение соответствует первому элементу массива, а каждое последующее — последующему элементу.

Агрегатирование – агрегаты могут использоваться для задания значений нескольким переменным или сигналам одновременно. Это определение имеет следующий синтаксис:

(namel, name2,...,name_n)<=name_aggregate

Ассоциирование. Выполняется ассоциирование значения индекса со значением элемента, т. е. сопоставление элементу с указанным индексом заданного значения элемента. Это определение имеет следующий синтаксис: ({index_values=>element_value),...); где index_value — может представлять:

□ простое выражение;

□ интервал (в этом случае все элементы, индексы которых попадают в этот интервал, будут иметь одно и то же значение);

□ список значений индексов;

□ others (в этом случае все элементы, индексы которых не вошли ни в одно из предыдущих определений, будут иметь указанное значение), others должно быть последним в списке.

Если задается список значений индексов, то его элементы отделяются друг от друга вертикальной чертой.

Например:

type synbol is (‘а', 't', 'd', 'h', cr);

type state is range 0 to 2

type matrix is array (state, symbol) of state;

constant n_state:matrix:=(0=>('a'=>l, 'd'=> 2. others =>0),

l=>('a’|'h'=>2, others=>0),

2=>('a' to 'h"=>l, others=>2));

Задание начальных значений массиву на языке VHDL. Агрегаты.

Начальные значения объектам типа массив могут задаваться тремя способами:

Прямое определение - начальные значения элементов могут задаваться списком, в котором первое значение соответствует первому элементу массива, а каждое последующее — последующему элементу.

Ассоциирование. Выполняется ассоциирование значения индекса со значением элемента, т. е. сопоставление элементу с указанным индексом заданного значения элемента.

Агрегаты. Могут использоваться для задания значений нескольким переменным или сигналам одновременно. Это определение имеет следующий синтаксис:

(namel, name2.....name_n)<=name_aggregate

Например, пусть имеются четыре переменных типа bit и переменная типа bit_vector длины 4. Для того чтобы присвоить переменным значения элементов этого вектора, можно выполнить следующее действие: (z_flag, n_flag, v_flag, c_flag)<=flag_reg;

Фрагменты массива(slire).

Type array_1 is array(1 to 100) of integer

Variable a1:array_1;

a1(20 to 50) фрагмент 1 из 31 элемента

a1(60 downto 40) фрагмент 2 из 21 элемента

К фрагментам применимы все операции, как и к массиву в целом.

Оператор CASE языка VHDL.

Оператор case – последовательный оператор, который по условию выполняет одну ветвь в зависимости от величины выражения селектора и имеет следующий синтаксис:

case выражение is

{when выборы =>

последовательные операторы}

…

end case;

Выражение, стоящее после case (селектор), должно принимать дискретный набор значений. Значение этого выражения сравнивается со значениями, стоящими после when (их тип должен совпадать). Выполняется последовательность действий, стоящая после первого же when, для которого было обнаружено совпадение. Если необходимо, чтобы выполнялась некоторая последовательность действий при отсутствии совпадений, то используется конструкция when others, после которой и задаётся эта последовательность. Эта конструкция должна быть последней в операторе.

Например:

type alu_func is (pass1, pass2, pass3, pass4);

variable func: alu_func;

case func is

when pass1 => result:=operand1;

when pass2 => result:=operand2;

when others => result:=0;

end case;

Если нескольким значениям селектора соответствует одна и та же последовательность действий, они могут быть перечислены после одного when. Разделителем служит вертикальная черта.

Например:

when load | add | subs =>operand:=mem_operand;

Оператор assert.

При отладке модели полезно контролировать значения, которые принимают объекты, и заносить информацию, получаемую в ходе работы модели, в отчет о проведенном моделировании. Для этого в программу на языке VHDL вводятся специальные операторы, управляющие сбором и сохранением информации о прогоняемой модели.

Для этих целей используется оператор assert, который имеет следующий синтаксис:

assert логическое выражение [report выражение1] [severity выражение2]

Если логическое выражение, стоящее в операторе assert, принимает в ходе моделирования значение false, моделирующая программа немедленно выдает уведомление об этом. Выражение, стоящее в секции report (если она имеется), при этом заносится в отчет. Это выражение может содержать текстовые строки, в качестве которых могут быть использованы атрибуты объектов, приводящие их значения к текстовому типу. Выражение, стоящее в секции severity, позволяет определить уровень ошибки. Оно должно принимать одно из значений, принадлежащих типу severity_level, определение которого выглядит следующим образом:

type severity_level is (note, warning, error, failure);

Например:

assert free_mem<=low_limit report "memory is small" severity warning;

Значение note соответствует ситуации, когда необходимо просто поместить информативное сообщение в отчет. Значение warning соответствует ситуации, когда в ходе выполнения модели возникло нечто, не характерное для нее. Уровень error используется, когда возникшая ситуация свидетельствует об ошибке. Уровень failure свидетельствует о нарушении целостности.

Оператор report

Если информация должна заноситься в отчет при любых условиях, то используется оператор report безусловного занесения информации в отчет. Он имеет следующий синтаксис:

report выражение1 [severity выражение2];

Инерционная задержка

Цифровые схемы обладают определенной инерционностью. Для формирования сигнала на выходном контакте, в ответ на изменение входного сигнала, требуется некоторое количество энергии и определенное время. Чтобы на выходе сформировался устойчивый сигнал, входной сигнал должен продержаться в новом состоянии не менее некоторого промежутка времени. Если же входной сигнал не простоит в этом состоянии нужное время, то вызванные им изменения состояния схемы не успеют распространиться до рассматриваемого выхода.

Для представления этого вида задержек распространения сигналов в языке VHDL используется понятие инерционной задержки (inertial delay), в операторе присваивания — ключевое слово inertial.

До тех пор, пока входной сигнал изменяется не чаще, чем время, указанное в секции after, изменения выходного сигнала происходят в соответствии с изменениями входного, но с учетом указанной задержки. Если же изменения входного сигнала происходят чаще, чем время, указанное в секции after, они игнорируются.

Когда минимальная длительность входного сигнала, приводящая к изменению выходного сигнала, меньше заданной задержки, для ее указания используется секция reject.

Например, в операторе присваивания значения сигналу можно указать:

z <= reject 3 ns inertial (x xor у) after 7 ns;

Здесь минимальная длительность импульса на входах х и у установлена равной 3 ns, в то время как задержка формирования выходного сигнала z равна 7 ns. При длительности, меньшей 3 ns, импульс отфильтровывается, отбрасывается системой моделирования и не приводит к формированию нового значения выходного сигнала z.

Если в операторе присваивания значения сигналу присутствует секция inertial и несколько секций after, то секция inertial применяется только к первой секции after, а к остальным секциям after применяются правила работы с транспортными задержками.

Транспортная задержка

Часто в модели необходимо, чтобы изменения сигналов любой длительности не отбрасывались, а отрабатывались системой моделирования и влияли на формирование выходных сигналов.

В отличие от инерционных задержек, транспортные задержки не накладывают ограничений на минимальную длительность импульса, не отфильтровывают короткие входные импульсы, а пропускают в схему любые входные сигналы.

Дельта-задержка сигналов

Особая ситуация складывается в модели устройства на языке VHDL, если оператор присваивания нового значения сигналу устанавливает нулевую задержку. Если отсутствует секция after, то считается, что задержка изменения сигнала составляет 0 нс. В реальных устройствах такие ситуации невозможны.

Решение проблемы: система моделирования, закончив текущий цикл моделирования для момента t1 модельного времени, не сразу переходит к следующему моменту модельного времени t2 > t1 (например, t2 = t1 + 1). Она проверяет, имеются ли изменения сигналов, вновь запланированные на момент t1. Если выявлены новые изменения сигналов на тот же момент t1 модельного времени, то система моделирования выполняет новый цикл моделирования, отрабатывая эти изменения. И так далее, пока не будет определено, что по результатам текущего цикла моделирования не появилось новых сигналов, запланированных на момент t1, после чего система переходит к моделированию момента t2 модельного времени.

Дельта-задержке не приписывается никакого числового значения (используется только для упорядочивания последовательности событий в модели и отрабатывающих их циклов работы системы моделирования).

Дельта-задержка — задержка условная позволяющая отразить зависимость изменения сигналов при нулевых задержках и соответствующую им последовательность дельта-циклов — циклов внутренней работы системы моделирования.

Декларация компонента

Для того чтобы один объект моделирования мог быть включен в состав другого объекта, его необходимо декларировать как компонент.

Декларация компонента должна полностью совпадать с декларацией соответствующего ему объекта моделирования, но ключевое слово entity заменяется ключевым словом component.

Декларация компонента имеет следующий синтаксис:

Component имя компонента is [generic (generic_interface_list);]

[port (port_interface_list);]

end component [имя компонента];

Имя компонента является типом компонента. В структурном описании архитектурного тела могут быть несколько компонентов, к которым применима эта декларация.

Декларация компонентов может размещаться в декларативной части объектов моделирования и может быть расположена и в тех файлах, в которых описаны объекты моделирования, используемые в качестве компонентов.

Декларация компонента

Для того чтобы один объект моделирования мог быть включен в состав другого объекта, его необходимо декларировать как компонент.

Декларация компонента должна полностью совпадать с декларацией соответствующего ему объекта моделирования, но ключевое слово entity заменяется ключевым словом component.

Декларация компонента имеет следующий синтаксис:

Component имя компонента is [generic (generic_interface_list);]

[port (port_interface_list);]

end component [имя компонента];

Имя компонента является типом компонента. В структурном описании архитектурного тела могут быть несколько компонентов, к которым применима эта декларация.

Декларация компонентов может размещаться в декларативной части объектов моделирования и может быть расположена и в тех файлах, в которых описаны объекты моделирования, используемые в качестве компонентов.

Включение компонента в модель объекта. Структурное описание объекта моделирования, находящегося на верхнем уровне иерархии, состоит из назначений компонентов. В рамках этих назначений определяются фактические значения обобщающих констант и связи с другими объектами.

Задав декларацию компонентов, мы описываем спецификацию проектируемого объекта, определив, какого типа компоненты в него входят. С помощью конструкции instantiation — оператора назначения компонента, мы устанавливаем компоненты в проектируемый объект и связываем их в некоторую структуру.

Оператор назначения компонента имеет следующий синтаксис:

instantiation__label:

[component] component_name

[generic map (generic_association_list);]

[port map (port_association_list)];

Операторы назначения компонентов являются параллельно выполняемыми.

Имя компонента component_name — это имя типа компонента. Ключевое слово component в операторе назначения компонента не является обязательным.

Секция связей портов компонента port map специфицирует связи данного компонента с сигналами объекта и портами других компонентов. Port_associacion_list содержит список фактических сигналов, связанных с портами компонента.

Каждый элемент в списке (сигнал) ассоциируется с портом объекта моделирования, описанного на один уровень выше, или с его внутренним сигналом, или является независимым, что помечается ключевым словом open.

Список Generic_association_list содержит фактические значения обобщающих констант.

Оператор генерации (generate).

Оператор генерации generate позволяет компактно описать модель. Оператор генерации имеет следующий синтаксис:

Group_label: for index in range generate

Element_label: component_name [generic map (generic_accosiation_list)]

[port map (port_accosiacion_list)]

end generate [Group__label];

Допускается вложенность операторов генерации.

63. Описание переменных и констант на языке VHDL. Литералы.

Описание констант, переменных и сигналов имеет сходную структуру. В начале строки описания указывается ключевое слово, определяющее вид описываемого объекта, затем указывается одно или несколько имен описываемых объектов и их тип. Для констант должно быть указано значение, для переменных и сигналов указание начального значения возможно, но не обязательно.

Описание константы имеет следующий синтаксис:

constant имя константы: имя типа: = значение;

Например:

constant address_length: integer:=4;

Описание переменной имеет следующий вид:

variable имя переменной: имя типа [:=значение];

Например:

variable counter: integer:=7;

Присваивание нового значения переменной:

[метка:]имя:=значение;

Описание сигналов имеет следующий синтаксис:

signal идентификатор: тип сигнала [:=значение];

Например:

signal flagl:bit;

signal flag2:bit:='l';

Литералом задается лексический элемент, который при компиляции кодируется некоторым числовым кодом.

Задание конфигурации компонентов на языке VHDL. Конфигурационная спецификация и конфигурационная декларация.

В общем случае объект моделирования может иметь несколько описаний архитектуры.

entity LA3=> erc 1 bch 1 of LA3

erc 2 bch 2 of LA3

…..

Для задания нужного описания используется конфигурация, т. е. связывание объекта с одним из описаний его архитектуры. Использование конфигурации позволяет создавать гибкие модели.

Формы задания конфигурации:

1.)Конфигурация спецификации:

for(метка экземпляра компонента, all, others): имя_компонента

use entity имя_entity[(имя архитектуры тела)];

end for;

Пример:

for bit0, bit1:flipflop

use entity work. edge_triggered_dff(basic);

end for;

Изменение конфигурации спецификации приводит к изменению текста модели объекта, что неудобно.

2.) Конфигурация декларации содержит ту же информацию, что и спецификация но может быть расположена в отдельном файле.

configuration имя_конфигурации of имя_entity is

for имя конфигурации. описания

{for(…) end for;}

end for

end configuration имя_конфигурации.

Пример:

сonfiguration conf1 of ent_bit is

for ent_bits_struct

for bit0, bit1:flipflop

use entity work. edge_triggered_dff(basic);

end for;

end for;

end configuration conf1;

Задание конфигурации компонентов на языке VHDL. Правила связывания по умолчанию.

В общем случае объект моделирования может иметь несколько описаний архитектуры.

entity LA3=> erc 1 bch 1 of LA3

erc 2 bch 2 of LA3

…..

Для задания нужного описания используется конфигурация, т. е. связывание объекта с одним из описаний его архитектуры. Использование конфигурации позволяет создавать гибкие модели.

Формы задания конфигурации:

1.)Конфигурация спецификации:

for(метка экземпляра компонента, all, others): имя_компонента

use entity имя_entity[(имя архитектуры тела)];

end for;

Пример:

for bit0, bit1:flipflop

use entity work. edge_triggered_dff(basic);

end for;

Изменение конфигурации спецификации приводит к изменению текста модели объекта, что неудобно.

2.) Конфигурация декларации содержит ту же информацию, что и спецификация но может быть расположена в отдельном файле.

configuration имя_конфигурации of имя_entity is

for имя конфигурации. описания

{for(…) end for;}

end for

end configuration имя_конфигурации.

Пример:

сonfiguration conf1 of ent_bit is

for ent_bits_struct

for bit0, bit1:flipflop

use entity work. edge_triggered_dff(basic);

end for;

end for;

end configuration conf1;

Правила связывания по умолчанию:

a. Для компонентов автоматически имеется объект с тем же именем;

2.) если используется архитектура тел, то для связывания используется то, которое компилируется последним

ВОПРОСЫ К ЭКЗАМЕНУ ПО ДИСЦИПЛИНЕ «ПРОГРАММИРУЕМЫЕ ЦИФРОВЫЕ УСТРОЙСТВА»

История появления микросхем программируемых цифровых устройств. Предшественники ПЛИС.

Интегральная схема создана в 1959г. в США (Fairchild Motorola).

Первые программируемые логические устройства создавались на основе технологии биполярных программируемых ПЗУ с дополнительными логическими возможностями и свойствами. Фирма Signetics выпустила в 1972 году биполярную микросхему программируемой логической матрицы. Совершенствование архитектуры привело к созданию фирмой Monolithic Memories Inc. (MMI) в 1975–1976 годах микросхем программируемой матричной логики (PAL), монтируемых в 20- и 24-выводные корпуса и способных заменить до 20 имевшихся в продаже логических вентилей. В 1984-м фирма Altera выпустила первую микросхему CPLD содержащую 300 вентилей. И уже сегодня логическая емкость микросхем ПЛИС с конфигурационной флэш-памятью превышает 1 млн вентилей. К классу программируемых логических приборов относятся простые и сложные ПЛИС (SPLD и CPLD, соответственно), а также программируемые пользователем базовые матричные кристаллы (FPGA).

Программируемые логические интегральные схемы (ПЛИС) позволяют в сжатые сроки создавать высокоскоростные периферийные модули, шинные интерфейсы (PCI, USB), сетевые устройства, контроллеры и др.

ПЛИС - это цифровая интегральная схема с программируемой структурой.

Виды ПЛИС:

1. программируемые логические матрицы (PLA)

2. программируемая матричная логика (PAL)

3. базовые матричные кристаллы (GA)