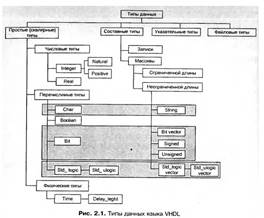

VHDL является языком со строгой типизацией. Каждый тип данных в VHDL имеет определенный набор принимаемых значений и набор допустимых операций. В языке предопределено достаточное количество простых и сложных типов, а также имеются средства для образования типов, определяемых пользователем.

Простые типы

Следующие простые типы являются предопределенными и базовыми:

BOOLEAN (логический) – объекты данного типа могут принимать значения FALSE (ложь) и TRUE (истина).

INTEGER (целый) – значения данного типа представляют собой 32-разрядные числа со знаком.

BIT (битовый) – представляет один логический бит. Объекты данного типа могут содержать значение '0' или '1'.

STD_LOGIC (битовый)/STD_ULOGIC (битовый) – представляет один бит данных. Объекты данного типа могут принимать 9 состояний.

ENUMERATED (перечислимый) – используется для задания пользовательских типов.

CHARACTER – символьный тип.

Для типа STD_ULOGIC не определена функция разрешения. В языке VHDL функция разрешения используется для определения значения сигнала, имеющего несколько источников (драйверов).

Подтипы

Использование подтипов позволяет объявлять объекты, принимающие ограниченный набор значений из диапазона, допустимого для базового типа. Подтипы применяются в двух случаях:

1) Подтип может ограничить диапазон значений базового скалярного типа (ограничение по диапазону). В этом случае объявление подтипа выглядит следующим образом:

SUBTYPE имя_подтипа IS имя__базового_типа RANGE диапазон_индексов;

Базовый тип и ограничение диапазона могут быть включены непосредственно в объявление объекта. Объявление сигнала А, эквивалентное приведенному выше, будет выглядеть следующим образом:

SIGNAL A: severity RANGE OKAY TO WARNING;

Подтипы, объявленные таким образом, могут также участвовать в описании ограниченных массивных типов

2) Подтип может определить границы диапазона индексов для неограниченного массивного типа. В этом случае объявление подтипа выглядит следующим образом:

SUBTYPE имя_поддиапазона IS имя_базового_типа (диапазон_индексов, диапазон_ивдексов);

Составные типы. Массивы. Размерность массива.

VHDL обеспечивает два вида составных типов: массивы и записи.

Массивы

Массив представляется набором одного или более идентичных элементов, рассматриваемых как одномерный вектор, двумерная матрица или как произвольная прямоугольная структура более высокой размерности. Объявление массивного типа может быть объявлением неограниченного или ограниченного массива, или объявлением массивного подтипа. Любому скаляру из массива может быть присвоено значение. Элемент массива может быть выбран путем задания значения индекса вместе с именем массива.

Примеры определения одномерного массива:

type word is array (0 to 31) of bit;

type state is (initial, idle, active, error);

tуре state_count is array (state range idle to error) of natural,

Определение типа многомерного массива отличается от определения одномерного тем, что количество определений индексов равно размерности массива. Определения индексов отделяются друг от друга запятыми. Например:

type matrix ia array (1 to 3, 1 to 3) of integer

Обращение к элементу многомерного массива осуществляется указанием всех его индексов, заключенных в круглые скобки, через запятую. Например:

variable matrix1: matrix;

Matrix (l,3):=15.

Задание начальных значений массиву на языке VHDL. Ассоциирование.

Начальные значения объектам типа массив могут задаваться тремя способами.

Прямое определение - начальные значения элементов могут задаваться списком, в котором первое значение соответствует первому элементу массива, а каждое последующее — последующему элементу.

Агрегатирование – агрегаты могут использоваться для задания значений нескольким переменным или сигналам одновременно. Это определение имеет следующий синтаксис:

(namel, name2,...,name_n)<=name_aggregate

Ассоциирование. Выполняется ассоциирование значения индекса со значением элемента, т. е. сопоставление элементу с указанным индексом заданного значения элемента. Это определение имеет следующий синтаксис: ({index_values=>element_value),...); где index_value — может представлять:

□ простое выражение;

□ интервал (в этом случае все элементы, индексы которых попадают в этот интервал, будут иметь одно и то же значение);

□ список значений индексов;

□ others (в этом случае все элементы, индексы которых не вошли ни в одно из предыдущих определений, будут иметь указанное значение), others должно быть последним в списке.

Если задается список значений индексов, то его элементы отделяются друг от друга вертикальной чертой.

Например:

type synbol is (‘а', 't', 'd', 'h', cr);

type state is range 0 to 2

type matrix is array (state, symbol) of state;

constant n_state:matrix:=(0=>('a'=>l, 'd'=> 2. others =>0),

l=>('a’|'h'=>2, others=>0),

2=>('a' to 'h"=>l, others=>2));

Задание начальных значений массиву на языке VHDL. Агрегаты.

Начальные значения объектам типа массив могут задаваться тремя способами:

Прямое определение - начальные значения элементов могут задаваться списком, в котором первое значение соответствует первому элементу массива, а каждое последующее — последующему элементу.

Ассоциирование. Выполняется ассоциирование значения индекса со значением элемента, т. е. сопоставление элементу с указанным индексом заданного значения элемента.

Агрегаты. Могут использоваться для задания значений нескольким переменным или сигналам одновременно. Это определение имеет следующий синтаксис:

(namel, name2.....name_n)<=name_aggregate

Например, пусть имеются четыре переменных типа bit и переменная типа bit_vector длины 4. Для того чтобы присвоить переменным значения элементов этого вектора, можно выполнить следующее действие: (z_flag, n_flag, v_flag, c_flag)<=flag_reg;