Обработка информации в ЭВМ организуется на основе принципа программного управления. Управление работой ВМ производится посредством управляющих слов, называемых командами.

УУ организует выполнение ЭВМ вычислений, начиная с момента ввода в машину программы и кончая вычислениями и выдачей результата.

Выполнение каждой команды, входящей в состав программы, требует, чтобы УУ:

1) получало из ЗУ команду, выполняемую в настоящий момент;

2) определяло адрес ячейки ЗУ, хранящей следующую команду;

3) организовывало выполнение текущей команды;

4) вырабатывало управляющие сигналы, определяющие время выполнения каждого шага текущей команды.

Код текущей команды передается в УУ из ячейки ЗУ имеющей адрес, найденный в процессе выполнения предыдущей команды. УУ вырабатывает сигнал на выходной шине, имеющей номер соответствующий коду операции, содержащейсяв команде. Тем самым, все устройства ЭВМ подготавливаются к выполнению команды.

Команда предписывает некоторую операцию из числа операций, реализуемых ЭВМ, и указывает операнды, участвующие в операции. Операция задается кодом, соответствующим наименованию операции, и операнды – адресами, определяющими машинные наименования операндов. Алгоритм решения задачи представляется в виде совокупности команд и называется программой.

Организация выполнения текущей команды сводится к подаче УУ ЭВМ сигналов на управляющие шины АЛУ, ОЗУ, УВВ в соответствии с осуществляемым тактом выполняемой команды. Так осуществляется чтение в ОЗУ чисел,участвующих в выполнении команды, передача их в АЛУ, работа последнего, выдача результата и запись его в ОЗУ или хранение результата в регистрах АЛУ. В случае других команд УУ управляет вводом в ЗУ программы вычислений и исходных данных или выдачей результатов во внешнее ЗУ и печатью результатов.

Список операций, реализуемых ВМ, определяется на основе алгоритмов, для выполнения которых предназначается ВМ, и зависит от способа структурной организации ВМ, в частности от состава и порядка взаимодействия устройств, средствами которых реализуется все множество операций. Множество операций разделяются на группы:

1) основные,

2) посылочные,

3) управления,

4) ввода-вывода,

5) системные.

Основные операции реализуются процессором и состоят в преобразовании информации, представляющей числа, логические значения и строки символов. В группу основных операций включаются операции двоичной арифметики, логические операции и операции над строками символов.

Посылочные операции состоят в передаче слов информации между процессором и оперативной памятью (ОП).Операции данной группы обеспечивают передачу слов из ОП в процессор – загрузку слов в процессор – и передачу слов из процессора в память – запись слов.

Операции управления служат для управления порядком следования команд. Обычно команды выполняются в естественном порядке – в порядке их следования в программе. Операции управления обеспечивают возможность перехода к выполнению команды, размещаемой в любом месте программы. Переходы могут выполняться безусловно, либо в зависимости от условий, определяемых текущими значениями признаков, которые формируются процессором путем анализа результата выполнения предыдущих операций (отрицательные и нулевые результаты, переполнение, потеря значимости и т.д.).

Операции ввода-вывода служат для передачи информации между внешними устройствами и ОП. Операции ввода-вывода обеспечивают чтение информации с устройств ввода, запись информации на устройства вывода и обмен информацией между ОП и внешним ОЗУ.

Системные операции используются для организации мультипрограммной работы ВМ или работы ВМ в составе системы совместно с другими ВМ. Системные операции обеспечивают переключение средств защиты памяти и обмен управляющей информацией между ВМ или процессорами ВС.

Операции выделяются посредством кодов, устанавливающих машинные номера операций. Код операции указывается в команде. Для кодирования операций используются двоичные коды минимальной длины.

Выполнение процессором программы решения задачи представляет собой последовательность операций, осуществляемых в заданном программой порядке. К таким операциям относятся арифметические и логические операции, операции связанные с анализом получающихся результатов, с организацией и управлением процессом вычислений. Обычно каждой такой операции соответствует команда программы.

Команда представляет собой код определяющий операцию ВМ и данные, участвующие в операции.

В свою очередь, операция (выполнение команды) может быть разделена на более мелкие этапы (микрооперации), во время которых исполняются определенные элементарные действия. Конкретный состав микроопераций и последовательность их выполнения определяются системой команд, логической структурой и особенностями данной ЭВМ. Для разных ЭВМ понятия «операция» и «микрооперация» могут иметь различное содержание. Последовательность микроопераций, реализующих данную операцию (команду) образует микропрограмму операции. Для характеристики временных соотношений между различными этапами операций используется понятие машинный такт. Он определяет интервал времени, в течение которого выполняется одна или одновременно несколько микроопераций процессора. Таким образом, может быть установлена следующая иерархия этапов выполнения программы в процессоре: программа, команда (микропрограмма), микрооперация.

Защита информации

Защита информации необходима, когда машина имеет дело более чем с одной задачей одновременно и (или) более чем с одним человеком-оператором, для того, чтобы обеспечить защиту информации, принадлежащей одной задаче (одному оператору) от воздействия программ других задач или других операторов.

В более сложных устройствах аппаратура защиты устанавливает разный статус для разных участков памяти. Например, некоторому пользователю могут быть разрешены произвольные обращения к одним участкам памяти, обращения только для чтения информации в качестве программы- к третьим участкам, и запрещены любые обращения к четвёртым участкам памяти.

Различия между чтением некоторой информации в качестве данных и в качестве программы делается в тех случаях, когда нужно запретить пользователю выводить из машины или делать копии с программ входящих в состав ПО.

Цепи защиты памяти являются частью устройств формирования исполнительных адресов и будем рассматривать их вместе с этими устройствами.

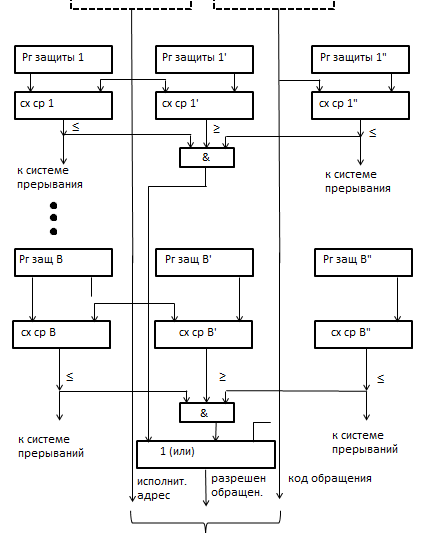

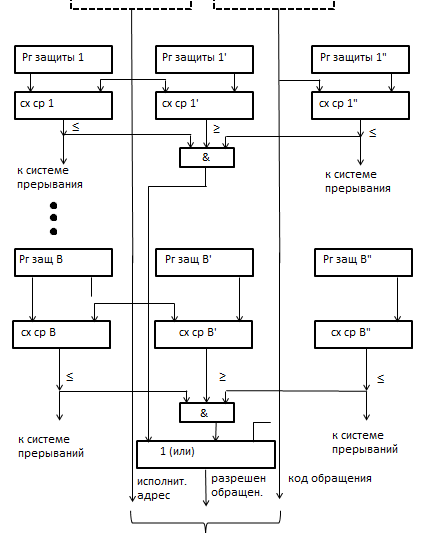

При реализации функций защиты памяти аппаратура относительной адресации должна быть дополнена специальными цепями защиты (рисунок 7.20). Схема рассчитана на возможность выделения программе пользователя до β различных областей памяти, к которым ей разрешено будет обращаться. Для каждой из областей в отдельности можно установить свой статус, в соответствии с которым программа пользователя сможет обращаться к этой области либо произвольным образом, либо только для чтения команд. Границы областей и статус каждой из областей будет устанавливаться ОС программным путём.

Исполнит. адрес Код обращения

Рисунок 1.4 – Защита памяти при относительной адресации

На рисунке 1.4 каждой i -й области ЗУ (i=1,2,, …., β) соответствуют три регистра защиты: Рг  , Рг защ

, Рг защ

Цепи засылки информации в эти регистры на рисунке не показаны. Информация в регистры защиты может засылаться программным путём, но только в режиме системы, то-есть при выполнении специальных привилегированных операций. Таким образом, программа пользователя не имеет средств для изменения информации в регистрах защиты.

Регистры  указывают соответственно верхнюю нижнюю границы i- й области памяти, отведенной программе пользователя.

указывают соответственно верхнюю нижнюю границы i- й области памяти, отведенной программе пользователя.

С каждым из Рг  связано по одной схеме сравнения, Сх. ср. i и Сх.ср.

связано по одной схеме сравнения, Сх. ср. i и Сх.ср.  , выполняющие сравнение информации, находящейся в регистрах

, выполняющие сравнение информации, находящейся в регистрах  с исполнительным адресом, по которому предполагается выполнить обращение к памяти. Если величина, находящаяся в

с исполнительным адресом, по которому предполагается выполнить обращение к памяти. Если величина, находящаяся в  меньше или равна исполнительному адресу, то схема Сх.ср. i формирует сигнал ≤. Аналогичным образом, если величина, находящаяся в регистре

меньше или равна исполнительному адресу, то схема Сх.ср. i формирует сигнал ≤. Аналогичным образом, если величина, находящаяся в регистре  адресу, схемой Сх.ср.

адресу, схемой Сх.ср.  формируется сигнал

формируется сигнал  . Наличие обоих этих сигналов одновременно свидетельствует о принадлежности исполнительного адреса i -й области, отведённый пользователю.

. Наличие обоих этих сигналов одновременно свидетельствует о принадлежности исполнительного адреса i -й области, отведённый пользователю.

Однако, для того,чтобы элемент И(&), на входы которого поступают сигналы от схем сравнения Сх.ср.  и Сх.ср.

и Сх.ср.  выработал сигнал разрешения обращения к памяти, необходимо, чтобы на выходе Сх.ср.

выработал сигнал разрешения обращения к памяти, необходимо, чтобы на выходе Сх.ср.  также появился сигнал ≥.

также появился сигнал ≥.

Регистры защиты Ргзащ  и связанные с ними Сх.ср.

и связанные с ними Сх.ср.  предназначены для установления различного статуса для различных областей памяти, открытых программе пользователя.

предназначены для установления различного статуса для различных областей памяти, открытых программе пользователя.

При отсутствии сигнала «Разрешение обращения» программа пользователя прерывается и вызывается операционная система(супервизор).

В режиме системы цепи защиты фактически отключается сигналом «система», формирующим сигнал разрешения.

Страничная адресация

При страничной организации адресации вся память делится на равные части определенного размера.

Страничный способ адресации не имеет никакого отношения к физической организации памяти системы. Этот способ просто используется для указания адреса с помощью меньшего количества разрядов, чем это имеет место при однокомпонентных способах адресации. При страничном способе адресации команда содержит только адреса на странице (рисунок 7.14 в, г, д); номер страницы определяется несколькими путями с помощью команды, формирующий абсолютный адрес:

- адресация на базовой странице. Номеру страницы присваивается нулевое значение, т.е. абсолютный адрес формируется из нулевой (базовой) страницы памяти;

-адресация с использованием текущей страницы. Номер страницы устанавливается равным значениям старших разрядов счетчика команд, при этом адрес располагается на той странице, где находится выполняемая команда (на текущей странице);

-адресация с использованием регистра страницы. Номер страницы определяется по содержимому регистра страниц, в которой предварительно программным путем загружается требуемый номер страницы.

Хотя при этом способе адресации уменьшается длина адреса для многих команд, все-таки иногда необходимо указывать полный адрес. Следовательно, ЭВМ, имеющие страничную адресацию, должны располагать и другими способами адресации, такими, как абсолютная и косвенная регистровая адресация.

Страничную адресацию использует ЭВМ 6809, MCS-48 (память данных), MCS-48 (память команд) и др.

На представленном рисунке 1.5 16-разрядный абсолютный адрес может быть поделен на два элемента: 8-разрядный номер страницы указывает какая из 256 страниц содержит требуемый байт информации; 8-разрядный адрес на странице задает местоположение байта в пределах 256-байтовой страницы.

A)

00FF

01FF

0200

02FF

FF00

FFFF

Б) 15 8 7 0

В)

ОП

Г) Счетчик команд (РС) ОП

Исполнительный адрес

Д)

Регистр страниц ОП

Рисунок 1.5 – Формирование страничных адресов

где: А) – деление адресного пространства;

Б) – адресное значение;

В) – адресация с использованием базовой страницы;

Г) - адресация с использованием текущей страницы;

Д) - адресация с использованием регистра страницы.

Аппаратура страничной организации памяти может быть реализована по следующему принципу.

Разделим (мысленно) всю главную память на страницы, т.е. на равные части определенного размера. Например, размер страницы в разных ЭВМ принимался равным от 512 до 4096 слов, а количество страниц в главной памяти от 16 до 64 или даже от 128 и более. Тогда адрес любой ячейки памяти можно представить себе состоящим из двух частей: старшие разряды – номер страницы, младшие – номер ячейки в странице («номер строки»). Это относится как к тем адресам, которые записаны в тексте программы на машинном языке (математические или виртуальные адреса), так и к тем исполнительным адресам, которые передаются запоминающим устройствам при обращении к ним (физические адреса). Формирование исполнительных адресов состоит в подмене номера страницы в математическом адресе (математического номера страницы) некоторым другим, физическим номером страницы. Эта подмена выполняется при каждом обращении к памяти аппаратурой формирования исполнительных адресов, а соответствие между математическими и физическими адресами на определенный интервал времени устанавливает операционная система.

Как увидим далее, такое построение позволяет организовать перемещение и уплотнение информации в памяти, защиту памяти и решить другие задачи. Однако все эти задачи будут решаться с дискретностью в одну страницу. Например, при уплотнении информации система сумеет использовать «окна» в памяти, только кратные по размеру странице, при организации защиты памяти для всей страницы будет устанавливаться одинаковый статус и т.д.

Известны три основных варианта построения аппаратуры, обеспечивающей страничную организацию памяти. Эти варианты представлены на рис. 1.6.

Во всех вариантах существенную часть аппаратуры составляет ЗУ из так называемых дескрипторных регистров, в которых ОС заносит описание (description) соответствия между физическими и математическими номерами страниц. Варианты различаются, прежде всего формой, в которой представлено это описание. Занесение информации в дескриптарные регистры (ДР) является привелигированной операцией ОС.

1-й вариант (рисунок 1.6а) построен так, что количество дескрипторных регистров равно максимально возможному для одной программы количеству страниц. При этом предполагается, что если это количество равно N, то в качестве математических номеров страниц будут использоваться числа 1,2,3, …, N или 0,1,…(N-1). Математический номер страницы в составе адреса, имеющегося в инструкции, представляет собой фактически номер дескрипторного регистра (ДР), который должен быть использован при формировании исполнительного адреса.

Информация, хранящаяся в этом варианте в ДР – это физические номера страниц, соответствующие заданным неявно (в виде номеров ДР математическим адресам).

При формировании адреса производится дешифрирование математического номера страницы, и на одном из выходов дешифраторасигналов управления появляется сигнал. Этот сигнал открывает группу вентилей (&), пропускающую на своем выходе информацию из того ДР, номер которой соответствует математическому номеру страницы. Выходы вентилей объединяются в сборку (шины), на выходе которой проходит информация из выбранного ДР, т.е. физический номер страницы, соответствующий математическому номеру страницы, содержащемуся в адресе, который был прочитан в составе команды.сигналов управления появляется сигнал. Этот сигнал открывает группу вентилей (&), пропускающую на своем выходе информацию из того ДР, номер которой соответствует математическому номеру страницы. Выходы вентилей объединяются в сборку (шины), на выходе которой проходит информация из выбранного ДР, т.е. физический номер страницы, соответствующий математическому номеру страницы, содержащемуся в адресе, который был прочитан в составе команды.

Второй вариант (рис. 1.6б) отличается тем, что каждый из ДР закреплен не за математическим номером страницы, а, наоборот, за определенной физической страницей. Информация, которую ОС засылает в дескрипторы, в этом варианте представляет собой математические адреса страниц: в ДР, соответствующий определенной физической странице, записывается математический номер, по которому программа будет обращаться к этой странице.

Выходная информация из ДР поступает на входы схем совпадения, каждая из которых соединена со своим ДР. На другие входы схем совпадения поступает математический номер страницы. Обнаруживая совпадение математического номера страницы с содержанием своего дескриптора, схема совпадения формирует сигнал = (равно).

Сигналы с выходов схем совпадения, представляющие собой как бы физический номер страницы, записанные в единичной форме, поступают на вход шифратора, который кодирует этот номер в виде двоичного числа.

3-ий вариант аппаратной реализации страничной памяти представлен на рисунке 1.6в.

Каждый из ДР состоит из двух частей. В тех частях регистров, которые на рисунке расположены слева, записываются математические адреса страниц, в правых – соответствующие им физические адреса страниц.

С левой частью каждого из ДР связана схема совпадения, так же как на рисунке 1.6б. При совпадении математического номера страницы в адресе обращения к памяти с математическим номером страницы, записанным в левой части некоторого ДР, соответствующая СП вырабатывает сигнал = (равно). Этот сигнал управляет группой вентилей, соединенной с правой частью того же ДР аналогично тому, как группы вентилей соединены с ДР-ми в схеме рисунка 1.6а. Далее как на рисунке 1.6а, выходы группвентилей объединяются сборкой, на выход которой проходит физический номер страницы, соответствующий выбираемому математическому номеру страницы.

| Математический номер страницы

|

Математический адрес

| Дешифратор сигналов управления

|

.

.

.

.

| Физический номер страницы

|

Физический адрес операнда

Рисунок 1.6а – Варианты страничной адресации

Математический адрес

| Математический номер страницы

|

| Физический номер страницы

|

Рисунок 1.6б – Варианты страничной адресации

| Математический номер страницы

|

Мат. ном.стр.Физ. Ном. Строки

Рисунок 1.6в – Варианты страничной адресации

Сравнивая между собой приведенные три основных варианта, можно заметить одно принципиальное отличие 1-го варианта от 2-го и 3-го. Совокупность ДР в любом случае можно рассматривать как некоторое ЗУ специального назначения. Однако только в первом варианте оно является обычным ЗУ с адресной выборкой. Математический номер страницы в этом варианте построения аппаратуры, используется как адрес ячейки в специальной памяти, где хранится соответствующий физический номер страницы. Во 2-м и 3-м вариантах мы имеем дело фактически с ЗУ с ассоциативной выборкой.

Поэтому на основе 1-го варианта аппаратуры страничной организации памяти возможно создание такой упрощенной модификации, в которой роль ДР играл бы отведенной для этой цели участок главной памяти (рисунок 1.6г).

Математический адрес

| Регистр адреса начала дескрипторного массива

|

| Математическийномер страницы

|

(Физический адрес дескриптора)

(содержимое ячейки дескриптора)

| Физический номер страницы

|

Физический адрес

Рисунок 1.6г – Варианты страничной адресации

Аппаратура ДР заменена одним регистром, в который ОС засылает начальный физический адрес массива главной памяти, отведенного для дескрипторов. Этот массив заполняется ОС и тоже защищен от изменения в нем программами пользователей.

Формирование исполнительного адреса состоит в том, что к начальному физическому адресу дескрипторного массива добавляется как бы смещение – математический номер страницы, содержащийся в математическом адресе. В результате на выходе сумматора образуется физический адрес той ячейки ОП, в которой хранится физический номер страницы, соответствующий данному математическому номеру. По этому адресу производится вспомогательное обращение к памяти и прочитывается физический номер страницы. Далее к нему присоединяется номер строки из исходного (математического адреса).

, Рг защ

, Рг защ

указывают соответственно верхнюю нижнюю границы i- й области памяти, отведенной программе пользователя.

указывают соответственно верхнюю нижнюю границы i- й области памяти, отведенной программе пользователя. связано по одной схеме сравнения, Сх. ср. i и Сх.ср.

связано по одной схеме сравнения, Сх. ср. i и Сх.ср.  , выполняющие сравнение информации, находящейся в регистрах

, выполняющие сравнение информации, находящейся в регистрах  с исполнительным адресом, по которому предполагается выполнить обращение к памяти. Если величина, находящаяся в

с исполнительным адресом, по которому предполагается выполнить обращение к памяти. Если величина, находящаяся в  меньше или равна исполнительному адресу, то схема Сх.ср. i формирует сигнал ≤. Аналогичным образом, если величина, находящаяся в регистре

меньше или равна исполнительному адресу, то схема Сх.ср. i формирует сигнал ≤. Аналогичным образом, если величина, находящаяся в регистре  адресу, схемой Сх.ср.

адресу, схемой Сх.ср.  . Наличие обоих этих сигналов одновременно свидетельствует о принадлежности исполнительного адреса i -й области, отведённый пользователю.

. Наличие обоих этих сигналов одновременно свидетельствует о принадлежности исполнительного адреса i -й области, отведённый пользователю. и Сх.ср.

и Сх.ср.  также появился сигнал ≥.

также появился сигнал ≥.