ЦЕЛИ И ЗАДАЧИ ДИСЦИПЛИНЫ

1.1. Цели изучения дисциплины

Дисциплина «Схемотехника, часть 2: Основы цифровой схемотехники» является специальной базовой дисциплиной, подготавливающей студентов к изучению других специальных и профилирующих дисциплин специальности. 160905, и имеет целью изучения принципов и методов анализа и синтеза устройств формирования, преобразования, хранения и индикации цифровых сообщений и сигналов.

1.2. Задачи изучения дисциплины

1.2.1.Иметь представление: об основных свойствах цифровых сообщений и сигналов, различных методов формирования, преобразования, хранения и индикации этих сигналов, особенностях материального отображения цифровых сигналов, технологии производства цифровых ИМС различного типа, методах и принципах выбора оптимальных решений цифровой схемотехники, временных и энергетических свойствах ИМС и узлов на них.

1.2.2.Знать: основные способы аналитического и материального представления цифровых сообщений и сигналов, сущность математических и логических действий над цифровыми сигналами и их моделями, основы теории логических функций и алгебры логики, номенклатуру, основные свойства, методы синтеза и анализа цифровых узлов комбинационного и последовательного типа, свойства и способы применения арифметико-логических устройств и устройств запоминания информации, методы анализа и синтеза устройств синхронизации, тактирования и управления цифровыми ИМС и узлами, основные принципы синтеза цифровых узлов на промышленных ИМС.

1.2.3.Уметь: осуществлять аналитическое и материальное представление цифровых сообщений и сигналов, проводить математические и логические действия над цифровыми сигналами, проводить расчет логических функций, использовать законы алгебры логики в этих расчетах, номенклатуру, технико-эксплуатационные свойства и особенности промышленных ИМС комбинационного и последовательного типа, применять арифметико-логические устройства и устройства запоминания информации, проводить анализ, синтез и электрический расчет устройств синхронизации, тактирования и управления цифровыми ИМС и узлами, читать и синтезировать структурно-логические и принципиальные схемы на основе и с применением промышленных ИМС различных технологий.

1.2.4.Иметь опыт: анализа и синтеза цифровых сигналов, синтеза цифровых устройств с использованием теории логических функций и алгебры логики, выбора и применения цифровых ИМС промышленного производства, чтения и синтеза структурно-логических и принципиальных схем на основе ИМС, расчета, анализа и синтеза устройств синхронизации, тактирования и управления цифровыми ИМС и узлами на них.

РЕКОМЕНДУЕМАЯ ЛИТЕРАТУРА:

1. Основная литература

1.Бабаев В.Г. Основы цифровой схемотехники. Часть 1. МГТУ ГА, 1995.

2.Бабаев В.Г. Основы цифровой схемотехники. Часть 2. МГТУ ГА, 1996.

3.Бабаев В.Г. Основы цифровой схемотехники. Часть 3. МГТУ ГА, 1997.

4.Бабаев В.Г., Зыков В.П., Глушнев В.Г. Схемотехника импульсных и цифровых устройств. М: Воздушный транспорт, 1998.

2. Учебно-методическая литература

5.Васильева Л.С. Методические указания по применению ИМС ТТЛ-типа. МГТУ ГА, 1995.

6.Бабаев В.Г. Основы цифровой схемотехники. Часть 4. МГТУ ГА, 1998.

7. Бабаев В.Г. Пособие к выполнению лабораторных работ по дисциплине ОЦСТ. Часть 1. МГТУ ГА, 1999.

8. Сосновский М.Ю. Пособие к выполнению лабораторных работ по дисциплине ОЦСТ. Часть 2. МГТУ ГА, 2000.

9.Бабаев В.Г. Пособие к выполнению курсовой работы по дисциплине «Схемотехника», часть 2. МГТУ ГА, 2003.

10.Бабаев В.Г. Схемотехника. Пособие по изучению дисциплины, часть 2. Для студентов 4 курса спец. 201300 заочного обучения. МГТУ ГА. 2003.

Лекция №1

1. ОБЩИЕ СВЕДЕНИЯ О ЦИФРОВЫХ СИГНАЛАХ (КОДАХ)

Понятие цифрового сигнала

ЦИФРОВЫМ СИГНАЛОМ называется цифровое сообщение, преобразованное в стандартную электромагнитную форму.

ИНФОРМАЦИЯ, представленная сочетанием символов (букв, цифр) или фонемой устной речи, называется СООБЩЕНИЕ. В свое очередь, сообщение, составленное только из цифровых символов, является ЦИФРОВЫМ СООБЩЕНИЕМ. Следовательно, цифровое сообщение представляется сочетанием только цифр, а комбинации цифр, в свою очередь, представляют собой любые иные символы или понятия – буквы, слове и фразы, действия над данными (сложение, деление, возведете числа в какую-либо степень и т.д.) из которых составляется сообщение.

С помощью цифровых символов и сообщений возможна передача любой информации – книг, рисунков графиков, музыки и изображения и т.д.

Ясно, что все это должно быть произведено с использованием каких-либо стандартов кодирования сообщения и символов, передающих информацию.

Для работы с цифровым сообщением в электронных цифровых устройствах эти сообщения необходимо сначала преобразовать в бинарную форму, используя только два символа «0» и «1», а затем в цифровой сигнал (в дальнейшем будем подразумевать «1» = I – логическое состояние, а не число).

Преобразование цифрового сообщения в цифровой сигнал называется КОДИРОВАНИЕМ СООБЩЕНИЙ. Поэтому цифровые сигналы называются иначе цифровыми кодами чисел.

Для получения сигнала из цифрового сообщения используются соглашения положительной, отрицательной или импульсной логики.

Рис. 1.1. Соглашение положительной логики

Соглашение положительной логики применяется на практике в большинстве интегральных микросхем (ИМС) транзисторно-транзисторной логики (ТТЛ - типа).

Напряжения более 2,4 В отображают логическую " 1 ", а напряжения менее 0,4 В отображают логический " 0 ". На рис. 1.2. показан цифровой сигнал, отображающий число 2616 = 0100110.

Рис. 1.2. Цифровой сигнал числа 2616

Цифровые сигналы можно условно разделить на две группы:

1) стандартные (типовые) сигналы: они отображают стандартные символы (буквы, цифры, арифметические или логические операции, знаки препинания и т.д.) и образуется с помощью стандартных цифровых кодов;

2) цифровые сигналы, отображающие количественную характеристику какого-либо процеcca: расстояние от самолета до аэропорта, высоту полета ЛА и т.д. Другими словами цифровые сигналы – текущие данные о каком-либо процессе в определенный момент времени.

Как правило, такие данные получают от различных датчиков, параметрами которых могут быть: время, длина, частота, фаза и т.д.

Для учета и дальнейшей обработки таких сигналов их необходимо преобразовать в цифровой код при помощи аналого-цифрового преобразователя (АЦП).

На вход АЦП подаётся аналоговый электрический сигнал, например, от бортового радиовысотомера (РВ). При поступлении на синхровход АЦП тактового импульса, на выходе АЦП формируется цифровой код, соответствующий напряжению сигнала (в данном случае – высота полета самолета в каждый момент времени).

Позиционные числа

Позиционным называется число, у которого весовой коэффициент любого разряда определяется его позицией (номером разряда).

Вес для целых чисел определяется:

Hi = qi-1,

где q – основная система счисления;

i – номер разряда числа (имеется ввиду наименьший значащий разряд (МЗР); i =1, а старший (СЗР) – номер i =n).

Для десятичных чисел q = 10; вес первого разряда H1 = 100, H2 = 101, Hn = 10n-1.

Для двоичных чисел q = 2; вес первого разряда H1 = 20, H2 = 21, Hn = 2n-1 и т.д.

Общая формула позиционного числа:

А =  ,

,

где n – число разрядов целой части; i = 1, 2,…n;

ai – цифры разрядов целой части;

m – число разрядов дробной части; j = 1, 2,…m;

aj - цифры разрядов дробной части.

Сокращенная запись числа А:

A = an ·an-1·an-2… a2·a1,·am·am-1·am-2…a2·a1.

Арифметические операции над двоичным числом

Умножение двоичных чисел

Умножение двоичных чисел производится по тому же правилу, что и умножение десятичных чисел. Учитывая, что в разрядах множителя записываются только цифры 0 или I, легко сформулировать правило умножения двоичных чисел:

1) Записываем множимое и множитель так, чтобы их разряды с одинаковым " весом " находились один под другим:

А = 10101,01 – множимое

х В = 10011,10 – множитель

………..

………..

2) Определяем число единиц в множителе и их местоположение.

3) Множимое переписываем справа – налево (его запятая игнорируется), нанимая с местоположения единицы множителя, и делаем это столько раз, сколько единиц в множителе.

4) Складываем арифметически полученные двоичные числа, их количество равно числу единиц множителя.

5) Местоположение запятой в произведении определяется суммой разрядов после запятой множимого и множителя.

Пример: 1101,01 = А

х 0101,01 = В

1101 01

1101 01

+ 110101

+ 110101

+ 110101

А х В = 1000101,10 01

переносы: 11111 1

Вычитание двоичных чисел

Вычитание легко представить как алгебраическое сложение:

А – В = А + (–В)

Следовательно, для осуществления алгебраического сложения необходимо ввести знаковые разряды: положительные числа имеют знаковый разряд " 0 ", отрицательные числа – знаковый разряд " 1 ". Кроме того, отрицательные числа представляются в обратном коде, для этого все разряды числа, кроме знакового, инвертируются: 0 заменяют на 1 и наоборот.

Пример: А = 10111,011

В прямом коде –A = 110111,011

В обратном коде – А = 101000,100

Деление двоичных чисел

Деление двоичных чисел производится по тому же правилу, что и деление десятичных чисел. Как известно, при делении десятичных чисел делается вычитание из одного десятичного числа другого с использованием правила «заема» единиц в соседних, более старших разрядах.

Пример: 99: 11 = 9 1100011: 1011 = 1001

– 1011

0001011

0001011

– 1011

– 1011

Преобразование целых чисел

Для преобразования целой части числа разделим левую и правую части полинома на основание q:

Ац/q = an qn-2 + an-1 qn-3 +…a2 q0 + a1/q.

Выполняя последовательно операцию деления на q, получим новое целое число и остаток от деления с цифрой разряда an-1.

#1 100:8 = 12:8 =1; Ответ: 100 = 1448.

4 4

#2 89:2 = 44:2 = 22:2 = 11:2 = 5:2 = 2:2 = 1:2; Ответ: 89:2 = 1011001

1 0 0 1 1 0 1

Для получения восьмеричного числа из двоичного числа нужно разбить его разряды на «триады»:

А = 010 011 101 011 = 23538.

А = 010 011 101 011 = 23538.

2 3 5 3

Для получения двоично-восьмеричного кода нужно каждую цифру восьмеричного числа заменить трёхразрядным двоичным числом:

23538 = 2·82 + 3·81 + 5·80 = 128 +24 + 1.

В шестнадцатеричных числах основание q = 16; алфавит включает числа 0÷9 и буквы A÷F (10÷15).

Получение шестнадцатеричных чисел из двоичных

A = 1101 1001 1110, 0001 0101 = D9E, 1516.

A = 1101 1001 1110, 0001 0101 = D9E, 1516.

D 9 E 1 5

Целую часть числа разбиваем на тетрады (четырех - разрядные числа), от запятой справа – налево, а дробную часть – тетрады, от запятой слева – направо. Полученные тетрады заменяем цифрами.

Типы цифровых устройств

Цифровое устройство (ЦУ) обеспечивает преобразование совокупности цифровых входных сигналов Х в выходные сигналы У. Для формирования цифровых выходных сигналов используются ЦУ двух типов:

1) ЦУ выходные сигналы, у которых в некоторый момент времени tn зависят только от совокупности (комбинации) сигналов Х, присутствующих на их входах в тот же момент времени tn, и не зависят от входных сигналов, поступающих в предшествующие моменты времени. Иными словами, ЦУ этого типа «не помнит» предыстории поступления сигналов на его входы. Такие ЦУ принято называть комбинационными или ЦА без памяти.

2) ЦУ, выходные сигналы у которых в момент времени tn определяются не только комбинациями входных сигналов Х, воздействующих в тот же момент времени tn, но и сигналами, поступающими на входы в предшествующие моменты времени. В составе таких ЦУ обязательно присутствуют элементы памяти, внутреннее состояние которых отражает предысторию поступления последовательности входных сигналов. Подобные ЦУ принято называть последовательностными или, конечными автоматами (ЦА с памятью).

К комбинационным ЦУ относят следующие: дешифраторы, шифраторы, мультиплексоры, схемы сравнения, преобразователи кодов, комбинационные полусумматоры и сумматоры.

Шифраторы

Шифратором называется устройство, обратное дешифратору по функции выполняемого преобразования. Полный шифратор имеет n выходов и m=2 входов (рис. 3.1).

Рис. 3.1.

Такой шифратор преобразует десятичные цифры 0, 1,..., 7 в трехразрядный двоичный код.

| Номер набора

| х7 х6 х5 х4 х3 х2 х1 х0

| у2 у1 у0

|

|

| 0 0 0 0 0 0 0 1

1 1

1 1

| 0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

|

На основе таблицы можно записать соответствующие ПФ для у2, у1, у0, а затем выполнить необходимые действия по их минимизации. Но в данном случае можно воспользоваться особенностью закона функционирования данного ЦА. Анализ таблицы показывает, что единицу в младшем разряде двоичного числа имеют нечетные десятичные цифры 1, 3, 5, 7, т.е. на выходной шине младшего разряда должна быть логическая единица, если она есть на соответствующих входных шинах с номерами строк 1, 3, 5 или 7. Поэтому входные шины с указанными номерами должны быть подключены к выходу младшего шифратора через ИЛЭ ИЛИ. Единицу во втором разряде двоичного числа имеют десятичные цифры 2, 3., 6 и 7. Входные шины с этими номерами подключаются через второй ИЛЭ ИЛИ ко второму выходу шифратора, на котором формируется второй разряд двоичного кода.

Единицу в третьем разряде двоичного кода имеют десятичные цифры 4, 5, 6 и 7, входные шины с этими номерами должны быть соединены через ИЛЭ ИЛИ с выходом третьего разряда шифратора. Для кода нулевого набора сигнала на входы ИЛЭ ИЛИ не подаются. Кроме того, в каждый момент времени должен подаваться сигнал только по одной входной шине.

Дешифраторы

Дешифратором (ДС) называется комбинационное логическое устройство для обнаружения и регистрации определенных кодовых комбинаций, поступающих на его вход.

Если логику устройства описывают n двоичных переменных, то это устройство может иметь  различных выходных состояний по числу возможных наборов из этих переменных и их отрицаний. Например, при двух входных переменных Х0 и Х1, когда n=2, дешифратор формирует

различных выходных состояний по числу возможных наборов из этих переменных и их отрицаний. Например, при двух входных переменных Х0 и Х1, когда n=2, дешифратор формирует  выходных сигнала у0, у1, у2, у3. Его условное графическое обозначение имеет вид рис. 3.2. опознанная комбинация переменных вызывает сигнал истинности уi=1 на той выходной шине дешифратора, номер которой совпадает с действующими на входе двоичным числом, т.е. с номером набора переменных.

выходных сигнала у0, у1, у2, у3. Его условное графическое обозначение имеет вид рис. 3.2. опознанная комбинация переменных вызывает сигнал истинности уi=1 на той выходной шине дешифратора, номер которой совпадает с действующими на входе двоичным числом, т.е. с номером набора переменных.

Рис. 3.2.

Дешифраторы могут быть полными и неполными. Полный дешифратор служит для обнаружения всех m возможных наборов, а неполный дешифратор обнаруживает m<2 входных комбинаций, требуемых по условию задачи.

Различают одноступенчатые и многоступенчатые дешифраторы. Различные схемы дешифраторов сравнивают по двум основным показателям:

1) времени задержки сигнала tзад.;

2) аппаратурным затратам (количеству корпусов интегральных схем).

Одноступенчатый дешифратор

Таблица истинности приведенного на рис. 3.2. дешифратора имеет вид:

| Номер

набора

| Х1

| Х0

| У0

| У1

| У2

| У3

|

|

|

|

|

|

|

|

|

Каждый выходной сигнал  как ПФ n переменных может принимать 2n значений, из которых только одно значение истинно (равно 1) и соответствует номеру набора входных переменных.

как ПФ n переменных может принимать 2n значений, из которых только одно значение истинно (равно 1) и соответствует номеру набора входных переменных.

В одноступенчатых ДС каждая из ПФ  , описывающих его работу, реализуется независимо, отдельной логической схемой типа И.

, описывающих его работу, реализуется независимо, отдельной логической схемой типа И.

Например, полный дешифратор двухразрядных чисел, согласно рис. 3.2, описывают следующие четыре ПФ, записанные в СДНФ.

.

.

На рис. 3.3 приведена функциональная схема этого ДС, выполненная на ЛЭ типа И и с двумя входами каждая. Такой дешифратор называют также линейным.

Рис. 3.3. Рис. 3.4. а

Его можно реализовать также на элементах И-НЕ. При этом на его выходах получаем не сами функции уi, а их версии, т.е. все невыбранные выходы находятся в состоянии 1, а один выбранный выход – в состоянии 0. В этом случае при условном изображении дешифратора (рис. 3.4, б) его выходы нужно помечать символами инверсии.

Рис. 3.4. б

В выражениях, связывающих входы и выходы дешифратора, участвуют не только сами входные переменные, но и их инверсии. Соответственно на входы элементов нужно подавать как прямые, так и инверсные значения входных переменных. Поэтому либо входы дешифратора необходимо выполнять парафазными, либо инвертировать сигналы внутри дешифратора. Поэтому целесообразно на входе дешифратора включать буферные элементы (рис. 3.4, а), позволяющие уменьшить нагрузку дешифратора на источник входного сигнала.

Дешифратор, как любая многовыходная комбинационная логическая схема, может иметь различную задержку в различных путях прохождения сигналов со входа на выход. При этом при применении значения входных переменных правильные сигналы на выходах дешифратора устанавливаются не сразу, и могут появиться ложные выбросы. Поэтому в дешифраторе желательно иметь средства стробирования выходного сигнала. Для этого элементы И-НЕ выполняют с числом входов, на единицу большим разрядности дешифрируемого кода, и на дополнительный вход подается стробирующий сигнал С (рис. 3.4, а). Учитывая, что этот сигнал подводится к большому числу ЛЭ, на входе дешифратор обычно ставится дополнительный элемент (инвертор), делающий вход стробирования инверсным (рис. 3.4, б).

Преимущество одноступенчатых ДС – минимальная задержка сигнала, равная задержке в одном ЛЭ.

Многоступенчатый дешифратор

Одноступенчатые ДС при n>4 требуют для реализации большого числа ЛЭ И. Этот недостаток ослабляется в многоступенчатых ДС. На практике широкое применение находит, например, двухступенчатый дешифратор. Рассмотрим принцип построения такого дешифратора на примере ДС с 4-мя входами и 16-ю выходами.

Разобьем входные переменные Х3, Х2, Х1, Х0 на две группы по две переменные в каждой: Х3, Х2 и Х1, Х0. Каждую пару переменных используем в качестве входных переменных отдельного одноступенчатого дешифратора на четыре выхода, как показано на рис. 3.5.

Рис. 3.5.

Выходные переменные одноступенчатых дешифраторов определяются следующими логическими выражениями:

.

.

Эти дешифраторы выполняют функции первой ступени дешифратора.

Выходные переменные у0,...,у15 дешифратора можно представить логическими выражениями, используя в них в качестве аргументов выходные переменные

и

и  одноступенчатых дешифраторов:

одноступенчатых дешифраторов:

;

;

;

;

.......................................

.

.

Эти логические операции И выполняются в отдельном дешифраторе второй ступени, состоящим их двухвходовых ЛЭ.

Недостатком многоступенчатых дешифраторов является большее время задержки сигналов, поскольку они должны проходить через ЛЭ всех ступеней.

Мультиплексоры

В цифровых устройствах бывает необходимо в разные моменты времени подключать к одной линии (назовем ее выходной) одну из нескольких входных линий. Такая операция коммутации каналов называется мультиплексированием, а устройство, реализующее эту операцию, называется мультиплексором. Выбор входной (информационной) линии осуществляется путем подачи ее номера в виде двоичного кода на управляющие (адресные) входы мультиплексора, коммутирующего 2n линии, как показано на рис. 3.6.

Рис. 3.6.

На входы А0, А1 подается адрес источника информации. Так, например, при подаче кода 00 подключается линия D0, при подаче кода 01 – линия D1 и т.д.

Здесь V – вход синхронизации. ПФ, описывающая работу такого мультиплексора, имеет вид

.

.

Из данного выражения видно, что для каждого входа D коммутации сигналов адреса в мультиплексоре такие же, как и в дешифраторе. Следовательно, составной частью мультиплексора является дешифратор. Функциональная схема мультиплексора с четырьмя информационными входами D приведена на рис. 3.7.

Рис. 3.7.

Демультиплексоры

Демультиплексоры предназначены для коммутации одного информационного входного сигнала на 2m входов, где m–число адресных входов, т.е. демультиплексоры выполняют функцию, обратную мультиплексорам.

Условное графическое обозначение демультиплексора с четырьмя информационными выходами представлено на рис. 3.8.

Рис. 3.8.

Переключательные функции выходных сигналов такого демультиплексора аналогичны выражениям, определяющим формирование выходных сигналов дешифратора, использующего синхронизацию по входу D:

;

;  ;

;  ;

;  .

.

Поэтому в качестве демультиплексора можно применять дешифратор, в котором информационный входной сигнал подан на вход синхронизации.

Сумматоры

Одноразрядный полусумматор

При сложении младших разрядов  и

и  двух чисел А и В цифра переноса

двух чисел А и В цифра переноса  в этот разряд всегда равна нулю. Поэтому сумматор, используемый в этом разряде, может иметь всего два входа.

в этот разряд всегда равна нулю. Поэтому сумматор, используемый в этом разряде, может иметь всего два входа.

Сумматор такого типа называется полусумматором, он обозначается, как показано на рис. 3.10, а функционирует в соответствии с таблицей истинности, представленной в табл. 3.2. Из неё легко получить ПФ в СДНФ:

Рис. 3.10.

Таблица 3.2.

Одноразрядный сумматор

Сумматором называется логическое устройство, выполняющее операцию арифметического сложения двух чисел.

Наиболее широко используются комбинационные сумматоры, которые выполняются в виде комбинационных схем (без элементов памяти).

Сложение двух чисел  и

и  обычно выполняется поразрядно одноразрядным сумматором. При этом сумматор складывает цифры

обычно выполняется поразрядно одноразрядным сумматором. При этом сумматор складывает цифры  и

и  i-го разряда слагаемых, а также цифру переноса

i-го разряда слагаемых, а также цифру переноса  из младшего (i-1)-го разряда. В результате получится цифра

из младшего (i-1)-го разряда. В результате получится цифра  i-го разряда суммы и цифра переноса

i-го разряда суммы и цифра переноса  в следующий (i +1) – й разряд.

в следующий (i +1) – й разряд.

Отсюда ясно, что одноразрядный сумматор имеет три входа

и два выхода

и обозначается, как показано на рис. 3.11.

Рис. 3.11.

Закон функционирования одноразрядного сумматора описывается таблицей истинности, которая отражает правила сложения трёх двоичных чисел (табл.1). На основе табл. 3.1. составим ПФ суммы  и переноса

и переноса  в СДНФ.

в СДНФ.

(3.3)

(3.3)

(3.4)

(3.4)

Выражения (2) минимизируется путём добавления двух слагаемых вида  и попарного склеивания соседних слагаемых

и попарного склеивания соседних слагаемых

(3.5)

(3.5)

На рис. 3.12 приведена схема сумматора, реализованная на ЛЭ типа И, ИЛИ по выражениям (3.3), (3.5).

Рис. 3.12.

Для обработки многоразрядных чисел объединяется соответствующее число одноразрядных сумматоров. При этом отдельные разряды обрабатываемых чисел А и В подаются на входы  и

и  . На вход

. На вход  подаётся перенос из предыдущего, более младшего разряда. Формируемый в данном разряде перенос

подаётся перенос из предыдущего, более младшего разряда. Формируемый в данном разряде перенос  передаётся в следующий, более старший разряд (рис. 3.13.).

передаётся в следующий, более старший разряд (рис. 3.13.).

Рис. 3.13 Рис. 3.14

Время выполнения операции в сумматоре, построенном таким образом, существенно больше времени сложения в одноразрядном сумматоре. Действительно, сигнал переноса  только тогда может принять правильное значение, когда перед этим будет установлено правильное значение

только тогда может принять правильное значение, когда перед этим будет установлено правильное значение  .

.

Такой порядок выполнения операции называется последовательным переносом. Чтобы уменьшить время, необходимое для сложения многоразрядных чисел, можно использовать схему переноса, в которой все сигналы переноса вычисляются параллельно непосредственно по значениям входных переменных. Полагая, что входная переменная с полного одноразрядного сумматора, работающего в i-м разряде многоразрядного сумматора, используется в качестве сигнала переноса из предыдущего разряда, т.е.  в соответствии с (3.5) выражение для сигнала переноса

в соответствии с (3.5) выражение для сигнала переноса  , формируемого в этом разряде, представим в виде:

, формируемого в этом разряде, представим в виде:

(3.6)

(3.6)

где  – функции входных переменных

– функции входных переменных  , называемые функцией генерации переноса

, называемые функцией генерации переноса  и функцией распространения переноса

и функцией распространения переноса  .

.

Важно, что значения  и

и  не зависят от

не зависят от  , т.е. могут быть вычислены с минимальной задержкой. Функция распространения переноса

, т.е. могут быть вычислены с минимальной задержкой. Функция распространения переноса  при

при  может принимать произвольное значение, поскольку значение

может принимать произвольное значение, поскольку значение  обеспечивается первым членом выражения (3.6) независимо от значения

обеспечивается первым членом выражения (3.6) независимо от значения  .

.

Пользуясь выражением (3.6), можно вывести следующие формулы для вычисления сигналов переноса:

Устройство, реализующее указанные функции в параллельной форме, называют схемой ускоренного переноса. На функциональных схемах его обычно обозначают символом GRP.

Схема четырёхразрядной секции сумматора с параллельным переносом и её условное обозначение показаны соответственно на рис. 3.15 а и рис. 3.15 б.

а) б)

Рис. 3.15.

Обратите внимание на изменение обозначения одноразрядных секций, вызванное тем, что в данном случае входы одноразрядного сумматора по отношению к выходам G и D не равноценны. Усложнение схемы такой секции окупается существенным повышением быстродействия, поскольку в ней значения выходных сигналов старших и младших разрядов формируются одновременно.

Лекция №4

ТРИГГЕРЫ

В импульсной и цифровой технике широко используются функциональные узлы, способные сохранять двоичную информацию (состояния «0», «1») после окончания действия входных импульсов. Такие функциональные узлы называют триггерами.

В импульсной и цифровой технике широко используются функциональные узлы, способные сохранять двоичную информацию (состояния «0», «1») после окончания действия входных импульсов. Такие функциональные узлы называют триггерами.

В интегральной микросхемотехнике триггеры выполняют либо на основе логических интегральных элементов, либо как завершенный функциональный элемент в виде микросхемы.

Интегральные триггеры характеризуются большим разнообразием. Их отличают функциональный признак, определяющий поведение триггера при воздействии сигнала управления, а также используемый способ управления. По функциональному признаку различают триггеры типов R-S, D, T, J-K и др. По способу управления триггеры подразделяют на асинхронные и тактируемые. В асинхронных триггерах переключение из одного состояния в другое осуществляется непосредственно с поступлением сигнала на информационный вход. В тактируемых триггерах помимо информационных входов имеется вход тактовых импульсов. Их переключение производится только при наличии разрешающего, тактирующего импульса.

Триггеры применяют при построении более сложных функциональных устройств: счетчиков импульсов, регистров и т. д.

4.1.1. R-S -триггеры. В зависимости от способа управления различают асинхронные и тактируемые R-S -триггеры.

Асинхронные R-S- триггеры являются простейшими, однако они получили широкое распространение в импульсной и цифровой технике. В частности, они служат основой триггеров других типов и требуют для своего построения два двухвходовых логических элемента типа И – НЕ или ИЛИ – НЕ.

| tn

| tn + 1

|

S S

|  R R

| Q n + 1

|

|

|

|

|

|

|

|

|

|

|

| Q n

|

|

|

| X

|

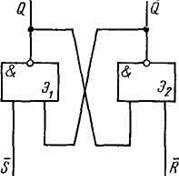

На рис. 4.1. приведена структурная схема асинхронного триггера на логических элементах И – НЕ. Схема имеет два выхода: Q – прямой, Q – инверсный.

На рис. 4.1. приведена структурная схема асинхронного триггера на логических элементах И – НЕ. Схема имеет два выхода: Q – прямой, Q – инверсный.

Рис. 4.1.

Асинхронный R-S -триггер, как и триггер любого другого типа, характеризуется двумя состояниями: логической «1» и логического «0». Состоянию логической «1» соответствует Q= 1, Q = 0; состоянию логического «0» – Q = 0, Q= 1.

Асинхронный R-S -триггер, как и триггер любого другого типа, характеризуется двумя состояниями: логической «1» и логического «0». Состоянию логической «1» соответствует Q= 1, Q = 0; состоянию логического «0» – Q = 0, Q= 1.

По информационному входу S производится установка триггера в состояние логической «1», а по информационному входу R – установка (перевод) триггера в исходное состояние логического «0». Этому соответствуют сокращенные обозначения входов и название триггера: S – set (установка), R – reset (возвращение в исходное состояние).

Принцип действия триггера определяется поведением в нем элементов И – НЕ. Он иллюстрируется таблицей переходов триггера (рис. 4.1 б), где указаны значения входных сигналов S и R внекоторый момент времени t nи состояние триггера (по значению его

,

, ………..

……….. 1101 01

1101 01 + 110101

+ 110101 0001011

0001011 – 1011

– 1011

А = 010 011 101 011 = 23538.

А = 010 011 101 011 = 23538.

1

1

1

1

различных выходных состояний по числу возможных наборов из этих переменных и их отрицаний. Например, при двух входных переменных Х0 и Х1, когда n=2, дешифратор формирует

различных выходных состояний по числу возможных наборов из этих переменных и их отрицаний. Например, при двух входных переменных Х0 и Х1, когда n=2, дешифратор формирует  выходных сигнала у0, у1, у2, у3. Его условное графическое обозначение имеет вид рис. 3.2. опознанная комбинация переменных вызывает сигнал истинности уi=1 на той выходной шине дешифратора, номер которой совпадает с действующими на входе двоичным числом, т.е. с номером набора переменных.

выходных сигнала у0, у1, у2, у3. Его условное графическое обозначение имеет вид рис. 3.2. опознанная комбинация переменных вызывает сигнал истинности уi=1 на той выходной шине дешифратора, номер которой совпадает с действующими на входе двоичным числом, т.е. с номером набора переменных.

как ПФ n переменных может принимать 2n значений, из которых только одно значение истинно (равно 1) и соответствует номеру набора входных переменных.

как ПФ n переменных может принимать 2n значений, из которых только одно значение истинно (равно 1) и соответствует номеру набора входных переменных.

.

.

.

.

и

и  одноступенчатых дешифраторов:

одноступенчатых дешифраторов: ;

; ;

; .

.

.

.

;

;  ;

;  ;

;  .

. и

и  двух чисел А и В цифра переноса

двух чисел А и В цифра переноса  в этот разряд всегда равна нулю. Поэтому сумматор, используемый в этом разряде, может иметь всего два входа.

в этот разряд всегда равна нулю. Поэтому сумматор, используемый в этом разряде, может иметь всего два входа.

и

и  обычно выполняется поразрядно одноразрядным сумматором. При этом сумматор складывает цифры

обычно выполняется поразрядно одноразрядным сумматором. При этом сумматор складывает цифры  из младшего (i-1)-го разряда. В результате получится цифра

из младшего (i-1)-го разряда. В результате получится цифра  i-го разряда суммы и цифра переноса

i-го разряда суммы и цифра переноса  в следующий (i +1) – й разряд.

в следующий (i +1) – й разряд.

и два выхода

и два выхода  и обозначается, как показано на рис. 3.11.

и обозначается, как показано на рис. 3.11.

в СДНФ.

в СДНФ. (3.3)

(3.3) (3.4)

(3.4) и попарного склеивания соседних слагаемых

и попарного склеивания соседних слагаемых (3.5)

(3.5)

в соответствии с (3.5) выражение для сигнала переноса

в соответствии с (3.5) выражение для сигнала переноса  (3.6)

(3.6) – функции входных переменных

– функции входных переменных  , называемые функцией генерации переноса

, называемые функцией генерации переноса  и функцией распространения переноса

и функцией распространения переноса  .

. , т.е. могут быть вычислены с минимальной задержкой. Функция распространения переноса

, т.е. могут быть вычислены с минимальной задержкой. Функция распространения переноса  при

при  может принимать произвольное значение, поскольку значение

может принимать произвольное значение, поскольку значение  обеспечивается первым членом выражения (3.6) независимо от значения

обеспечивается первым членом выражения (3.6) независимо от значения

В импульсной и цифровой технике широко используются функциональные узлы, способные сохранять двоичную информацию (состояния «0», «1») после окончания действия входных импульсов. Такие функциональные узлы называют триггерами.

В импульсной и цифровой технике широко используются функциональные узлы, способные сохранять двоичную информацию (состояния «0», «1») после окончания действия входных импульсов. Такие функциональные узлы называют триггерами. S

S

R

R

На рис. 4.1. приведена структурная схема асинхронного триггера на логических элементах И – НЕ. Схема имеет два выхода: Q – прямой, Q – инверсный.

На рис. 4.1. приведена структурная схема асинхронного триггера на логических элементах И – НЕ. Схема имеет два выхода: Q – прямой, Q – инверсный.

Асинхронный R-S -триггер, как и триггер любого другого типа, характеризуется двумя состояниями: логической «1» и логического «0». Состоянию логической «1» соответствует Q= 1, Q = 0; состоянию логического «0» – Q = 0, Q= 1.

Асинхронный R-S -триггер, как и триггер любого другого типа, характеризуется двумя состояниями: логической «1» и логического «0». Состоянию логической «1» соответствует Q= 1, Q = 0; состоянию логического «0» – Q = 0, Q= 1.