ОПЕРАТОР IF. <<ß-------------Ветвление

Этот условный оператор в зависимости от заданных условий выполняет цепочки последовательных операторов, причем от условия зависит, которая из цепочек операторов выполняется. Упрощенный синтаксис оператора:

\оператор if\:: = if \условие 1\ then

{\последовательный оператор 1\}

[ { elsif \условие 2\ then

{\последовательный оператор 2\}]

[ else

{\последовательный оператор 3\}]

end if;

Каждое из условий должно быть выражением, вычисляющим результат булевского типа. При выполнении этого оператора условия проверяются последовательно друг за другом пока результат условия не будет true. Тогда выполняется соответствующая этому условию цепочка операторов и выполнение данного оператора if прекращается.

ОПЕРАТОР CASE. <<ß---------Селектор

Этот оператор разрешает выполнение одной из цепочек последовательных операторов в зависимости от значения выражения селектора. Его упрощенный синтаксис:

\оператор case\:: = case \простое выражение\ is

when \альтернативы\ => {\последовательный оператор\}

{ when \альтернативы\ => {\последовательный оператор\}}

end case;

\альтернативы\:= \альтернативa\{ | \альтернатива\}

В выражении селектора \простое выражение\ должен вычисляться целый результат или значение перечисляемого или регулярного типа. Это должно быть простое выражение, а не, например, конкатенация. Каждая из альтернатив \альтернатива\ должна быть такого же типа, что и \выражение\ и представлена статическим выражением или диапазоном, например, 0 to 4.

Никакие два значения, получаемые из выражений альтернатив, не должны быть равны друг другу, т.е. множества альтернатив не перекрываются. Последней альтернативой может быть ключевое слово others, которое указывает на не перечисленные альтернативы. Если слово others не применяется, то в альтернативах должны быть перечислены все возможные значения, принимаемые в селекторе \выражение\.

Примероператора case:

variable sel, a: integer 0 to 9;

.............

case sel is

when 0 => a <= 0;

when 1|2|3 => a <= 1;

when 4 to 7 => a <= 2;

when others => a <= 3;

Endcase.

Объявление компонента в VHDL. Включение компонента в схему.

Объявление компонента определяет интерфейс и модели на VHDL (Entity или Architecture). В момент моделирования должны существовать объявления Entity и Architecture для компонентов, которые не только объявлены, но и установлены в схему. Это позволяет задавать объявления библиотечных элементов, а реальные их описания (объявления Entity и Architecture) задавать по мере использования этих элементов.

Объявление компонента записывается в виде: Componentname [port (port_list);] endcomponent.

Модели задержки в языке VHDL. Примеры применения.

Объект с задержкой можно представить состоящим из двух: идеального элемента и элемента задержки:

В языке VHDL встроены две модели задержки: инерционная (inertial) и транспортная (transport).

Инерциальная модель предполагает, что элемент не реагирует на сигналы, длительность которых меньше порога, равного времени задержки элемента.

Транспортная модель не имеет такого ограничения.

Инерциальная модель по умолчанию встроена воператор назначения сигнала языка VHDL. Например, оператор назначения

Y<= inertialXIand Х2 after 10ns;

описывает работу вентиля 2И и соответствует инерциальной модели.

Указание на использование транспортной модели обеспечивается ключевым словом Transport в правой части оператора назначения. Например:

YT<= transportXIandX2 after 10ns;

Он отображает транспортную модель задержки вентиля. Если ключевое слово transport отсутствует, то подразумевается инерционная задержка. При транспортной задержке все изменения входных сигналов будут передаваться в выходные, но с указанной задержкой.

Задержка может быть задана не константой, а выражением. Для этого ее надо задать как параметр настройки в описании интерфейса объекта. Например:

Entity 12 is

Generic (T: time=10ns); - параметр настройки Т равен 10 не

Port (XI, Х2: in std_logic;

Y: out std_logic);

End 12;

Architecture A1 inert of 12 is

Begin

Y <= XI and X2 after T;

EndA1 inert;

Примеры описания регистровых схем на языке VHDL.

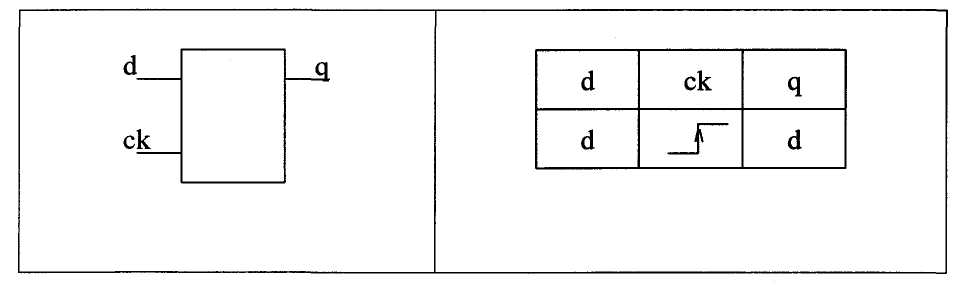

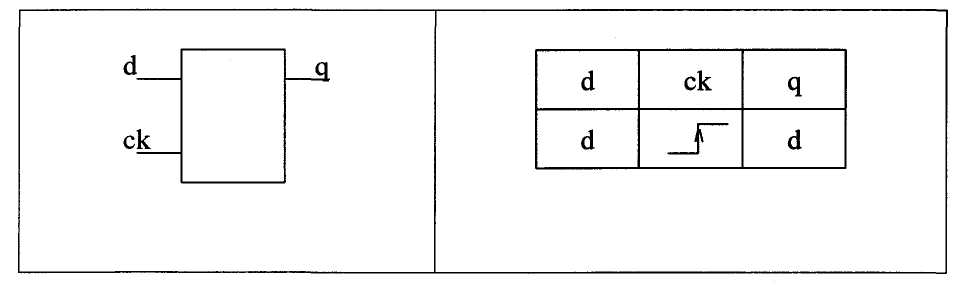

Триггер D-типа

Триггер работает по положительному фронту импульса. При этом происходит запись информации со входа D-триггера на его выход Q.

VHDL-файл имеет следующее описание:

Library ieee;

Use ieee.std_logic_1164.all;

Entity dtype is Port (d, ck: in std_logic; q: out std_logic); end dtype;

architecture behavior of dtype is

begin

process (d, ck)

begin

if ck=' 1' and ck'event then

q<=d;

end if;

end process;

endbehavior;