Оглавление

Лабораторная работа 1.............................................................................................. 2

Формирователь цифровых сигналов.......................................................................... 2

Лабораторная работа 2............................................................................................ 16

Исследование компаратора сигналов....................................................................... 16

Лабораторная работа 3............................................................................................ 22

Исследование сумматоров на базе простейших логических элементов................. 22

Литература.................................................................................................................. 32

Лабораторная работа 1

Формирователь цифровых сигналов

Цель работы

1.1. Исследование способов построения генераторов цифровых последовательностей.

1.2. Освоение методов программирования цифровых генераторов по заданной форме сигнала.

Задание

2.1. Задание для предварительной подготовки к работе

Изучить изложенный в пособии материал. Составить список команд для формирования цифрового сигнала заданной формы в соответствии с вариантом индивидуального задания, см. пункт 5.

2.2. Задание на экспериментальную часть

Составить схему цифрового генератора на базе имеющихся в программе моделей STIM, указать атрибуты в соответствии с заданием и получить изображение заданной цифровой последовательности.

Методические указания по выполнению работы.

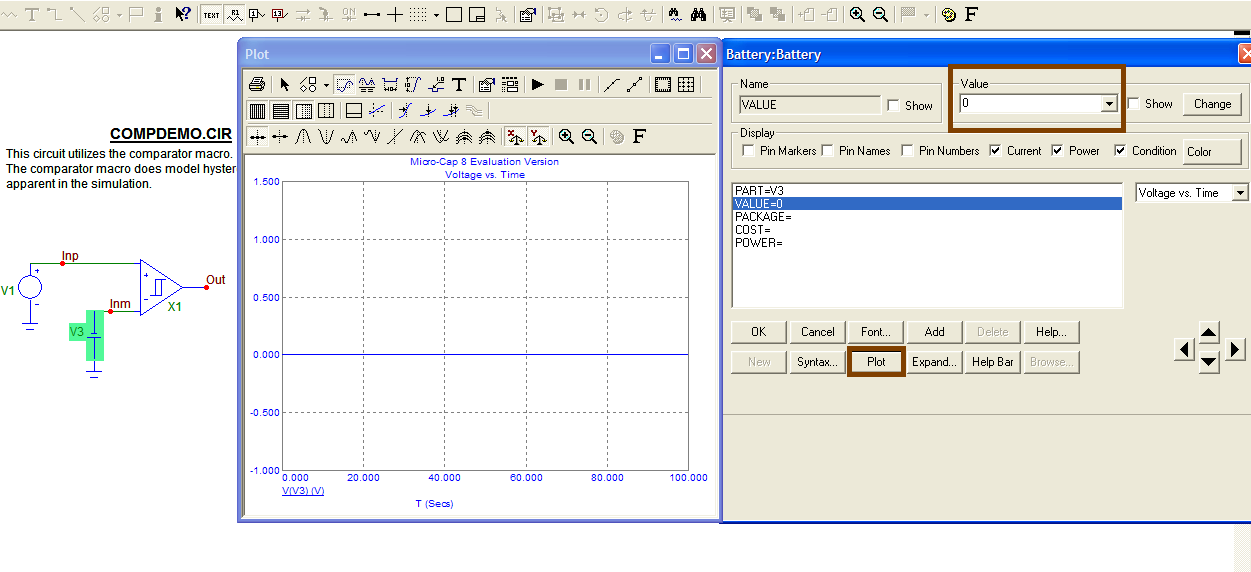

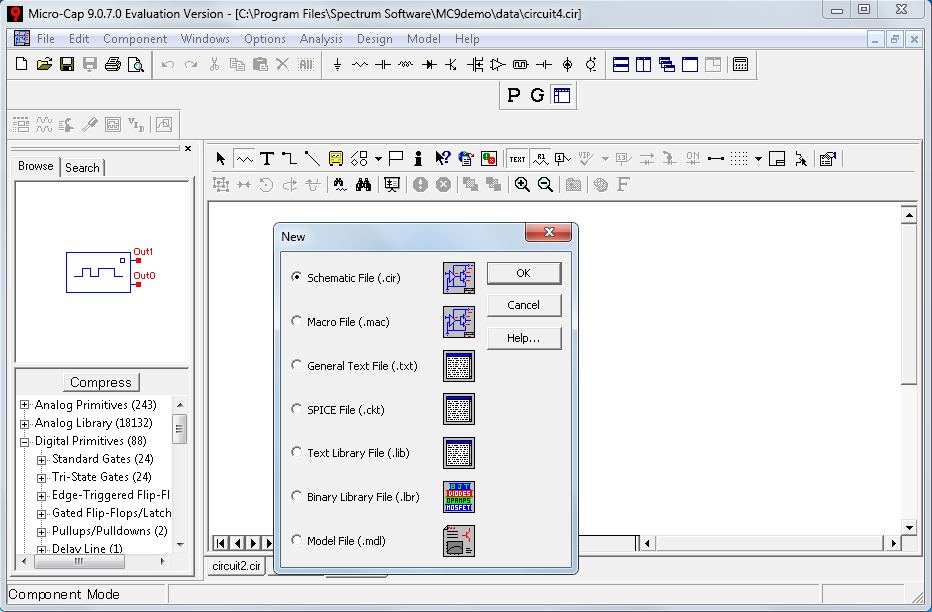

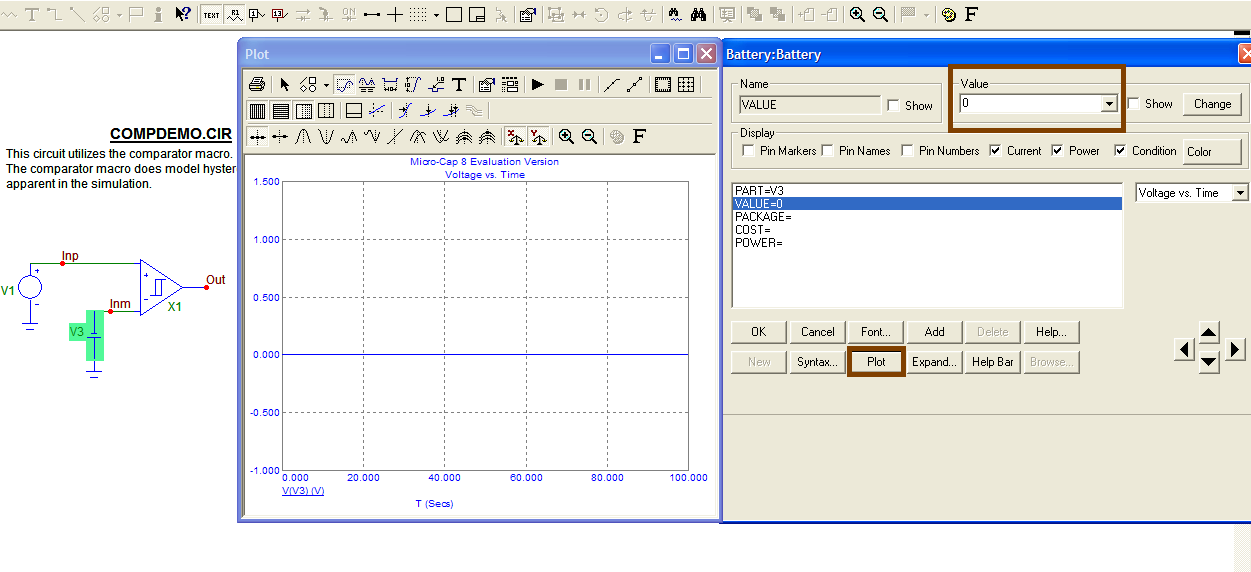

3.1. Загрузить программу схемотехнического моделирования МС 7…9 двойным щелчком по ее пиктограмме; при этом на экране появляется рабочее окно главного меню, рис.1.

Рис. 1

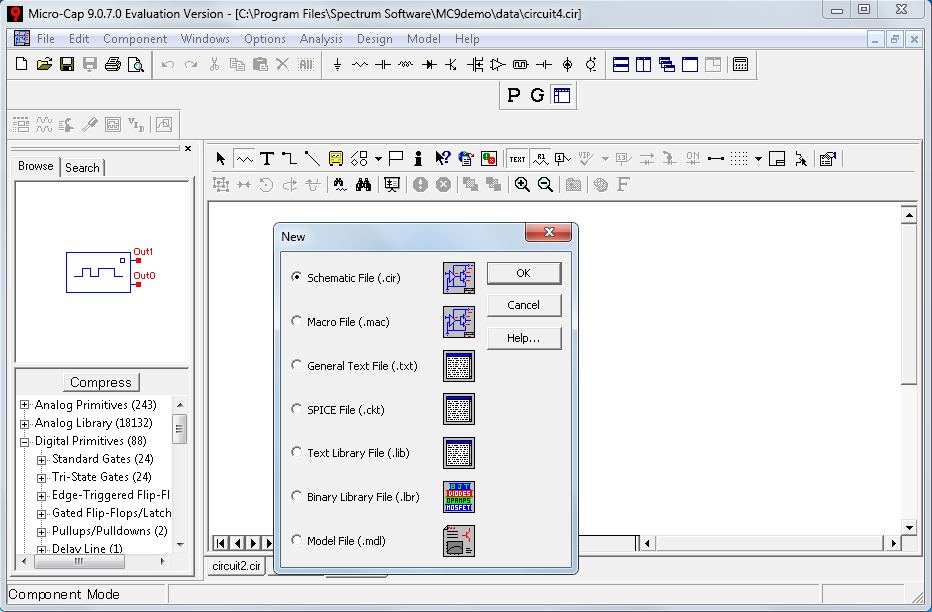

3.2. На верхней командной линейке выбираем режим ФАЙЛ (FILE) и по команде СОЗДАТЬ (NEW) открываем новый схемный файл (SCHEMATIC) с расширением.cir, где будем создавать чертёж исследуемой схемы.

3.3. Загрузить схему исследуемого генератора цифровых чисел STIM 1…STIM 16 в соответствии с индивидуальным заданием по команде COMPONENT ->DIGITAL PRIMITIVES->STIMULUS GENERATORS -> STIM1…16.

3.3. Загрузить схему исследуемого генератора цифровых чисел STIM 1…STIM 16 в соответствии с индивидуальным заданием по команде COMPONENT ->DIGITAL PRIMITIVES->STIMULUS GENERATORS -> STIM1…16.

3.4. Кликнуть курсором по изображению выбранного типа генератора: появится окно задания параметров выбранной схемы.

Рис. 2

3.5. Задать имена и значения атрибутов анализируемой схемы:

· имя схемы PART дается произвольно, по умолчанию первым символом в цифровых схемах ставится U,

· в атрибуте FORMAT записывается заданный формат представления чисел цифрового генератора в соответствии с заданием,

· атрибут COMMAND имеет произвольную форму: это имя массива команд, описывающих форму выходного сигнала генератора,

· имя модели «вход-выход» записывается в атрибуте IO-MODEL, непродвинутому пользователю лучше взять стандартную модель IO STD – её основные параметры указаны в нижней части окна редактора; в правой части этого окна указаны и другие, наиболее часто употребляемые модели,

· уровень сложности модели «вход- выход» IO LEVEL по умолчанию принимается равным нулю (см. раздел 4),

· в атрибутах POWER NODE и GROUND NODE указаны по умолчанию имена цифровых узлов источника питания и земли: $G DPWR и $G DGND, соответственно.

3.6. В окне редактора после директивы.define ввести присвоенное COMMAND имя, в последующих строках записать строки команд управления формой выходного сигнала в соответствии с заданием.

3.7. Пронумеровать узлы схемы с помощью пиктограммы

При желании можно внести на чертёж схемы текстовую информацию с помощью пиктограммы Т, расположенной на нижней линейке рабочего окна. Также можно сохранить исследуемую схему: в нижней части рабочего окна записано имя файла с вашей схемой, которое программа дала автоматически с расширением.cir, кликнув по этому названию, ответьте «save», сохранить.

3.8. Провести анализ переходного процесса заданного варианта генератора:

· по команде АНАЛИЗ (ANALYSIS)->АНАЛИЗ ПЕРЕХОДНЫХ ПРОЦЕССОВ (TRANSIENT ANALYSIS) вывести на экран окно задания параметров анализа,

· в строке время расчета (TIME RANGE) указать время анализа не менее, чем длительность сигнала по Вашему заданию,

· в столбце Р указывается номер страницы выводимого на экран графика, при наличии нескольких выходов желательно везде ставить 1, при этом все графики наблюдаются одновременно,

· по оси Х указывается время Т, а по оси У –цифровой сигнал d(n) в соответствующих узлах схемы, n - номер узла, масштаб по осям X и Y лучше первоначально принять auto,

· запустить анализ переходного процесса (RUN).

3.9. Определить численные параметры смоделированного сигнала: логические уровни и временные метки. Для этого воспользоваться курсорами с помощью пиктограммы  зарисовать или распечатать временные диаграммы полученных цифровых последовательностей с указанием размерностей по осям Х и Y.

зарисовать или распечатать временные диаграммы полученных цифровых последовательностей с указанием размерностей по осям Х и Y.

3.10. Сделать выводы по проделанной работе.

Таблица 1.

| Условное обозначение

| Состояние

|

|

| логическая 1,высокий уровень,high

|

|

| логический ноль, низкий уровень, low

|

| R

| переход от низкого уровня к высокому, rize

|

| F

| переход от высокого уровня к низкому, fall

|

| X

| состояние 1, 0 или нестабильное

|

| Z

| любое из перечисленных выше состояний (состояние высокого импеданса, при котором логический уровень неопределенный)

|

Рис. 3

В программе МС каждому реальному цифровому компоненту ставятся в соответствие следующие модели:

· для сопряжения с аналоговыми устройствами, которые могут подключаться к его входу и выходу, ставятся два устройства интерфейса Д/А (А/Ц) и А/Д (Ц/А),которые осуществляют обмен данными между подпрограммами, моделирующими аналоговые и цифровые устройства;

· модели вход/выход (I/O model),отражающие входные и выходные комплексные сопротивления данного цифрового компонента;

· временные модели, учитывающие запаздывания сигналов в различных элементах схемы.

Модели цифровых компонентов, стандартные и создаваемые пользователем, размещаются в библиотеке программы LIBRARY в файлах с префиксом dig.

При соединении нескольких цифровых компонентов различного назначения необходимо соблюдать соответствие длительностей переходных процессов составляющих элементов: времени установления и спада, называемых временем переключения TSWLH и TSWHL, и длительности сигналов. В свою очередь эти параметры зависят от величин входных и выходных сопротивлений и емкостей цифровых моделей.

Таблица 2.

| Идентификатор параметра

| Параметр

| Значение по умолчанию

| Единица измерения

|

| INLD

| Входная емкость

|

| Ф

|

| OUTLD

| Выходная емкость

|

| Ф

|

| DRVH

| Выходное сопротивление высокого уровня

|

| Ом

|

| DRVL

| Выходное сопротивление низкого уровня

|

| Ом

|

| AtoD1

| Имя макромодели интерфейса А/Ц первого уровня

| AtoDDefault

| -

|

| DtoA1

| Имя макромодели интерфейса Ц/А первого уровня

| DtoADefault

| -

|

| AtoD2

| Имя макромодели интерфейса А/Ц второго уровня

| AtoDDefault

| -

|

| DtoA2

| Имя макромодели интерфейса Ц/А второго уровня

| DtoADefault

| -

|

| AtoD3

| Имя макромодели интерфейса А/Ц третьего уровня

| AtoDDefault

| -

|

| DtoA3

| Имя макромодели интерфейса Ц/А третьего уровня

| DtoADefault

| -

|

| AtoD4

| Имя макромодели интерфейса А/Ц четвертого уровня

| AtoDDefault

| -

|

| DtoA4

| Имя макромодели интерфейса Ц/А четвертого уровня

| DtoADefault

| -

|

| TSWLH1

| Время переключения 0-1 для DtoA1

|

| с

|

| TSWLH2

| Время переключения 0-1 для DtoA2

|

| с

|

| TSWLH3

| Время переключения 0-1 для DtoA3

|

| с

|

| TSWLH4

| Время переключения 0-1 для DtoA4

|

| с

|

| TSWHL1

| Время переключения 1-0 для AtoD1

|

| с

|

| TSWHL2

| Время переключения 1-0 для AtoD2

|

| с

|

| TSWHL3

| Время переключения 1-0 для AtoD3

|

| с

|

| TSWHL4

| Время переключения 1-0 для AtoD4

|

| с

|

| DIGPOWER

| Имя макромодели источника питания

| DIGIFPWR

| -

|

Входная и выходная емкости определяют время задержки сигнала в цифровом элементе. Выходные сопротивления цифрового компонента зависят от его состояния: в состоянии логической 1 оно обозначается DRVH, в состоянии 0 как DRVL.

Пользователь может составить макромодель интерфейса со своими численными значениями параметров и занести её в библиотечный файл DIGIO.LIB.

В библиотеке интерфейсов МС содержатся стандартные модели IO, приведенные в таблице 3, отличающиеся друг от друга разным уровнем сложности (IO LEVEL): имена макромоделей интерфейса AtoD1, DtoA1, …, AtoD4, DtoA4. Текстовое описание моделей приведено в указанном выше файле.

Таблица 3.

| IO_LEVEL

| Определение

|

|

| Текущее значение параметра DIGIOLVL окна Global Settings (по умолчанию равно 1)

|

|

| Основная (простейшая) модель, имеющая логические состояния 0, 1, X, R и F (AtoD1/DtoA1)

|

|

| Основная (простейшая) модель без промежуточного состояния X (AtoD2/DtoA2)

|

|

| Сложная модель с промежуточным состоянием X (AtoD3/DtoA3)

|

|

| Сложная модель без промежуточных состояний X, R и F (AtoD4/DtoA4)

|

Источник питания

Источник питания задается макромоделью c именем DIGIFPWR, текстовое описание которой содержится в библиотечном файле DIGIO.LIB, по умолчанию его напряжение равно 5 В. Если необходимо изменить величину напряжения источника питания, нужно зайти в описание этой модели в указанном файле и изменить численное значение параметра VOLTAGE. В числе атрибутов модели указывается узел подключения источника питания, а также земли.

4.5. Способы задания параметров сигнала в генераторе STIM

Программа МС может обеспечивать достаточно сложные цифровые последовательности. Форма выходного сигнала задаётся одним из двух способов:

· FSTIM – параметры сигнала записываются пользователем в файл, имя которого указывается в атрибуте FILE, и он содержится в библиотеке DIGIO.LIB,при моделировании такого генератора в атрибутах указывается имя файла;

· STIM – в атрибуте COMMAND указывается имя команды – условное обозначение набора команд, формирующих цифровой сигнал, например PART 1, INN или др. По директиве.define PART 1 в текстовом окне описания параметров цифрового сигнала записываются последовательные по времени состояния генератора.

В данной работе рассматриваются STIM генераторы.

Командные последовательности, задающие форму цифрового сигнала, могут быть представлены в различном виде. Ниже приведены несколько примеров, рис. 4…7

Пример 1.

.DEFINE IN1

.DEFINE IN1

+0NS 1

+10NS 0

+20NS 1

Рис. 4

Первая строка указывает состояние генератора в начале счёта, в данном случае 1. Вторая и третья строки – выходные уровни спустя 10нс и 20нс от начала; символ + означает начало новой строки команды.

Пример 2.

В приведенном ниже примере второй символ + указывает на продолжение предыдущей строки, при этом начало последующего временного интервала отсчитывается от конца предыдущего

.DEFINE IN3

.DEFINE IN3

+0NS 0

+LABEL=BEGIN

+ +5NS 1

+ +5NS 0

+ +5NS GOTO BEGIN -1 TIMES

Рис. 5

В рассматриваемом примере переменная LABEL – имя метки, в данном случае < BEGIN>, используется для организации цикла с помощью оператора перехода GO TO, который передаёт управление на строку, следующую за оператором LABEL = <имя метки>. Переменная <n> times задаёт количество повторяющихся циклов GO TO, при =-1 задаётся бесконечное повторение цикла.

Пример 3.

.DEFINE IN4

.DEFINE IN4

+LABEL=BEGIN

+ +0NS 00

+ +5NS 01

+ +5NS 10

+ +5NS 11

+ +5NS GOTO BEGIN -1 TIMES

Рис. 6

Этот вариант отличается от предыдущих тем, что цифровой генератор обеспечивает две цифровых последовательности.

Пример 4.

.DEFINE IN5

+LABEL=BEGIN

+LABEL=BEGIN

+ +0NS INCR BY 01

+ +10NS GOTO BEGIN UNTIL GE 06

+ +10NS F0

+ +10NS F1

Рис. 7

В этом примере генератор имеет восемь выходных сигналов

Атрибут FORMAT (формат)

В этом атрибуте записывается формат представления выходных сигналов генератора в строках заданной команды: при бинарном представлении логических уровней сигнала записывается 1; 3 – при восьмиразрядной системе счисления (OCTAL) и 4- при шестнадцатеричном представлении (HEX). Цифры 1, 2 или 3 – это показатели степени 2 при соответствующей системе счисления; сумма этих цифр, записанных в атрибуте «формат» равна числу выходов цифрового генератора. Ниже приведена таблица соответствия между используемыми в МС системами чисел.

Таблица 4.

| Десятичная (Decimal)

|

|

|

|

|

|

|

|

|

| Шестнадцатеричная (HEX)

|

|

|

|

|

|

|

|

|

| Двоичная (Binary)

|

|

|

|

|

|

|

|

|

| Десятичная (Decimal)

|

|

|

|

|

|

|

|

|

| Шестнадцатеричная (HEX)

|

|

| A

| B

| C

| D

| E

| F

|

| Двоичная (Binary)

|

|

|

|

|

|

|

|

|

Примеры:

· Format=1, генератор имеет один выход с бинарным представлением уровней,

· Format=11, два выхода с бинарным сигналом на каждом из них,

· Format=4, четыре выхода: логическое состояние каждого из них опреляется цифрой четырёхпозиционного двоичного кода, эквивалентного записанному в программе шестнадцатеричному числу, см. таблицу4. Аналогично определяются параметры генератора в форматах 44; 14; 411 и т.д.

В приведенных в разделе 4.5 примерах 1, 2 и 3 может использоваться только бинарный формат, в то время как в примере 4 может быть использован как бинарный формат 11111111, так и шестнадцатеричный формат 44.

5. Таблица вариантов.

Таблица 5

| № варианта

| Тип схемы

| Format

| Наличие цикла

| Отсчеты от начала сигнала

| Последующий отсчет от конца предыдущего

| Длительность такта, ns

| Вид цифровой последовательности

|

|

| Stim1

|

| -

| +

| -

|

|

|

|

| Stim1

|

| -

| -

| +

|

|

|

|

| Stim1

|

| -

| +

| -

|

|

|

|

| Stim2

|

| -

| -

| +

|

| D9; DA

|

|

| Stim2

|

| -

| +

| -

|

| 55; AA

|

|

| Stim2

|

| -

| -

| +

|

| E5; 26

|

|

| Stim4

|

| -

| +

| -

|

| D5; D6

D4; D8

|

|

| Stim4

|

| +

| -

| +

|

| EE; 55

DD; AA

|

|

| Stim4

|

| -

| +

| -

|

| 97; 96

94; 98

|

|

| Stim8

|

| +

| -

| +

|

| 97; 9F

B7; AD

97; 9F

B7; AD

|

|

| Stim8

|

| -

| +

| -

|

| D5; 44

DF; 46

D5; 44

DF; 46

|

|

| Stim8

|

| +

| -

| +

|

| DF; 44

DE; 45

DC; 4C

DC; 55

|

|

| Stim16

|

| -

| +

| -

|

| DD; 44

AA; 55

EE; 66

CC; 3C

EE; 66

CC; 3C

66; 99

CC; 99

|

|

| Stim16

|

| +

| -

| +

|

| FF;FF

4D;5C

AC;A2

55;CF

FF;FF

4D;5C

AC;A2

55;CF

|

|

| Stim16

|

| -

| +

| -

|

| AA; BB

DD; 33

55; 66

11; 99

BB; 22

FF; AA

BB; DD

DD; AB

|

Содержание отчёта

Отчёт должен содержать:

1) титульный лист,

2) цель работы,

3) структурную схему генератора,

4) список команд формирования сигнала для заданного варианта,

5) графики полученных результатов,

6) выводы по проделанной работе.

7. Контрольные вопросы

1. Поясните структуру генератора числовых последовательностей.

2. Зачем нужны ЦАП и АЦП в компьютерной модели цифрового генератора?

3. Что такое IO model? Какими основными параметрами она описывается?

4. Что означает атрибут IO LEVEL? Какие значения он может принимать?

5. Какие значения может принимать атрибут FORMAT? Чему он равен в Вашем задании? Может ли он принимать другие значения?

6. Какие атрибуты цифрового генератора связаны с количеством его выходов?

7. Какие команды определяют цикличность программы генератора?

8. Что означает команда +10NS 01?

9. Сколько выходов имеет генератор и в каком логическом состоянии они находятся, если одна из команд имеет вид: + + 5ns B?

10. Для чего в модели «вход-выход» задаются временные параметры?

11. Что представляет собой генератор с атрибутом FORMAT=4?

12. Каким следует задать время расчета при анализе переходной характеристики генератора, если последняя команда в окне редактора + 600 NS?

Лабораторная работа 2

Цель работы

Исследование компаратора сигналов на базе программы схемотехнического моделирования MICROCAP.

Задание на экспериментальную часть

2.1. Загрузить схему исследуемого компаратора.

2.2. Установить параметры источников сигналов V1 и V2 в соответствии с выполняемым заданием и вариантом.

2.3. Исследовать схему компаратора в следующих режимах:

- в качестве нуль-органа, или детектора нулевого уровня, при V2(t)=0;

- в качестве порогового устройства при V2(t)=const;

- в режиме сравнения двух переменных сигналов: V1≠0 и V2≠0.

2.4. Определить ошибку преобразования компаратора в процессе исследований.

Рис.1

В инструментальной строке окна выбрать опцию  и проставить номера узлов (самостоятельно узлы схемы не переименовывать!).

и проставить номера узлов (самостоятельно узлы схемы не переименовывать!).

3.2. Исследование схемы в режиме нуль-органа.

Для исследования компаратора в данном режиме в качестве V2 используется источник постоянного напряжения с нулевым уровнем выходного сигнала, для этого необходимо открыть Component, выбрать Battery и установить на место V2.

Рис.2

В качестве источника V1 использовать источник синусоидального напряжения (sine source) с частотой от 1 до 20 кГц амплитудой 1 В.Чтобы просмотреть временные диаграммы сигналов на выходе источников V1 и V2,воспользуйтесь опцией Plot(график),предварительно дважды кликнув на нужный источник.При этом в левой части экрана монитора появится график искомого сигнала,проверьте,чтобы он соответствовал Вашему режиму и варианту.

Анализ выходных сигналов компаратора во временной области осуществляется последовательным выполнением команд: Analysis-Transient-Transient Analysis Limits-Run. В подменю Transient Analysis Limits (рис.3) задаются пределы и условия анализа, а так же перечень выводимых на экран кривых.

Рис.3

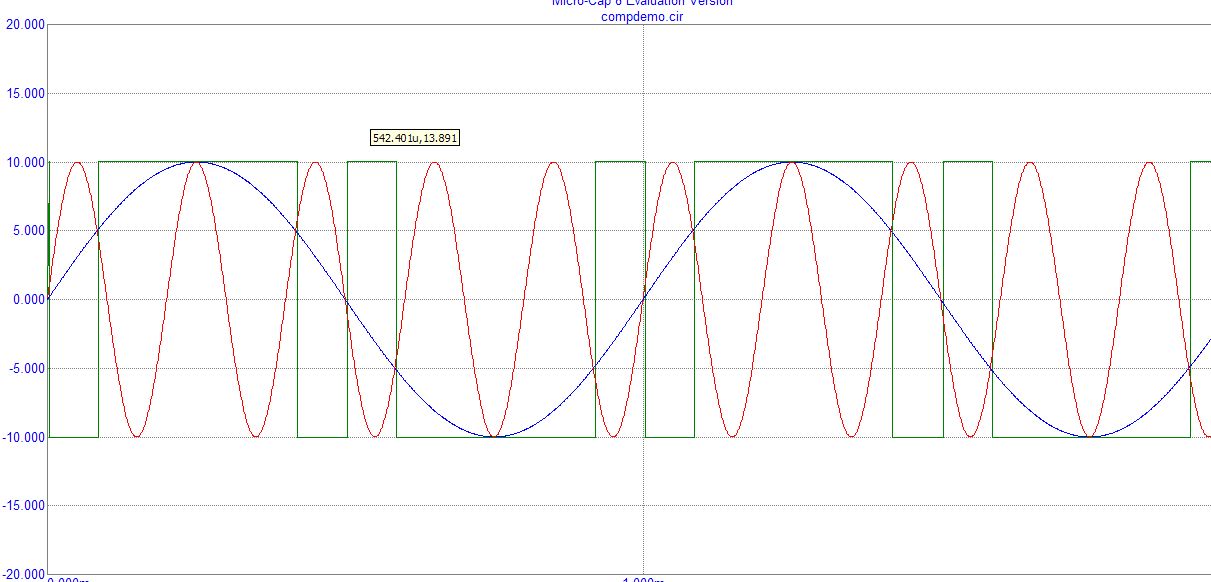

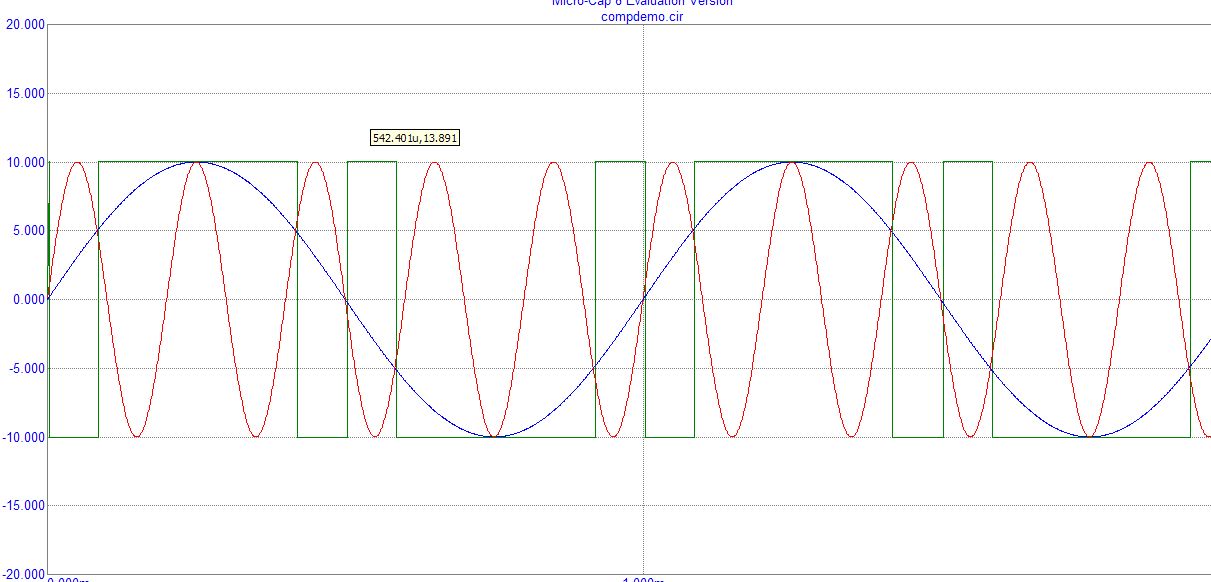

В приведённом окне указывается время,в течение которого программа производит анализ устройства (Time range),оно должно быть не менее,чем 3…5 периодов наблюдаемого сигнала.В строках X range и Y range указываются диапазоны исследуемых величин,выводимых на экран,первоначально можно указать режим auto.Полученные в эксперименте зависимости имеют вид,представленный на рис 4.

Определите ошибку преобразования компаратора с помощью опции, приведённой на верхней линейке окна (на рис.4 стрелками показано значение ошибки).

Рис.4

3.3. Исследование схемы в качестве порогового устройства.

В этом случае эксперимент проводится аналогично п.3.2,изменяется только уровень выходного сигнала источника постоянного порогового напряжения V2,его следует принять равным +,- 0,1…0.9 В.Просмотрите и зарисуйте изменение формы сигнала с выхода компаратора при двух разных значениях порогового напряжения,оцените ошибку преобразования.

3.4. Режим сравнения двух переменных сигналов.

3.4.1 Установить форму и параметры источников сигналов V1 и V2 в соответствии с таблицей индивидуальных заданий..В качестве V1 использовать функциональный источник напряжения NFV по команде Component – Analog Primitives – Function Sources – NFV.Источник V2 voltage source находится аналогично.Просмотреть и зарисовать временные диаграммы сигналов на входе и выходе компаратора.Пример временных диаграмм приведён на рис 5.

Рис.5

3.4.2. Установить в качестве входных источников V1 и V2 также voltage source,при этом форму сигнала для V1 сформировать из заданного варианта в колонке V2,но со сдвигом фазы колебания на 90 градусов.Начальная фаза синусоидального сигнала записывается в последней цифре формулы V2(в исходном варианте фазаV2 равна нулю).В режиме Transient (временной анализ) получить временные диаграммы сигналов для следующих случаев:

- построить график зависимости разности входных сигналов V(V1) – V(V2) и выходного напряжения V(out) от времени на одном графике,

- построить график зависимости выходного напряжения компаратора V(out) от разности входных сигналов V(V1) – V(V2).

По снятым временным диаграммам оценить погрешности преобразования компаратора по первому и второму графикам и сравнить их.

Варианты индивидуальных заданий

Таблица 1

| № Варианта

| V1 (NFV)

| V2 (VOLTAGE SOURCE)

|

|

| 5+1*SIN(2*Pi*T*2E6)+2*COS(2*PI*T*2E6)

| DC 0 AC 1 0 Sin 0 1 1E6 0 0 0

|

|

| SIN(2*Pi*T*1E6)+7*COS(2*PI*T*1E6)+

| DC 0 AC 1 0 Sin 0 2 4E6 000

|

|

| 4+2*SIN(2*Pi*T*5E6)+ COS(2*PI*T*3E6)

| DC 0 AC 1 0 Sin 0 3 2E6 0 0 0

|

|

| COS(2*Pi*T*10E3)+2*COS(2*PI*T*20E)

| DC 0 AC 1 0 Sin 0 4 3k 0 0 0

|

|

| 6+2*SIN(2*Pi*T*2E6)+2*COS(2*PI*T*23E6)

| DC 0 AC 1 0 Sin 0 5 1E6 0 00 0

|

|

| 2+5*COS(2*Pi*T*4E6)+3*SIN(2*Pi*T*2E6)

| DC 0 AC 1 0 Sin 0 6 1.1E6 00 0 30

|

|

| SIN(2*Pi*T*11E6)+6*COS(2*PI*T*3E6)

| DC 0 AC 1 0 Sin 0 7 2E6 0 00

|

|

| 5+2*SIN(2*Pi*T*4E3)+ COS(2*PI*T*12E3)

| DC 0 AC 1 0 Sin 0 8 7E3 0 00

|

|

| 5+2*SIN(2*Pi*T*10E3)+2*COS(2*PI*T*2E3)

| DC 0 AC 1 0 Sin 0 9 4E3 000

|

|

| SIN(2*Pi*T*3E6)+2*COS(2*PI*T*2E6)

| DC 0 AC 1 0 Sin 0 10 1E6 000

|

|

| SIN(2*Pi*T*10E4)+2*COS(2*PI*T*2E4)

| DC 0 AC 1 0 Sin 0 11 1E4 000

|

|

| COS(2*PI*T*2E5)+ SIN(2*Pi*T*3E5)

| DC 0 AC 1 0 Sin 0 12 1E5 000

|

|

| 3+4*SIN(2*Pi*T*2E6)+2*COS(2*PI*T*3E6)

| DC 0 AC 1 0 Sin 0 13 1E6 0 0 0

|

|

| 5+SIN(2*Pi*T*1E6)+7*COS(2*PI*T*2E6)

| DC 0 AC 1 0 Sin 0 14 1E6 0 00

|

|

| SIN(2*Pi*T*1E6)+7*COS(2*PI*T*3E6)

| DC 0 AC 1 0 Sin 0 15 2Е6 000

|

Содержание отчёта.

Отчёт должен содержать

-титульный лист,

-цель работы,

-структурную схему устройства,

-номер и параметры варианта,

-графики полученных результатов с выводами по проделанной работе.

6.Контрольные вопросы.

1. Каково назначение компаратора?

2. На каких элементах может строиться компаратор?

3. Что такое погрешность компаратора?

4. Как определяется экспериментально погрешность компаратора?

5. Как устанавливаются параметры временного анализа при известных сигналах?

6. Зависит ли форма выходного сигнала компаратора от параметров входных сигналов?

7. Что такое нуль-орган?

8. Что такое пороговый режим компаратора,где он может применяться?

Лабораторная работа 3

Цель работы

1.1. Исследование способов построения двоичных сумматоров по таблице истинности на базе простейших логических элементов в программе схемотехнического моделирования Micro-Cap.

1.2. Экспериментальное исследование построенных сумматоров.

2. Задание для предварительной подготовки к работе

. Составить две таблицы истинности и командные последовательности входных цифровых сигналов для генераторов Stim2 (выходы А и В) и Stim1 (выход PI) в соответствии с вариантом индивидуального задания (см. пункт 5). Построение командных последовательностей см. в лабораторной работе 1.

Задание на экспериментальную часть

Составить схему сумматора по модулю 2 или полусумматора, как указано в Вашем индивидуальном задании (пункт 5), а также схему полного одноразрядного сумматора на базе простейших логических элементов. Получить временные характеристики сигналов на входе и выходе исследуемых схем.

Краткие сведения из теории

5.1. Типы исследуемых сумматоров

Основной элементарной операцией, выполняемой над кодами чисел в цифровых устройствах, является арифметическое сложение.

Сумматор – логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и др. Указанные операции выполняются в арифметическо-логических устройствах (АЛУ) или процессорных элементах, ядром которых являются сумматоры.

По числу входов и выходов одноразрядные двоичные сумматоры подразделяются на следующие виды:

· сумматоры по модулю 2, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

· полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд);

· полные одноразрядные двоичные сумматоры, характеризуются наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд).

Таким образом, очевидно, что одноразрядные двоичные сумматоры бывают с двумя входами (сумматор по модулю 2 и полусумматор) и сумматоры с тремя входами (полные одноразрядные двоичные сумматоры).

5.2. Построение двоичного сумматора по таблице истинности на основе простейших логических элементов

Построение двоичных сумматоров обычно начинается с сумматора по модулю 2. Исходя из правил суммирования в двоичной арифметики, получим таблицу истинности этого сумматора (таблица 1). Принципиальная схема сумматора по модулю 2 и его условно-графическое изображение (УГО), которое совпадает со схемой исключающего «ИЛИ» в двоичной арифметике, представлены на рис.1 и рис.2, соответственно.

Рис. 1 Рис. 2

Сумматор по модулю 2 выполняет суммирование без учета переноса. В полном двоичном сумматоре требуется учитывать перенос, поэтому требуются схемы, позволяющие формировать перенос в следующий двоичный разряд. Таблица истинности такой схемы, называемой полусумматором, приведена в таблице 2. В соответствии с принципами построения произвольной таблицы истинности получим схему полусумматора, рис.3 и его УГО (рис.4).

Рис. 3 Рис. 4

Схема полусумматора формирует перенос в следующий разряд, но не может учитывать перенос из предыдущего разряда, поэтому она и называется полусумматором. Таблицу истинности полного двоичного одноразрядного сумматора можно получить из правил суммирования двоичных чисел (таблица 3). В обозначении входов использовано следующее правило: в качестве входов использованы одноразрядные числа A и B; перенос обозначен буквой P; для обозначения входа переноса используется буква I (сокращение от английского слова input – вход); для обозначения выхода переноса используется буква O (сокращение от английского слова output – выход).

В соответствии с принципами построения принципиальной схемы по произвольной таблице истинности получим схему полного двоичного одноразрядного сумматора (рис.5) и его УГО (рис.6).

Рис. 5 Рис. 6

Одноразрядные сумматоры практически никогда не использовались, так как почти сразу же были выпущены микросхемы многоразрядных сумматоров.

5.3. Простейшие логические элементы

В программе схемотехнического моделирования Micro-Cap существует база с простейшими логическими элементами (таблица 4),из которых будут строиться исследуемые устройства.

Таблица 4

| Тип

| Параметры

| Узлы

| Логическая операция

| Условное изображение

|

| And

| Количество входов

| In*

Out

| «И»

|

|

| Inverter

|

| In

Out

| «НЕ»

|

| Buffers

|

| In

Out

| Повторяет заданную последовательность

|

| Nand

| Количество входов

| In*

Out

| «И-НЕ»

|

| Nor

| Количество входов

| In*

Out

| «ИЛИ-НЕ»

|

| Or

| Количество входов

| In*

Out

| «ИЛИ»

|

| XNor

|

| In

Out

| Исключающее «ИЛИ-НЕ»

|

| Xor

|

| In

Out

| Исключающее «ИЛИ»

|

5.4. Цифровые генераторы

Для задания цифровой последовательности в программе MC существует база с цифровыми генераторами, которые рассматривались ранее в лабораторной работе №1. В данной работе рассматриваются STIM1..2 генераторы.

Для начала рассмотрим цифровой генератор с одним выходом – STIM1. Этот генератор в данной работе пригодится для составления последовательности значения входа PI из таблицы истинности исследуемого сумматора. Например, дадим имя команды _1, тогда для последовательности PI:01010110 командная последовательность, задающая форму цифрового сигнала длительностью 450 нс, а длительность нуля или единицы 50нс, приведена в примере 1.

Пример 1.

.define _1

+0ns 0

+50ns 1

+150ns 0

+200ns 1

+250ns 0

+300ns 1

+350ns 1

+400ns 0

+450ns 0

Цифровой генератор STIM2 – генератор с двумя выходами. Этот генератор необходим в этой работе для создания последовательностей значений входов А и В из таблицы истинности сумматора. Для начала зададим имя команды _11. Тогда, для последовательностей А:10010101 и В:11010110 командная последовательность, задающая форму цифрового сигнала длительностью 450 нс, а длительность нуля или единицы 50нс, приведена в примере 2.

Пример 2.

.define _11

+0ns 11

+50ns 01

+100ns 00

+150ns 11

+200ns 00

+250ns 11

+300ns 01

+350ns 10

+400ns 00

+450ns 00

Имена команд для различных цифровых генераторов в рабочем окне программы MC должно быть неодинаковыми, иначе все генераторы примут одну и ту же командную последовательность.

Варианты индивидуальных заданий

Ниже в таблице 5 приведены варианты индивидуальных заданий. Для каждого варианта составлены входные последовательности для сумматоров с двумя и с тремя входами, где значения А, В и PI – значения входных последовательностей. В предварительной подготовке к работе, согласно правилам суммированиям в двоичной арифметике, необходимо построить таблицу истинности (см. пункт 5.2) в соответствии со своим вариантом задания.

По входным последовательностям А, В и PI требуется составить командную последовательность (см. пункт 5.4) и получить на выходе последовательности S и PO (см. таблицу 1, таблицу 2 и таблицу 3).

Таблица 5

| № варианта

| Входные последовательности для сумматора с двумя входами

| Входные последовательности для сумматора с тремя входами

|

|

| A: 01010101

B: 11111111

Сумматор по модулю 2

| PI:10011010

A:10001100

B:11101100

|

|

| A:10001100

B:11101100

Полусумматор

| PI:00010101

A:11001010

B:100000011

|

|

| A: 01101010

B: 10111110

Сумматор по модулю 2

| PI:01010101

A: 11011111

B: 00111100

|

|

| A: 01101010

B: 10111010

Полусумматор

| PI: 11110111

A: 01010101

B: 11111111

|

|

| A: 11111110

B: 01010111

Сумматор по модулю 2

| PI:11111010

A:10101011

B: 01010101

|

|

| A:11110011

B:00101001

Полусумматор

| PI: 00010100

A: 11111110

B: 01010111

|

|

| A: 10000011

B: 11110111

Сумматор по модулю 2

| PI: 11101001

A: 01101010

B: 10111110

|

|

| A: 10101111

B: 10101110

Полусумматор

| PI: 00000101

A: 10000011

B: 11110111

|

|

| A: 11011011

B: 10100010

Сумматор по модулю 2

| PI: 01101010

A: 10101111

B: 10101110

|

|

| A: 10111110

B: 01010101

Полусумматор

| PI: 00010100

A: 101000000

B: 10101110

|

|

| A: 101000000

B: 10101110

Сумматор по модулю 2

| PI: 10101010

A:11110011

B:00001001

|

|

| A: 10010001

B: 11110001

Полусумматор

| PI: 00111111

A: 11011111

B: 10100010

|

|

| A: 01000101

B: 01011110

Сумматор по модулю 2

| PI: 00111100

A: 10101100

B: 11010101

|

|

| A:10001100

B:11101000

Полусумматор

| PI:00010101

A:11001010

B:100000011

|

|

| A: 10010001

B: 11110001

Сумматор по модулю 2

| PI:00011011

A:11100101

B:00101101

|

Содержание отчета

Отчет должен содержать:

1) Титульный лист;

2) Цель работы;

3) Принципиальные схемы сумматоров;

4) Таблицы истинности для каждого сумматора;

5) Графики полученных результатов

6) Вывод по проделанной работе.

8.Контрольные вопросы

1. Каково назначение сумматора?

2. В чем главная разница между полусумматором и одноразрядным полным сумматором?

3. Какие простейшие логические элементы имеют несколько входов? Поясните почему.

4. Для чего задается командная последовательность?

5. Можно ли задать одно имя для STIM1 и STIM2? Поясните ответ.

Литература

1. П.Хоровиц, У.Хилл. Искусство схемотехники.-М.:Мир, 2011

2. А. Н. Касьянов. Micro-Cap в схемотехнике. –М.: ТГТУ, 2004

3. М.А.Амелина, С.А.Амелин. Программа схемотехнического моделирования Micro-Cap 8. -М.: Горячая линия –Телеком, 2007.

4. Разевиг В.Д. Схемотехническое моделирование с помощью Micro-Cap 7 М.: Горячая линия – Телеком, 2003.

5.Павлов В.Н.,Ногин В.Н.Схемотехника аналоговых электронных устройств.-М.:Горячая линия – Телеком,2005.

6.Угрюмов Е.П.Цифровая схемотехника. – Спб.:БХВ-Петербург,2004

Оглавление

Лабораторная работа 1.....................................................

3.3. Загрузить схему исследуемого генератора цифровых чисел STIM 1…STIM 16 в соответствии с индивидуальным заданием по команде COMPONENT ->DIGITAL PRIMITIVES->STIMULUS GENERATORS -> STIM1…16.

3.3. Загрузить схему исследуемого генератора цифровых чисел STIM 1…STIM 16 в соответствии с индивидуальным заданием по команде COMPONENT ->DIGITAL PRIMITIVES->STIMULUS GENERATORS -> STIM1…16.

зарисовать или распечатать временные диаграммы полученных цифровых последовательностей с указанием размерностей по осям Х и Y.

зарисовать или распечатать временные диаграммы полученных цифровых последовательностей с указанием размерностей по осям Х и Y.

.DEFINE IN1

.DEFINE IN1 .DEFINE IN3

.DEFINE IN3 .DEFINE IN4

.DEFINE IN4 +LABEL=BEGIN

+LABEL=BEGIN и проставить номера узлов (самостоятельно узлы схемы не переименовывать!).

и проставить номера узлов (самостоятельно узлы схемы не переименовывать!).