КОМПЬЮТЕРНАЯ СХЕМОТЕХНИКА И АРХИТЕКТУРА КОМПЬЮТЕРОВ

Методическое пособие

по выполнению лабораторных работ

по дисциплине «Компьютерная схемотехника и архитектура компьютеров»

для студентов направления подготовки

6.050101 «Компьютерные науки»

дневной формы обучения

Мариуполь

УДК 004.43(076.5)

Компьютерная схемотехника и архитектура компьютеров: методическое пособие по выполнению лабораторных работ по дисциплине «Компьютерная схемотехника и архитектура компьютеров» для студентов направления подготовки 6.050101 «Компьютерные науки» дневной формы обучения / сост. Т. А. Левицкая. – Мариуполь: ПГТУ, 2015. – 77 с.

В методических указаниях приведены основные положения, порядок выполнения и индивидуальные задания по выполнению лабораторных работ для изучения дисциплины «Компьютерная схемотехника и архитектура компьютеров».

| Составитель

| Т. А. Левицкая, канд. техн. наук, доцент

|

|

|

|

| Рецензент

| Д. С. Мироненко, канд. техн. наук, доцент

|

|

|

|

Утверждено

на заседании кафедры компьютерных наук,

протокол № 8 від 21 апреля 2015 г.

Утверждено

методической комиссией факультета информационных технологий,

протокол № 5 від 21 мая 2015 г.

©ГВУЗ «ПГТУ», 2015

СОДЕРЖАНИЕ

ВВЕДЕНИЕ.. 5

Лабораторная работа № 1. 6

МЕТОДЫ АНАЛИЗА И СИНТЕЗА КОМБИНАЦИОННЫХ СХЕМ. КОМБИНАЦИОННЫЕ СХЕМЫ С ОДНИМ ВЫХОДОМ... 6

1.1. Основные теоретические положения и методика выполнения работы.. 6

1.2. Задание и порядок выполнения работы.. 9

1.3. Структура отчета и требования к оформлению.. 9

1.4. Контрольные вопросы.. 9

Лабораторная работа № 2. 10

ЗНАКОМСТВО СО СРЕДОЙ САПР Altium Designer. 10

2.1. Основные теоретические положения, методика выполнения работы.. 10

2.2. Задание и порядок выполнения работы.. 11

2.3. Структура отчета и требования к оформлению.. 16

2.4. Контрольные вопросы.. 16

Лабораторная работа № 3. 17

ПРАКТИЧЕСКИЕ ИССЛЕДОВАНИЯ КОМБИНАЦИОННЫХ СХЕМ В ПРОГРАММЕ ALTIUM DESIGNER.. 17

3.1. Основные теоретические положения, методика выполнения работы.. 17

3.2. Задание. 22

3.3. Структура отчета и требования к оформлению.. 29

3.4. Контрольные вопросы.. 29

Лабораторная работа № 4. 30

ПРАКТИЧЕСКИЕ ИССЛЕДОВАНИЯ ТРИГГЕРОВ В ПРОГРАММЕ ALTIUM DESIGNER.. 30

4.1. Основные теоретические положения. 30

4.2. Задание и порядок выполнения работы.. 33

4.3. Структура отчета и требования к оформлению.. 42

4.4. Контрольные вопросы.. 42

Лабораторная работа № 5. 44

СОЗДАНИЕ УСЛОВНЫХ ГРАФИЧЕСКИХ ОБОЗНАЧЕНИЙ ЭЛЕМЕНТОВ В САПР ALTIUM DESIGNER.. 44

5.1. Основные теоретические положения. 44

5.2. Порядок выполнения работы.. 51

5.3. Структура отчета и требования к оформлению.. 51

5.4. Контрольные вопросы.. 52

Лабораторная работа № 6. 53

РАЗРАБОТКА В САРП ALTIUM DESIGNER ПОСАДОЧНЫХ МЕСТ НА ПЕЧАТНОЙ ПЛАТЕ.. 53

6.1. Основные теоретические положения и методика выполнения работы.. 53

6.2. Порядок выполнения работы.. 60

6.3. Структура отчета и требования к оформлению.. 60

6.4. Контрольные вопросы.. 61

Лабораторная работа № 7. 62

УПАКОВКА ВЫВОДОВ КОНСТРУКТИВНЫХ ЭЛЕМЕНТОВ.. 62

7.1. Основные теоретические положения и методика выполнения работы.. 62

7.2. Задание и порядок выполнения работы.. 68

7.3. Структура отчета и требования к оформлению.. 68

7.4. Контрольные вопросы.. 68

Лабораторная работа №8. 69

ЗНАКОМСТВО С АППАРАТНОЙ СРЕДОЙ КОМПЬЮТЕРА. РАБОТА С BIOS/UEFI 69

8.1. Основные теоретические положения. 69

8.2. Методика выполнения работы.. 71

6.3. Задание и порядок выполнения работы.. 75

6.4. Структура отчета и требования к оформлению.. 75

6.5. Контрольные вопросы.. 76

ЛИТЕРАТУРА.. 77

ВВЕДЕНИЕ

Целью дисциплины «Компьютерная схемотехника и архитектура компьютеров» является овладение фундаментальными понятиями, теорией и основами схемотехники современных электронно-вычислительных машин и систем и овладение теоретическими основами знаний архитектуры компьютеров и компьютерных сетей.

Изучение дисциплины направлено на освоение студентами теоретических основ построения и функционирования основных устройств, узлов, базовых элементов и архитектуры современной компьютерной техники, выполненные на базе интегральной технологии. Дисциплина формирует твердые практические навыки по оценке технического состояния компьютерной техники, расчетов параметров аналоговых и цифровых схем.

В результате изучения дисциплины студент должен знать:

─ физические принципы работы и логические основы построения элементов и узлов, которые составляют основу современной компьютерной техники;

─ методы анализа и расчета параметров элементов схемотехники компьютеризированных средств;

─ методики анализа условий функционирования цифровых и аналоговых схем компьютерной техники, а также порядок синтеза цифровых схем с заданными свойствами;

─ проводить расчеты необходимых параметров элементов компьютерной схемотехники, использовать в совместной работе базовые логические элементы различного типа логики;

Учебный курс базируется на знаниях, полученных при изучении дисциплин "Высшая математика", "Дискретная математика", "Физика" и "Основы электроники и электротехники". Также студент должен иметь навыки работы с персональным компьютером.

Цель проведения лабораторных занятий – глубокое усвоение студентами особенностей физических процессов, происходящих во время функционирования типовых элементов и узлов аналоговой и цифровой компьютерной схемотехники.

Лабораторная работа № 1.

МЕТОДЫ АНАЛИЗА И СИНТЕЗА КОМБИНАЦИОННЫХ СХЕМ. КОМБИНАЦИОННЫЕ СХЕМЫ С ОДНИМ ВЫХОДОМ

Цель: изучить методы анализа и синтеза комбинационных логических схем с одним выходом, оценки их аппаратурной сложности и быстродействия.

Задание и порядок выполнения работы

1. Определить свой вариант логической функции.

Для этого необходимо номер варианта в журнале перевести в двоичную систему счисления и подставить шесть разрядов полученного таким образом двоичного числа в Таблицу1 (α1 – младший разряд). Например, если задан номер варианта 10, то в двоичной системе счисления этот номер можно подать шестиразрядная числом 001010. То есть в Таблицу 2 подставляем значения:  (младший разряд),

(младший разряд),  ,

,  ,

,  ,

,  ,

,  .

.

2. Для своего варианта логической функции найти МДНФ, МКНФ

3. Построить схему для реализации функции на логических элементах И, ИЛИ, И-НЕ ИЛИ-НЕ.

Таблица 1

| № набора

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| a1

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| a2

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| a3

|

|

|

|

|

|

|

|

|

|

|

|

|

| a4

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| a5

|

|

|

|

|

|

|

|

|

|

|

|

|

| a6

|

|

|

|

|

|

|

|

1.

1.2.

1.3 Структура отчета и требования к оформлению

1) название и цель работы.

2) условие индивидуального задания;

3) краткие выводы по результатам работы.

1.4 Контрольные вопросы

1. Что такое логический элемент?

2. Описать три этапа синтеза комбинационной схемы.

3. Что называют простой конъюнкцией и простой дизъюнкцией?

4. Как строится карта Карно? Как происходит склейка элементов в ней?

Лабораторная работа № 2.

ЗНАКОМСТВО СО СРЕДОЙ САПР Altium Designer

Цель: изучение структуры САПР AltiumDesigner, ее возможностей,

состава и назначения основных программных модулей.

1.

Основные горячие клавиши

Space (пробел) – поворот (вращение) компонента или угла;

Шаг поворота задается в настройках DXP / Preferences/ PCB Editor, щелкнуть дважды ЛК и выбрать General / Шаг поворота-45 градусов.

Shift+Space – смена угла прокладки трассы или цепи;

X – зеркальное отображение компонента;

G – переключение шага сетки;

F11 – вызов инспектора;

Ctrl+MouseWheel – масштабирование изображения;

Нажатая клавиша Shift позволяет выделить несколько компонентов;

Включение – отключение видимой сетки выполняется нажатием клавиш Shift+G.

Нажатая клавиша Ctrl позволяет переместить компонент без отрыва от цепи

или трассы;

Основные определения

• Designator – номер вывода

• Layer – слой расположения (multilayer для всех слоев)

• Net – цепь

• Plated – наличие металлизации (параметр важный, в AD, начиная с шестого,

можно создать два файла сверловки, для отверстий с металлизацией и для

крепежных отверстий, без металлизации)

• Locked – блокировка площадки (перед возможным изменением параметров

выдаст запрос на подтверждение действия)

Назначение слоев

• Toplayer – верхний слой фольги

• Bottomlayer – нижний слой фольги

• Mechanicall – габаритное изображение элемента (в этом слое нужно рисовать контур элементов)

• Topoverlay – верхний слой маркировки (шелкографии)

• Bottomoverlay – нижний слой маркировки (шелкографии)

• Keep-outlayer – контур запрещенной для трассировки зоны (в нем рисуется

контур платы)

Система схемотехнического моделирования Altium Designer предназначена для моделирования и анализа электрических схем и микросхем памяти. Она позволяет моделировать аналоговые, цифровые, а также аналого-цифровые и цифро-аналоговые схемы высокого уровня сложности. Предопределенные библиотеки содержат большой набор распространенных электронных компонентов. Параметры компонентов могут быть изменены пользователем в процессе работы над схемой. Модель выбирается из списка компонентов выбранной библиотеки. Программа также позволяет графически построить плату, используя следы или, так называемые, футпринты.

Если схема не вмещается на экране монитора, то можно изменить масштаб рабочего листа. Для этого есть несколько способов. Первый из них заключается в зажатии СКМ и движения мыши вверх по экрану для приближения либо вниз по экрану для отдаления. Второй – в зажатии клавиши Ctrl и прокрутки СКМ. Также можно просмотреть любой участок листа при помощи линеек прокрутки или же движения мыши в нужную сторону с зажатой ПКМ.

Построение схемы оканчивается установкой на схему портов питания GND (заземление) и VCC (питание).

Задание и порядок выполнения работы

Запустить

Altium Designer. Для этого выполнить команды

Файл / Новый /Проект/ Проект платы (ЛК) (

File/New/Project/PCB Project) (рис. 1).

Рис. 1

Если в левой части экрана менеджер проекта не открыт, то выполнить команды: на панели инструментов в нижней части экрана System / Projects. Слева на экране должно появиться окно менеджера проектов Projects.

Далее необходимо сохранить новый проект. Для этого щелкнуть ПК по названию создаваемого проекта и, выполнив команду «Сохранить проект как...» (Save Project As), сохранить проект с названием «Печатная плата», указав номер группы и фамилию (рис. 2).

Затем вновь нажать ПК и выполнить команды «Добавить новый проект /Schematic» (Add New to Project). На рабочем поле открывается форматка для выполнения чертежа схемы (рис. 3).

Аналогичным образом сохранить схему. Щелкнуть ПК по названию проекта«

Sheet1 SchDo». В выпавшем меню выбрать «

Сохранить как...» и в открывшемся окне набрать название «

Схема электрическая принципиальная», указав в этом же окне тип файла

Advanced Schematic binary, нажав ПК (рис. 4).

Рис.2 Рис. 3

Рис.4

В верхнем или нижнем поле форматки в поле «Файл» отображается месторасположения файла на жестком диске ЭВМ.

После этого необходимо добавить файл конструктивного проекта платы. Для чего также, наведя курсор на название проекта, щелкнуть ПК и в выпадающем меню выбрать «Добавить новый проект / PCB» (File/New/PCB) (рис. 2.5).

Рис. 5 Рис. 6,а

На рабочем поле появится черный прямоугольник, ограничивающий контуры платы (рис. 6.а). Проект также надо сохранить. Для этого щелкнуть ПК по

PCB1.

PcbDoc, в выпавшем меню выбрать «

Сохранить как...», назвать его «

Плата печатная», задав расширение

PCB BinaryFiles (рис. 6.б). Справа от названия проекта

Печатная плата.PrjPcb красный листок. Это означает, что проект надо сохранить.

Рис. 6,б

Поэтому выполнить команды «Файл / Сохранить все...» (File/Save All). В результате этого справа в менеджере проекта правее от названий файлов все листки станут серого цвета (не сохраненные файлы в Altium Design помечены красными листками).

Примечание. Если в менеджере проектов напротив названия проекта имеется «*», то необходимо выполнить сохранение всего проекта.

Добавим новые библиотеки в созданный проект.

Для этого, щелкнув ПК по названию проекта, в выпадающем меню выполнить команды «

Добавить новый проект / SchematicLibrary» (рис. 7).

Рис. 7

В левой части экрана в менеджере проекта в меню библиотек Libraries появится подпапка с названием SchematicLibraryDocuments, а справа – рабочее поле редактора условных графических изображений (УГО) электро-радиоэлементов (ЭРЭ).

После этого сохранить создаваемую библиотеку. Для чего щелкнуть ПК по названию последней библиотеки Schlibl.Schlib (рис. 8) и в выпавшем меню выбрать «Сохранить как...» (Save As…)с названием «Библиотека УГО». Тип файлов оставить по умолчанию (рис. 9).

Затем надо добавить в проект библиотеку посадочных мест ЭРЭ. Для этого в менеджере проекта щелкнуть ПК по названию Печатная плата АД.PrjPCB. В выпавшем меню выполнить команды Добавить новый проект / PCB Library (Рис.10).

В результате появилась новая папка PCB LibraryDocuments, в которой есть подпапка PcbLib1.PcbLib1. Именно ее необходимо сохранить. Для чего, щелкнув ПК по названию и выбрав в выпадающем меню «Сохранить как…» (рис. 11),задать ей название «Библиотека посадочных мест» с типом файла по умолчанию (рис. 12).

Рис. 8 Рис. 9

Рис. 11

Рис. 12 Рис. 13

После всех указанных действий необходимо сохранить весь проект. Для этого выполнить команды «Файл / Сохранить всё». В результате всей последовательности выполненных действий получим в менеджере проекта дерево, включающее в себя все файлы проекта (рис. 13).

2.3 Структура отчета и требования к оформлению

1) название и цель работы;

2) ход выполнения и результаты;

3) краткие выводы по результатам работы.

2.4 Контрольные вопросы

1. Каким образом запускается САПР Altium Designer?

2. Назовите основные горячие клавиши системы.

3. Как включается русскоязычная версия системы?

4. Назовите назначение слоев САПР.

5. Как создается проект в САПР Altium Designer?

6. Из каких файлов состоит проект?

7. Как размещены на экране основные меню и панели системы?

8. Поясните назначение кнопок на панелях инструментов.

9. Поясните, какие слои используются в САПР Altium Designer?

10. Как задается шаг сетки?

Лабораторная работа № 3.

ПРАКТИЧЕСКИЕ ИССЛЕДОВАНИЯ КОМБИНАЦИОННЫХ СХЕМ В ПРОГРАММЕ ALTIUM DESIGNER

Цель: обучиться моделированию комбинационных схем в программе Altium Designer.

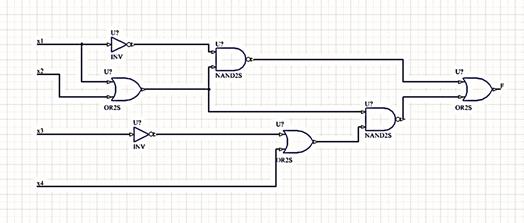

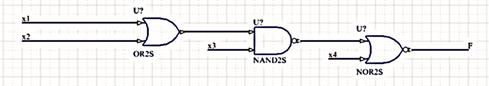

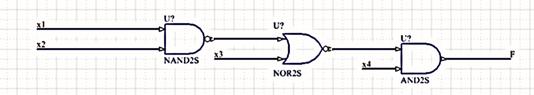

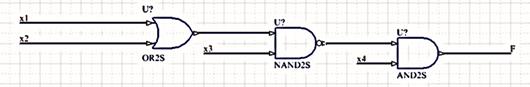

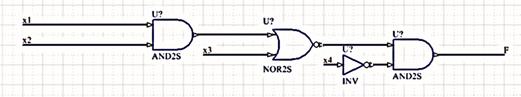

1.

2.

3.

Задание

Согласно номеру в журнале, выбрать задание 1 и 2 из таблицы 3 и 4, выполнить их по рассмотренному выше примеру.

Таблица 3

Таблица 4

3.3 Структура отчета и требования к оформлению

1) Цель работы

2) Условие задания;

3) Результаты работы программы (копия экрана);

4) Выводы.

3.4 Контрольные вопросы

1. Для чего предназначена система схемотического моделирования?

2. При помощи, каких устройств можно управлять операциями?

3. Можно ли изменять масштаб? Как?

4. Что позволяют сделать футпринты?

5. Опишите алгоритм построения и редактирования схем.

Лабораторная работа № 4.

ПРАКТИЧЕСКИЕ ИССЛЕДОВАНИЯ ТРИГГЕРОВ В ПРОГРАММЕ ALTIUM DESIGNER

Цель: обучиться моделированию работы цифровых устройств с элементами памяти в программе Altium Designer.

Задание и порядок выполнения работы

Собрать схему RS-триггера, основанную на элементах И-НЕ. Промоделировать ее, последовательно подавая на входы сигналы 0 и 1.

Этапы работы:

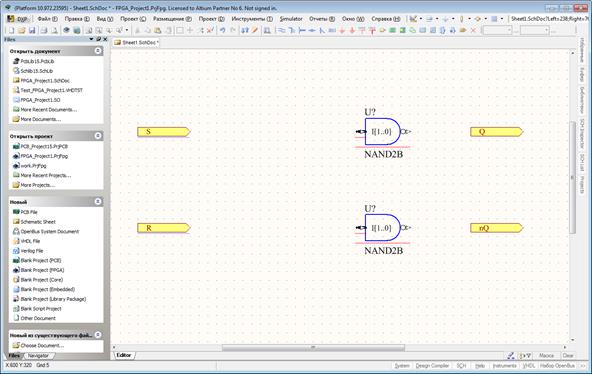

Создание схемы RS-триггера.

Для этого необходимо создать проект ПЛИС, который позволяет моделировать логические устройства. Файл → Новый → Проект → Проект ПЛИС. В нем создать файл Schematic и сохранить проект. Теперь можно начинать непосредственное построение принципиальной схемы работы RS-триггера. Для этого вызвать контекстное меню ПКМ, выбрать пункт Размещение → Часть… В открывшемся окне нажать кнопку Выбрать (Choose). Необходимый нам элемент И-НЕ находится в библиотеке FPGA Generic.IntLib. Вместо привычного нам элемента NAND2S в этой работе мы будем использовать элемент NAND2B, которые логически идентичны (рис. 5). Отличие этих компонентов заключается в способе подачи сигналов на входы компонента: элемент NAND2B имеет шину на входе (от англ. bus – шина), которая позволяет связать 2 (и более) соединения в одну эквивалентную точку.

Рис.5

Разместим два компонента NAND2B на рабочей области документа (рис. 6).

Рис.6

Теперь разместим на схеме входы R и S и выходы Q и  . Для этого выберем в контекстном меню пункт Размещение → Порт (рис. 7).

. Для этого выберем в контекстном меню пункт Размещение → Порт (рис. 7).

Рис.7

Рис.7

Теперь нужно настроить каждый из них. Начнем с левого верхнего входа. Двойным кликом по этому элементу вызовем окно настроек компонента Порт. В графе Имя следует указать название входа. Т.к. это – установочный вход, назовем его S. В графе Тип следует указать значение Input. Нажать ОК (рис. 8).

Рис.8

Перейдем ко второму входу. Вызовем окно настроек порта двойным кликом по нему. Это – вход сброса, поэтому в поле Имя введем значение R, в графе Тип укажем Input.

Осталось настроить выходы триггера. Вызовем окно настроек верхнего правого порта. Укажем его название – Q и тип Output (рис. 9). Для последнего порта укажем Имя nQ и тип Output.

Рис.9

Элементы схемы после проделанных действий (рис. 10)

Рис.10

Кроме уже размещенных на схеме элементов схема RS-триггера также включает в себя инверторы, через которые проходит сигнал, прежде чем попасть в компонент И-НЕ. Разместим на схеме два элемента INV (рис. 11).

Соединим порты входов с соответствующими им инверторами, а компоненты И-НЕ – с соответствующими им выходными портами. Для этого в контекстном меню выберем пункт Размещение → Соединение.

Добавим в схему шины, с помощью которых сигналы будут входить в компоненты И-НЕ. Для этого в контекстном меню выберем пункт Размещение → Шина (рис. 12).

Рис.11

Рис.12

Теперь, чтобы избежать путаницы в линиях соединения, поставим метки цепей, с помощью которых можно реализовать соединение цепи. Для этого в контекстном меню выберем пункт Размещение → Метка цепи и прикрепим ее к каждой линии соединения, которая используется в работе триггера.

Далее необходимо указать название цепи для каждой метки. Начнем с шин, к каждой из которых должно подходить по два сигнала. Пусть к одной из шин поступают сигналы с нулевой и первой цепей, а ко второй – с третьей и четвертой. Тогда в окне настроек каждой из этих меток цепи в поле Имя необходимо указать название I[1..0] и I[3..2] соответственно. Эта запись значит, что к первой шине подключены цепи I0 и I1, а ко второй – I2 и I3. Обратите внимание, что для указания интервала используются две точки. Заметьте также, что интервалы записаны по убыванию – от 1 до 0, от 3 до 2. Следующим шагом необходимо

определить сами цепи I0, I1, I2 и I3 (рис. 13).

Рис.13

Рис.14

Последним штрихом является нумерация компонентов схемы. Для этого необходимо выбрать вкладку Инструменты на панели управления, в ней выбрать пункт Принудительная перенумерация. В появившемся окне нажать ОК (рис. 14).

Моделирование.

Для моделирования полученного устройства необходимо создать файл, в котором будут описаны параметры входных сигналов. Этот файл имеет расширение.VHDTST и создается автоматически (по шаблону) с помощью команды Simulator → Create VDHL Testbench.

Открывшийся документ имеет следующее содержание:

------------------------------------------------------------

-- VHDL Testbenchfor Sheet1

-- 2014 12 6 23 55 6

-- Createdby "EditVHDL"

-- "Copyright (c) 2002 AltiumLimited"

------------------------------------------------------------

Library IEEE;

Use IEEE. std_logic_1164. all;

Use IEEE. std_logic_textio. all;

Use STD. textio. all;

------------------------------------------------------------

------------------------------------------------------------

entity TestSheet1 is

end TestSheet1;

------------------------------------------------------------

------------------------------------------------------------

architecture stimulus of TestSheet1 is

file RESULTS: TEXT open WRITE_MODE is "results.txt";

procedure WRITE_RESULTS(

NQ: std_logic;

Q: std_logic;

R: std_logic;

S: std_logic

) is

variable l_out: line;

Begin

write (l_out, now, right, 15);

write (l_out, NQ, right, 2);

write (l_out, Q, right, 2);

write (l_out, R, right, 2);

write (l_out, S, right, 2);

writeline (RESULTS, l_out);

endprocedure;

component Sheet1

port (

NQ: out std_logic;

Q: out std_logic;

R: in std_logic;

S: in std_logic

);

endcomponent;

signal NQ: std_logic;

signal Q: std_logic;

signal R: std_logic;

signal S: std_logic;

Begin

DUT:Sheet1 portmap (

NQ => NQ,

Q => Q,

R => R,

S => S

);

STIMULUS0: process

Begin

-- insertstimulushere

wait;

endprocess;

WRITE_RESULTS(

NQ,

Q,

R,

S

);

endarchitecture;

------------------------------------------------------------

------------------------------------------------------------

Обратите особое внимание на строки, выделенные красным цветом. Именно здесь указываются процессы, которые будет выполнять собранное устройство. Вместо этих строк введите следующий код:

STIMULUS0: process

Begin

R<= '0';

waitfor 10 ns;

R<= '1';

waitfor 10 ns;

R<= '0';

waitfor 10 ns;

endprocess;

STIMULUS1: process

Begin

S<= '1';

waitfor 10 ns;

S<= '0';

waitfor 20 ns;

endprocess;

Процессы STIMULUS0 и STIMULUS1 будут выполняться одновременно. Заметьте, что в данном коде опущено неустойчивое состояние R = 1, S = 1: первые 10 нс будут подаваться сигналыR = 0, S = 1, следующие 10 нс – R = 1, S = 0, последние 10 нс – R = 0, S = 0. Далее цикл будет повторяться.

Имея схему RS-триггера и файл с его параметрами можно переходить к компиляции проекта и его моделированию, однако прежде, чем это делать, необходимо указать программное средство для моделирования устройства. Для этого перейдем по вкладке Проект, пункт Опции проекта.

В открывшемся окне перейдем на вкладку Моделирование. В поле инструмент выберем Aldec OEM Simulator, а в поле Конфигурации необходимо добавить файл с заданными ранее параметрами. Нажать ОК.

После выполнения этих действий можно переходить к непосредственному моделированию.

Для этого во вкладке Simulator панели управления необходимо выбрать пункт Simulate with Aldec OEM Simulator → STIMULUS of TESTSHEET1 in *название_файла_с_параметрами*.

Важно! Для корректного моделирования устройства необходимо, чтобы имя листа со схемой (расширение.SchDoс) полностью совпадало с названием самого проекта (расширение.PrjFpg). Поэтому, если в вашем проекте эти названия разные, вам необходимо переименовать их, затем заново сгенерировать файл Testbench и заново указать его во вкладке Моделирование окна Опции проекта.

После проделанных действий откроется окно редактирования сигналов. Выберем необходимые входы и выходы, нажмем Применить (рис. 15).

После проделанных действий откроется окно редактирования сигналов. Выберем необходимые входы и выходы, нажмем Применить (рис. 15).

Рис.15

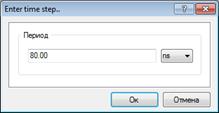

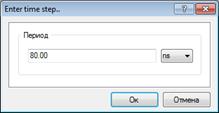

Теперь можно начинать процесс моделирования. Для этого во вкладке Моделирование выберем пункт Run Time Step… В открывшемся окне зададим время 80 нс (рис. 16)

Теперь можно начинать процесс моделирования. Для этого во вкладке Моделирование выберем пункт Run Time Step… В открывшемся окне зададим время 80 нс (рис. 16)

Рис.16

В верхней части рабочего окна моделирования появился график подачи сигналов на входы R и S и соответствующие им сигналы на выходах Q и

В верхней части рабочего окна моделирования появился график подачи сигналов на входы R и S и соответствующие им сигналы на выходах Q и  (рис. 17).

(рис. 17).

Рис.17

Обратите внимание, что сигналы на 0 нс и 30 нс идентичны, т.к. именно с этого момента цикл начинает повторяться.

Для проверки работы собранного устройства необходимо заполнить таблицу входных и выходных сигналов и сравнить ее с таблицей значений RS-триггера. Если таблицы одинаковы, значит, работа выполнена правильно и созданное устройство действительно является триггером типа RS. Проверим это.

Таблица значений RS-триггера: Таблица полученных значений:

Заметьте, что с написанными ранее параметрами в файле Testbench нельзя полностью заполнить таблицу. Это связано с тем, что сигналы образуют пары R = 0, S = 1, затем R = 1, S = 0, и R = 0, S = 0, т.е. 01, 10, 00, дальше цикл повторяется: 01, 10, 00, 01, 10, 00, 01, 10… Для полного заполнения таблицы необходимы все возможные варианты последовательной смены сигналов, например, в нашей схеме после пары 01 не появится пара 00, после 00 не появится 10, а после 10 не появится 01.

4.3 Структура отчета и требования к оформлению

1. Цель работы

2. Условие задания;

3. Результаты работы программы (копия экрана);

4. Выводы.

1.

2.

3.

4.

4.1.

4.2.

4.3.

4.4 Контрольные вопросы

1. Что такое триггер?

2. Какие входы может иметь триггер?

3. Опишите устройство RS-триггера.

4. Назовите главное отличие JK-триггера.

5. Зависит ли состояние D-триггера от уровня сигнала на входе?

6. Каков главный принцип работы T-триггера?

Лабораторная работа № 5.

Порядок выполнения работы

1. Через Кнопку Пуск в меню Программы загрузить САПР Altium Designer.

2. Открыть редактор схем Schematic.

3. Установить начальные настройки рабочего поля.

4. Создать библиотеку УГО ЭРЭ.

5. Создать УГО элементов НЕ-И и 2И-НЕ.

6. Сохранить результат.

5.4 Структура отчета и требования к оформлению

4. Цель работы

5. Условие задания;

6. Результаты работы программы (копия экрана);

7. Выводы.

5.5 Контрольные вопросы

1. Каким образом выполняются основные настройки редактора УГО?

2. Как настраиваться шаг, вид и цвет сетки?

3. Как задается тип шрифта?

4. Каким образом задаются основные примитивы системы?

5. Как изменяется масштаб изображения.

6. Каким образом задаются основные параметры входных и выходных выводов ЭРЭ?

7. Каким образом задается на экране видимая сетка в виде линий или точек?

8. Как задаются основные параметры выводов питания и корпуса ЭРЭ?

9. Как пополнить содержимое библиотеки УГО новыми элементами?

10. Какой порядок присвоения элементам схемы позиционных обозначений?

11. Каков порядок создания УГО элемента НЕ-И?

12. Каков порядок создания УГО элемента 2И-НЕ?

13. Каким образом выполняется вращение УГО элементов?

14. Каким образом выполняется прорисовка контура УГО?

15. Какими командами выполняется размещение текстовой строки?

16. Какими командами выполняется сохранение результатов проектирования?

Лабораторная работа № 6.

Порядок выполнения работы

1. Через Кнопку Пуск в меню Программы загрузить САПР Altium Designer.

2. Открыть редактор PCB и создать файл библиотеки посадочных мест.

3. Выполнить начальные

(младший разряд),

(младший разряд),  ,

,  ,

,  ,

,  ,

,  .

.

. Для этого выберем в контекстном меню пункт Размещение → Порт (рис. 7).

. Для этого выберем в контекстном меню пункт Размещение → Порт (рис. 7). Рис.7

Рис.7

После проделанных действий откроется окно редактирования сигналов. Выберем необходимые входы и выходы, нажмем Применить (рис. 15).

После проделанных действий откроется окно редактирования сигналов. Выберем необходимые входы и выходы, нажмем Применить (рис. 15). Теперь можно начинать процесс моделирования. Для этого во вкладке Моделирование выберем пункт Run Time Step… В открывшемся окне зададим время 80 нс (рис. 16)

Теперь можно начинать процесс моделирования. Для этого во вкладке Моделирование выберем пункт Run Time Step… В открывшемся окне зададим время 80 нс (рис. 16) В верхней части рабочего окна моделирования появился график подачи сигналов на входы R и S и соответствующие им сигналы на выходах Q и

В верхней части рабочего окна моделирования появился график подачи сигналов на входы R и S и соответствующие им сигналы на выходах Q и