Равносильные преобразования логических формул имеют то же назначение, что и преобразования формул в обычной алгебре. Они служат для упрощения формул или приведения их к определённому виду путем использования основных законов алгебры логики.

Под упрощением формулы, не содержащей операций импликации и эквиваленции, понимают равносильное преобразование, приводящее к формуле, которая либо содержит по сравнению с исходной меньшее число операций конъюнкции и дизъюнкции и не содержит отрицаний неэлементарных формул, либо содержит меньшее число вхождений переменных.

Некоторые преобразования логических формул похожи на преобразования формул в обычной алгебре (вынесение общего множителя за скобки, использование переместительного и сочетательного законов и т.п.), тогда как другие преобразования основаны на свойствах, которыми не обладают операции обычной алгебры (использование распределительного закона для конъюнкции, законов поглощения, склеивания, де Моргана и др.).

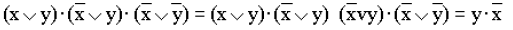

Покажем на примерах некоторые приемы и способы, применяемые при упрощении логических формул:

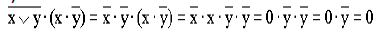

1) (законы алгебры логики применяются в следующей последовательности: правило де Моргана, сочетательный закон, правило операций переменной с её инверсией и правило операций с константами);

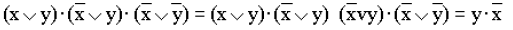

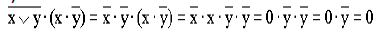

2) (применяется правило де Моргана, выносится за скобки общий множитель, используется правило операций переменной с её инверсией);

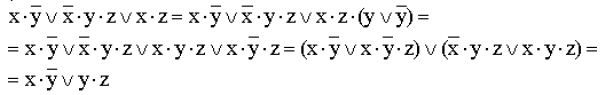

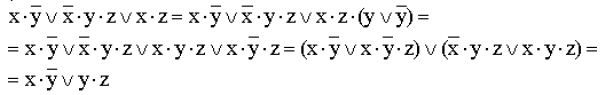

3) (повторяется второй сомножитель, что разрешено законом идемпотенции; затем комбинируются два первых и два последних сомножителя и используется закон склеивания);

4) (вводится вспомогательный логический сомножитель (); затем комбинируются два крайних и два средних логических слагаемых и используется закон поглощения);

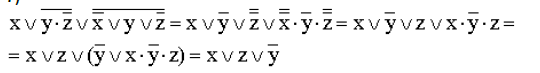

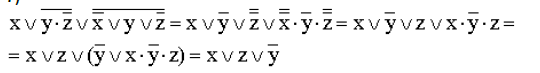

5) (сначала добиваемся, чтобы знак отрицания стоял только перед отдельными переменными, а не перед их комбинациями, для этого дважды применяем правило де Моргана; затем используем закон двойного отрицания);

6) (выносятся за скобки общие множители; применяется правило операций с константами);

7) (к отрицаниям неэлементарных формул применяется правило де Моргана; используются законы двойного отрицания и склеивания);

Логические элементы компьютера: конъюнктор, дизъюнктор, инвертор, триггер,

Сумматор.

Логический элемент компьютера - это часть электронной логической схемы, которая реализует элементарную логическую функцию. Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и другие (называемые также вентилями), а также триггер. С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем. Работу логических элементов описывают с помощью таблиц истинности. Таблица истинности это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний.

Логический элемент «И» (конъюнктор) реализует операцию конъюнкции.

Логический элемент «ИЛИ» (дизъюнктор) реализует операцию дизъюнкции.

Логический элемент «НЕ» (инвертор) — реализует операцию логического отрицания.

Сумма́тор — в кибернетике - устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов; устройство, производящее операцию сложения.

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов.

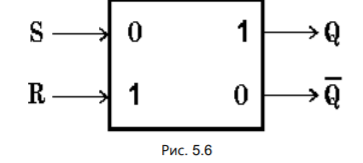

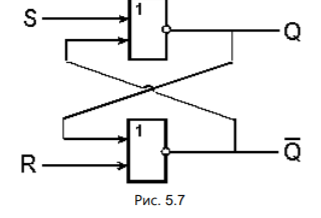

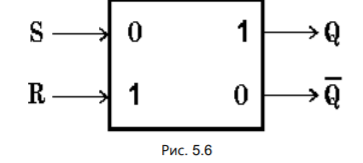

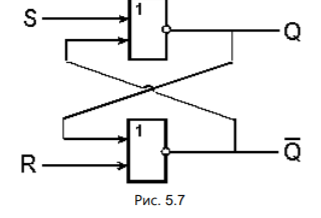

Триггер - это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое - двоичному нулю. Термин триггер происходит от английского слова trigger - защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flоp, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот. Самый распространённый тип триггера - так называемый RS-триггер (S и R, соответственно, от английских set - установка, и reset - сброс). Условное обозначение триггера - на рис. 5.6. Он имеет два симметричных входа S и R и два симметричных выхода Q и, причем выходной сигнал Q является логическим отрицанием сигнала. На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов (). Наличие импульса на входе будем считать единицей, а его отсутствие - нулем. На рис. 5.7 показана реализация триггера с помощью вентилей ИЛИ-НЕ и соответствующая таблица истинности.

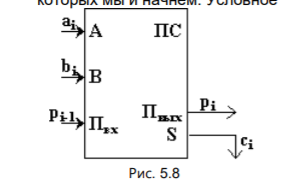

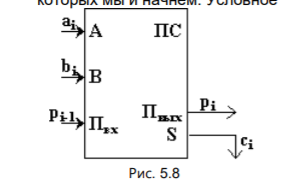

Сумматор - это электронная логическая схема, выполняющая суммирование двоичных чисел. Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины. Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядный двоичных чисел, представляет собой комбинацию одноразрядных сумматоров, с рассмотрения которых мы и начнём. Условное обозначение одноразрядного сумматора на рис. 5.8.

При сложении чисел А и B в одном i-ом разряде приходится иметь дело с тремя цифрами:

1. цифра аi первого слагаемого;

2. цифра bi второго слагаемого;

3. перенос pi–1 из младшего разряда.

В результате сложения получаются две цифры: 1. цифра ci для суммы; 2. перенос pi из данного разряда в старший. Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами, работа которого может быть описана следующей таблицей истинности: