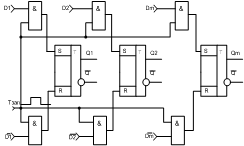

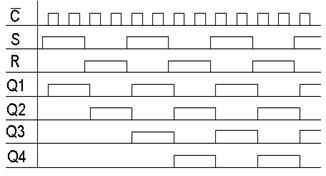

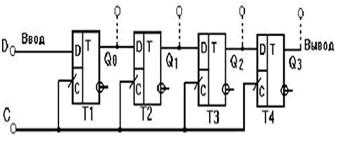

На Рис.4.9. представлена схема (а) и диаграмма (б) работы данного регистра.

|

|

| а)

| б)

| |

|

Рис.4.9. Запись информации по установочному входу R с предварительной

установкой в «1» всех триггеров регистра

| |

При записи парафазным кодом прямой код числа подается на вход S, обратный код на R.

Достоинством данной схемы является отсутствие сигнала предварительной установки регистра.

Недостатком то, что необходим прямой и обратный код числа. Если устройство работает только с прямым кодом, то для формирования обратного кода необходимо в схеме предусмотреть m инверторов.

Тактируемые регистры

Принцип действия регистров, срабатывающих по фронту тактового сигнала, ничем не отличается от принципа действия D-триггера.

По положительному фронту тактового сигнала С каждый из выходов регистра устанавливается в тот уровень, который был в этот момент на соответствующем данному выходу входе D, и сохраняется таковым до прихода следующего положительного фронта сигнала С. То есть если триггер запоминает один сигнал (один двоичный разряд, один бит), то регистр запоминает сразу несколько (4, 6, 8, 16) сигналов (несколько разрядов, битов). Память регистра сохраняется до момента выключения питания схемы.

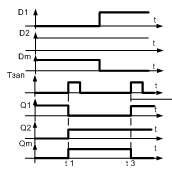

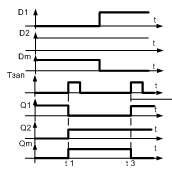

На Рис.4.11. представлена схема регистра на D триггерах, в котором данные в прямом коде подаются на входы D1,D … Dm.

Запись информации осуществляется фронтом сигнала Тзап (тактовый командный импульс) одновременно поступающего на входы С всех триггеров.

|

|

Рис.4.11. Запись информации параллельным кодом

|

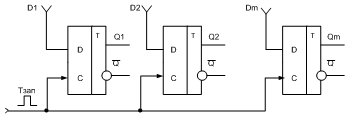

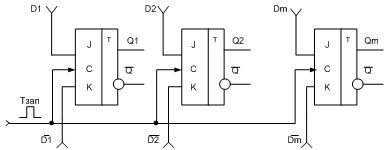

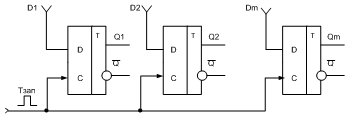

На Рис.4.12. представлена схема регистра на JK триггерах. В данной схеме данные подаются парафазным кодом (прямой код D1,D … Dm – на вход J, обратный кода – на вход К).

|

|

Рис.4.12. Запись информации парафазным кодом

|

Изменение хранящейся информации в регистре памяти (запись новой информации) осуществляется после установки на входах D0... Dm новой цифровой комбинации (информации) при поступлении определенного уровня (регистр на асинхронных триггерах или запись осуществляется по установочным входам триггера) или фронта синхросигнала (синхроимпульса) Тзап=С на вход «С» регистра (синхронные триггера с записью по информационным входам).

Регистры сдвига

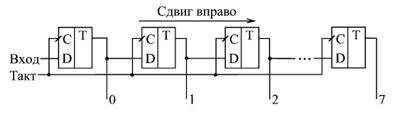

Регистры сдвига или сдвиговые регистры (англ. shift register) представляют собой, последовательно соединенную цепочку триггеров.

Т.е. в сдвиговых регистрах все триггеры соединены в последовательную цепочку (выход каждого предыдущего триггера соединен со входом D следующего триггера). Тактовые входы всех триггеров (С) объединены между собой. В результате такой триггер может рассматриваться как линия задержки, входной сигнал которой последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С. Информационные входы и выходы триггеров могут быть выведены наружу, а могут и не выводиться - в зависимости от функции, выполняемой регистром.

Основной режим их работы - это сдвиг разрядов кода, записанного в эти триггеры, То есть по тактовому сигналу содержимое каждого предыдущего триггера переписывается в следующий по порядку в цепочке триггер. Код, хранящийся в регистре, с каждым тактом сдвигается на один разряд в сторону старших разрядов или в сторону младших разрядов, что и дало название регистрам данного типа.

На схемах символом регистра служат буквы RG. Для регистров сдвига указывается также направление сдвига:

· → вправо (основной режим, который есть у всех сдвиговых регистров);

· ← влево (этот режим есть только у некоторых, реверсивных сдвиговых регистров);

· ↔ реверсивный (двунаправленный), т. е. записанную информацию можно сдвигать по линейке триггеров вправо или влево. Для включения режима сдвига предусматривают специальный управляющий вход.

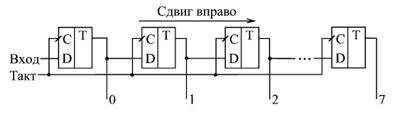

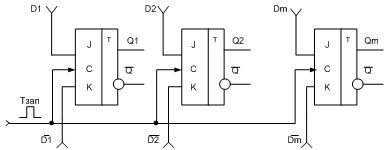

Направление сдвига отражают внутреннюю структуру регистров сдвига (Рис. 4.14) и перезапись сигналов последовательно по цепочке триггеров. При этом триггеры, вполне естественно, нумеруются слева направо, например, от 0 до 7 (или от 1 до 8) для 8-разрядных регистров. В результате сдвиг информации регистром вправо представляет собой сдвиг в сторону разрядов, имеющих большие номера, а сдвиг информации регистром влево - это сдвиг в сторону разрядов, имеющих меньшие номера.

Однако, как известно, в любом двоичном числе слева расположены старшие разряды, а справа - младшие разряды. Поэтому сдвиг двоичного числа вправо будет сдвигом в сторону младших разрядов, а сдвиг влево - сдвигом в сторону старших разрядов. О такой особенности необходимо помнить разработчику цифрового прибора.

Рис. 4.14. Направление сдвига в сдвиговых регистрах

Регистры сдвига могут выполнять функции хранения и преобразования информации.

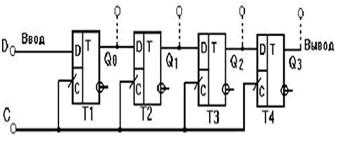

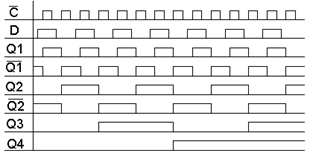

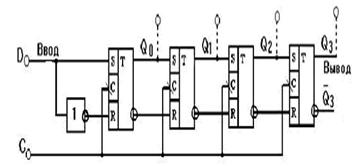

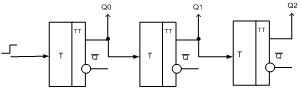

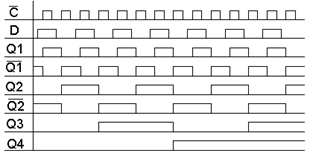

Регистры сдвига чаще все6го реализуются на D-триггерах (Рис.4.15, а) или на RS-триггерах (Рис.4.15, б), где для ввода информации в первый разряд включается инвертор (первый разряд представляет собой D-триггер).

Следует отметить, что все регистры сдвига строятся на базе двухступенчатых триггеров или синхронизируемых фронтом синхроимпульса.

Регистры сдвига могут быть построены и на триггерах одноступенчатой структуры. В этом случае в каждом разряде регистра нужно использовать два триггера, которые управляются двумя сдвинутыми во времени тактовыми импульсами. Если бы в регистре были применены одноступенчатые триггеры по одному на разряд, то правило работы регистра было бы нарушено: при первом же импульсе сдвига информация, записавшись в первый разряд, перешла бы во второй, затем в третий и т.д.

Разрядность регистров сдвига, как и у регистров хранения, определяется количеством триггеров, входящих в их состав.

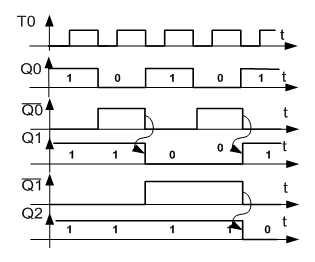

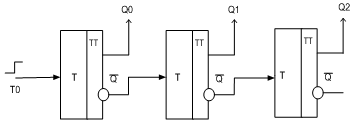

Работу регистра сдвига рассмотрим на примере схемы, приведенной на Рис. Рис.4.15.

Можно предположить, что в начале все триггеры регистра находятся в состоянии логического нуля, т.е. Q0=0, Q1=0, Q2=0, Q3=0. Если на входе D-триггера Т1 имеет место логический 0, то поступление синхроимпульсов на входы «С» триггеров не меняет их состояния.

Как следует из Рис.4.15, синхроимпульсы поступают на соответствующие входы всех триггеров регистра одновременно и записывают в них то, что имеет место на их информационных входах. На информационных входах триггеров Т2, Т3, Т4 - уровни логического «0», т.к. информационные входы последующих триггеров соединены с выходами предыдущих триггеров, находящихся в состоянии логического «0», а на вход «D» первого триггера, по условию примера, подается «0» из внешнего источника информации.

При подаче на вход «D» первого триггера «1», с приходом первого синхроимпульса, в этот триггер запишется «1», а в остальные триггеры - «0», т.к. к моменту поступления фронта синхроимпульса на выходе триггера Т1 «ещё» присутствовал логический «0». Таким образом, в триггер Т1 записывается та информация (тот бит), которая была на его входе «D» в момент поступления фронта синхроимпульса и т.д.

При поступлении второго синхроимпульса логическая «1», с выхода первого триггера, запишется во второй триггер, и в результате происходит сдвиг первоначально записанной «1» с триггера Т1 в триггер Т2, из триггера Т2 в триггер Т3 и т.д.. Таким образом, производится последовательный сдвиг поступающей на вход регистра информации (в последовательном коде) на один разряд вправо в каждом такте синхроимпульсов.

Суммирующие счетчики

Процесс двоичного счета может быть описан посредством таблицы последовательности чисел, в которой каждое число соответствует определенному состоянию счетчика. Состояние 3-х разрядного суммирующего счетчика описывается таблицей 5.1.

Исходным состоянием такого счетчика является нулевое состояние.

На вход счетчика поступает последовательность счетных сигналов Т0.

Из таблицы следует, что с приходом очередного счётного импульсТ0 к содержимому счётчика прибавляется единица. При этом увеличивается на единицу номер состояния, являющийся десятичным эквивалентом соответствующего данному состоянию двоичного числа.

Изменение состояния каждого последующего разряда происходит при изменении состояния предыдущего разряда от 1 к 0. Это означает, что всякий раз, когда данный триггер в счётчике переходит из состояния 1 в состояние 0, на его выходе должен формироваться сигнал переноса, вызывающий срабатывание следующего триггера. Если же данный триггер переходит из 0 в 1, то сигнала переноса на его выходе не должно быть.

Из таблицы.5.1 также следует, что триггер первого, самого младшего разряда, должен менять своё состояние каждый раз с приходом очередного счётного импульса, а триггер каждого последующего разряда - вдвое реже триггера предыдущего разряда.

Процесс двоичного счета суммирующего счетчика

| Номер состояния

| Q2

| Q1

| Q0

| Т0

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

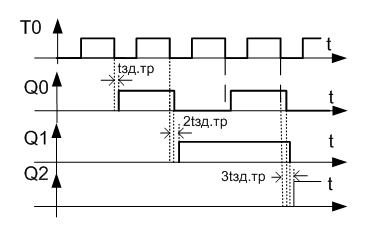

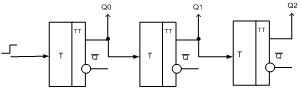

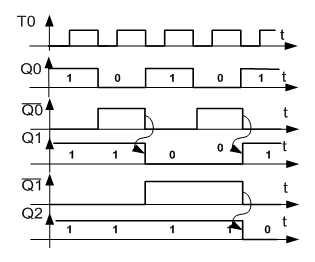

Описанные порядок смены состояний счётчика и характер процесса их установления могут быть реализованы, если счётчик будет построен на последовательно соединённых Т-триггерах.

Каждый последующий разряд при этом будет переключаться сигналом переноса, формируемым на выходе предыдущего разряда.

Счётные импульсы должны быть поданы на вход триггера самого младшего разряда.

Счётчики, построенные таким образом, получили название счётчиков с последовательным переносом.

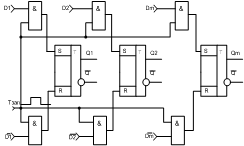

Схема суммирующего счетчика с последовательным переносом на Т – триггерах приведена на Рис.5.2 а.

Вычитающие счетчик

Вычитающий счётчик с последовательным переносом имеет обратный порядок смены состояний: с приходом очередного счётного импульса содержащееся в счётчике число уменьшается на единицу (табл.5.2).

Процесс двоичного счета вычитающегоо счетчика

| Номер состояния

| Q2

| Q1

| Q0

| Т0

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

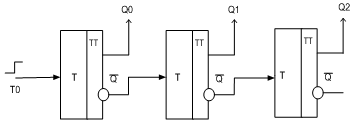

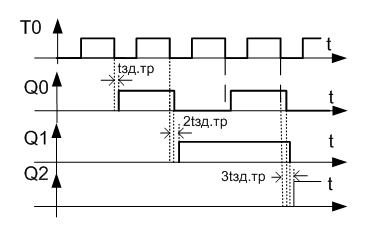

Другая особенность вычитающего счётчика - триггер каждого последующего разряда переключается в противоположное состояние при изменении уровня на выходе триггера предыдущего разряда от 0 к 1, т.е. при сигнале займа, обратном сигналу переноса в суммирующем счётчике.

Строится вычитающий счётчик так же, как суммирующий, но с тем отличием, что со входом каждого последующего триггера в отличие от Рис.5.2.а соединяется инверсный выход предыдущего триггера.

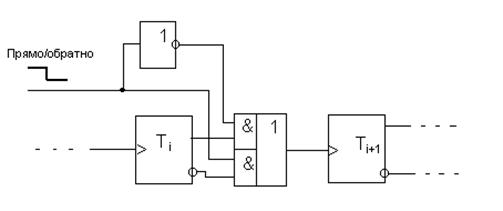

Кроме суммирующих и вычитающих счетчиков имеются реверсивные счетчики.

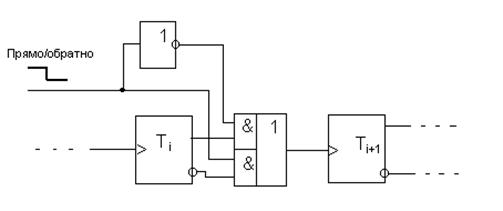

Реверсивные счетчики изменяют направление счета под воздействием управляющего сигнала. На Рис. 5.2 и 5.3 видно, что счетчики прямого и обратного счета различаются лишь точкой съема сигнала, подаваемого с предыдущего разряда на последующий. Если управляющий сигнал перестраивает межразрядные связи, перенося точку съема сигнала с одного выхода триггера на другой, то реализуется схема реверсивного счетчика (Рис.5.4).

|

| Рис. 5.4. Реверсивный счетчик

|

У асинхронных счетчиков (или счетчиками с последовательным переносом) каждый триггер переключается выходным сигналом предыдущего триггера. Временные состязания сигналов в таких счетчиках отсутствуют, поскольку триггеры переключаются поочередно, один за другим. Последовательные счетчики отличаются простотой схемы, но обладают низким быстродействием.

Сумматор

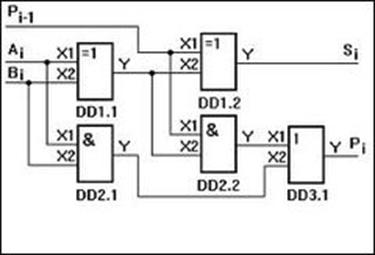

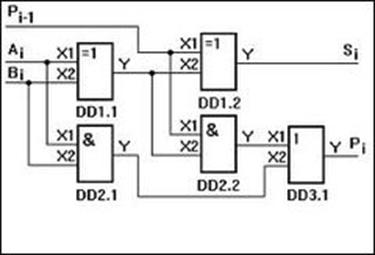

Cхема, которая обеспечивает сложение двух однобитных чисел А и В называется полусумматором. Полусумматор имеет 4 сигнальных линии: два входа для сигналов, представляющих одноразрядные двоичные числа А и В, и два выхода: сумма А и В по модулю 2 (S) и сигнал переноса (P). При этом S наименее значимый бит, а P наиболее значимый бит.

Объединив два полусумматора и добавив дополнительную схему ИЛИ, можно создать полный сумматор с дополнительным входом Pi-1 (на рисунке 1), который принимает сигнал переноса из предыдущей схемы.

Схема полного сумматора может быть использована в качестве "строительных блоков" для построения схем многоразрядных сумматоров, путём добавления одноразрядных полных сумматоров. Для каждой цифры, которую схема должна быть в состоянии обрабатывать, используется один полный сумматор.

Двоичный одноразрядный полный сумматор является полной тринарной (трёхоперандной) двоичной логической функцией с бинарным (двухразрядным) выходом. Все три операнда и оба выходных разряда однобитные.

Может быть построен как тринарная (трёхоперандная) двоичная функция с бинарным выходом, но, для уменьшения аппаратных затрат, обычно строится трёхступенчатым, состоящим из трёх узлов: двух полусумматоров, которые являются полными бинарными (двухоперандными) двоичными логическими функциями с унарным выходом и логического элемента «2ИЛИ».