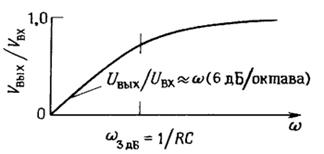

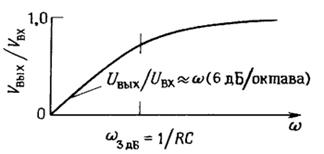

RC-фильтры

Фильтры высоких частот.

Фильтры высоких частот. Согласно закону Ома для комплексных величин,

I = U вх /Z полн = U вх /R - (j/ωC) = U вх [R + j/ωC)]/R 2 + 1/ω 2 C 2.

U вых = IZ R = IR = U вх [R + (j/ωС)R]/R 2 +1/ω 2 C 2.

Чаще всего нас интересует не фаза, а амплитуда Uвых:

U вых = (U вых U вых* ) 1/2 = U вх R/[R 2 + (1/ω 2 C 2 )] 1/2.

Итак, если не принимать во внимание сдвиг фаз, а рассматривать только модули комплексных амплитуд, то «отклик» схемы будет определяться следующим образом:

U вых = U вх R/[R 2 + (1/ω 2 C 2 )] 1/2 = U вх 2πƒRC/[1 + (2πƒRC)] 1/2.

Фильтры низких частот. Если поменять местами R и С (рис. 1.58), то фильтр будет вести себя противоположным образом в отношении частоты. Можно показать, что Uвых = [1/1 + ω2R2С2)1/2] Uвх. Такой фильтр называют фильтром низких частот. Точка -3 дБ на характеристике фильтра находится на частоте ƒ = 1/2πRC.

Полосовой фильтр

Полосовой фильтр получается соединением фильтров верхних и нижних частот, он пропускает частоты в определенном диапазоне

Полосовой фильтр получается соединением фильтров верхних и нижних частот, он пропускает частоты в определенном диапазоне

Усилители мощности

Электронный усилитель — усилитель электрических сигналов, в усилительных элементах которого используется явление электрической проводимости в газах, вакууме иполупроводниках. Электронный усилитель может представлять собой как самостоятельное устройство, так и блок (функциональный узел) в составе какой-либо аппаратуры —радиоприёмника, магнитофона, измерительного прибора и т. д.

Структура усилителя

§ Усилитель представляет собой в общем случае последовательность каскадов усиления (бывают и однокаскадные усилители), соединённых между собой прямыми связями

§ В большинстве усилителей кроме прямых присутствуют и обратные связи (межкаскадные и внутрикаскадные). Отрицательные обратные связи позволяют улучшить стабильность работы усилителя и уменьшить частотные и нелинейные искажения сигнала. В некоторых случаях обратные связи включают термозависимые элементы (термисторы, позисторы) — для температурной стабилизации усилителя или частотнозависимые элементы — для выравнивания частотной характеристики

§ Некоторые усилители (обычно УВЧ радиоприёмных и радиопередающих устройств) оснащены системами автоматической регулировки усиления (АРУ) или автоматической регулировки мощности (АРМ). Эти системы позволяют поддерживать приблизительно постоянный средний уровень выходного сигнала при изменениях уровня входного сигнала.

§ Между каскадами усилителя, а также в его входных и выходных цепях, могут включаться аттенюаторы или потенциометры — для регулировки усиления, фильтры — для формирования заданной частотной характеристики и различные функциональные устройства — нелинейные и др.

§ Как и в любом активном устройстве в усилителе также присутствует источник первичного или вторичного электропитания (если усилитель представляет собой самостоятельное устройство) или цепи, через которые питающие напряжения подаются с отдельного блока питания.

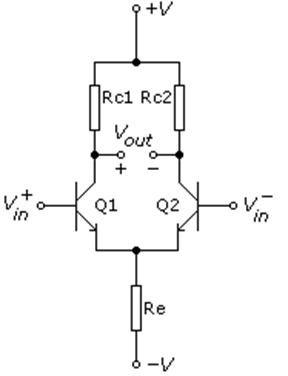

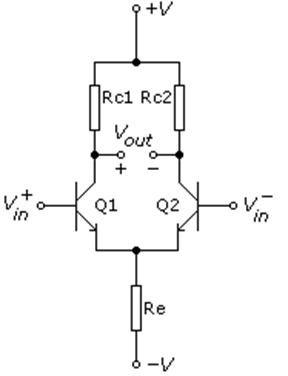

Дифференциальные усилители

Дифференциа́льный усили́тель — электронный усилитель с двумя входами, выходной сигнал которого равен разности входных напряжений, умноженной на константу. Применяется в случаях, когда необходимо выделить небольшую разность напряжений на фоне значительной синфазной составляющей.

Выходной сигнал дифференциального усилителя может быть как однофазным, так и дифференциальным. Это определяется схемотехникой выходного каскада.

Дифференциальный усилитель необходим в случаях, когда информацию несёт не абсолютное значение напряжения в некоторой точке (относительноуровня заземления), а разность напряжений между двумя точками. Характерным примером является резистивный датчик тока, включенный последовательно с исследуемой цепью.

Следует использовать дифференциальные усилители всегда, когда возможно наличие синфазных помех в сигнале. Например, при измерении электрических потенциалов, снимаемых с определённых точек живого организма: при снятии электрокардиограммы, электроэнцефалографии и подобных методах исследования. Обычно необходимо также использовать специальные линии передачи сигналов, например, экранированную двухпроводную линию для передачи сигнала с микрофона (применяется, например, в линиях с разъёмом XLR).

Классификация ОУ

По типу элементной базы

§ На полевых транзисторах

§ На биполярных транзисторах

§ На электронных лампах (устарели)

Инвертирующий усилитель

Рассмотрим схему на рис. 3. Проанализировать ее будет нетрудно, если вспомнить сформулированные правила:

1. Потенциал точки B равен потенциалу земли, следовательно, согласно правилу I, потенциал точки A также равен потенциалу земли.

2. Это означает, что: а) падение напряжения на резисторе R 2 равно U вых, б) падение напряжения на резисторе R 1 равно U вх.

3. Воспользовавшись теперь правилом II, получим U вых/ R 2 = - U вх/ R 1, или коэффициент усиления по напряжению = U вых/ U вх = R 2/ R 1. Позже вы узнаете, что чаще всего точку B лучше заземлять не непосредственно, а через резистор. Однако сейчас это не имеет для вас значения.

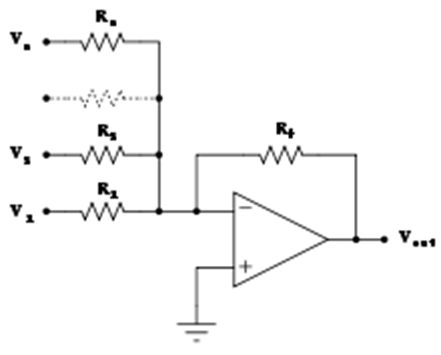

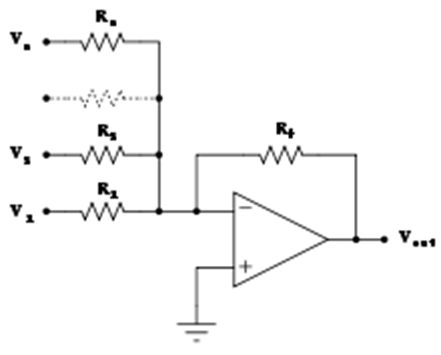

Суммирующий усилитель на ОУ

Суммирует (с весом) несколько напряжений. Сумма на выходе инвертирована, то есть все веса отрицательны.

§ Если  , то

, то

§ Если  , то

, то

§ Выход инвертирован

§ Входной импеданс n -го входа равен  (Поскольку

(Поскольку  является виртуальной землей)

является виртуальной землей)

14Интегрирующий усилитель (интегратор) – это такой усилитель (рис. 3.8), выходное напряжение которого пропорционально интегралу от входного напряжения. Его можно получить заменой активного сопротивления обратной связи R ОС в масштабном усилители реактивным элементом (конденсатором С).

Рисунок 3.8 – Интегрирующий усилитель на базе ОУ

Во время переходного процесса в цепи R 1, С, протекающего при подаче на вход схемы сигнала U вх, усилитель работает в линейном режиме. Этому режиму соответствует процесс интегрирования. Если принять, что КU →∞, то в схеме существует полная отрицательная обратная связь и U вх=0. Поэтому ток, протекающий через резистор R 1, определяется по формуле

Поскольку ток во вход идеального ОУ не втекает, то и напряжение на конденсаторе или, что то же самое, на выходе усилителя (U вх =0) определяется выражением:

Если к входу ОУ приложить напряжение в виде скачка с постоянной амплитудой U вх, то

где R 1 C – постоянная времени интегратора (τ = R 1 C).

В соответствии с этим уравнением интегрирующий усилитель может быть использован для получения линейно изменяющегося напряжения, что применяется при проектировании высокоточных генераторов пилообразного напряжения на ОУ.

Дифференциатор

Дифференциатор используется тогда, когда надо получить выходной сигнал, пропорциональный скорости изменения входного.

Идеальный дифференциатор

Рисунок 5. Схема инвертирующего дифференциатора на ОУ.

Для идеального ОУ напряжение на конденсаторе Uc равно входному напряжению Uвх, а ток через сопротивление обратной связи R равен току через конденсатор C, т.е.

ίR = – ίc. В этом случае выходное напряжение

Uвых = R·ίR = – ίc·R=–R·C(dUвх/dt).

Пример дифференцирования. Подадим на вход сигнал треугольной формы:

Рисунок 6. Временные диаграммы напряжения на входе и на выходе

дифференциатора.

Выходной сигнал - это прямоугольное напряжение, частота которого равна частоте входного сигнала

Таким образом, любому линейно изменяющемуся сигналу на входе дифференциатора соответствует постоянный выходной сигнал, величина которого пропорциональна крутизне входного сигнала; этот выходной сигнал остается постоянным в течение всего времени, пока входной сигнал сохраняет постоянный наклон.

Реальный дифференциатор

Рисунок 7. Инвертирующий дифференциатор на ОУ.

Резистор Rк и емкость C образуют дифференцирующую цепочку с частотой среза fc1 = 1/2π∙Rк∙С.

Резистор R и емкость Cк образуют интегрирующую цепочку с частотой среза

Fc2 = 1/2π∙R∙Ск.

Типичная логарифмическая амплитудно-частотная характеристика (ЛАЧХ) реального дифференциатора на ОУ показана на рисунке 8.

Рисунок 8. ЛАЧХ реального дифференциатора

Частотная характеристика реального дифференциатора представляет собой частотную характеристику полосового фильтра с подъемом и спадом 20 дб/декада и с коэффициентом усиления, большим единицы.

В области частот меньших частоты среза fc1 = 1/2π∙Rк∙С возможно дифференциирование входного напряжения.

В полосе частот от fc1 до fc2 реальный дифференциатор можно рассматривать как инвертирующий усилитель с коэффициентом усиления KU = - R/Rк.

В области частот больших частоты среза fc2 = 1/2π∙R∙Ск возможно интегрирование входного напряжения.

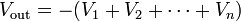

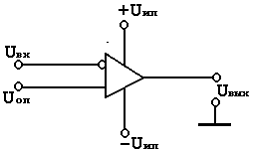

Компараторы

Компараторы предназначенные для сравнения величин двух аналоговых сигналов.

Рис.1. Схема компаратора

На один вход компаратора подается опорное напряжение Uоп, а на другой входной сигнал с напряжением Uвх.

Дифференциальное напряжение Uдиф = Uоп – Uвх.

Если Uвх >Uоп, то Uдиф < 0 и выходное напряжение будет отрицательным и равно Uвых = - Uвых макс.

Если Uвх <Uоп, то Uдиф > 0 и выходное напряжение будет положительным и равно Uвых = + Uвых макс.

Когда входной сигнал в процессе изменения становится больше или меньше опорного, то напряжение на выходе компаратора изменяется скачкообразно.

Рисунок 9. Временная диаграмма работы компаратора.

Активные фильтры на ОУ

Интегрирующие усилители

Интеграторы

Интеграторы предназначены для интегрирования во времени электрических входных сигналов.

Идеальный интегратор

Рисунок 1. Схема инвертирующего интегратора на ОУ.

Для идеального ОУ для входного тока ίR и тока через конденсатор ίC справедливо следующее равенство

ίC = − C(dUвых/dt) = Uвх/R = ίR.

Решая это выражение относительно dUвых получим:

dUвых = −(1/RC)Uвхdt,

Интегрируя последнее уравнение, найдем выходное напряжение:

Uвых =

Постоянный член Uвых(0) определяет начальное условие интегрирования.

Пример интегрирования. На вход интегратора подается периодический сигнал прямоугольной формы

Рисунок 2. Временные диаграммы напряжения на входе и на выходе интегратора.

Так как сигнал периодический, то для описания выходного напряжения достаточно рассмотреть один полный период. Выходной напряжение можно записать как функцию времени

,

,

После интегрирования получаем наклонную прямую на каждом полупериоде. Пределами интегрирования в этой формуле являются моменты времени t1 и t2

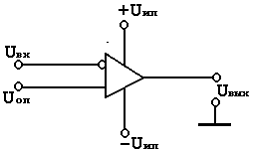

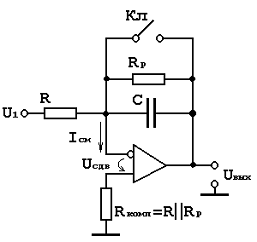

Реальный интегратор

Рисунок 3. Инвертирующий интегратор на ОУ с резистором Rp в цепи обратной связи.

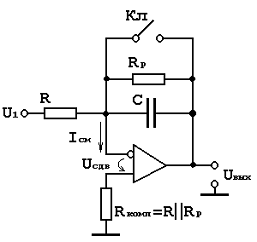

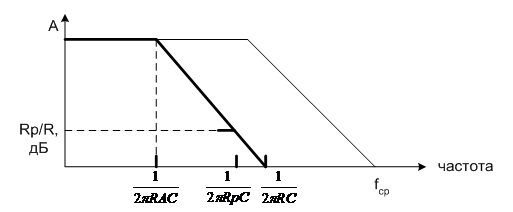

Типичные логарифмические амплитудно-частотные характеристики (ЛАЧХ) интеграторов на ОУ с шунтирующим резистором в цепи обратной связи RР и без него показаны на рисунке 4.

Рисунок 4. Логарифмические амплитудно-частотные характеристики интеграторов: тонкая сплошная линия – ЛАЧХ ОУ, жирная линия –ЛАЧХ идеального интегратора, штрихпунктирная линия – ЛАЧХ реального интегратора с резистором Rp в цепи обратной связи.

Частотная характеристика реального интегратора представляет собой частотную характеристику фильтра НЧ со спадом 20дб/декада и с коэффициентом усиления, большим единицы.

Для идеального интегратора (рисунок 1) коэффициент усиления на низких частотах

равен А (коэффициент усиления ОУ) и частота среза определяется по формуле:

.

.

Для реального интегратора (рисунок 3) коэффициент усиления на низких частотахравен RP/R и частота среза определяется по формуле:

Полоса частот, в которой возможно интегрирование входного напряжения лежит в области от 1/2π∙RP∙С до 1/2π∙R∙С.

В полосе частот от 0 до 1/2π∙RP∙С реальный интегратор можно рассматривать как инвертирующий усилитель с коэффициентом усиления KU = - RP/R.

Триггер Шмитта

Триггер Шмитта представляет собой регенеративный компаратор с гистерезисом. Он может быть выполнен на ОУ с резистивной положительной обратной связью.

Рисунок 10. Триггер Шмита.

Часть выходного напряжения с помощью делителя напряжения R1, R2 подается на неинвертирующий вход.

Когда Uвх <Uоп, то Uвых = + Uвых макс = +Uнас и опорное напряжение Uо будет положительным и равно:

Когда Uвх >Uоп, то Uвых = - Uвых макс = -Uнас и опорное напряжение Uо будет отрицательным и равно:

При подаче на вход переменного напряжения на выходе компаратора формируется сигнал прямоугольной формы.

Рисунок 11. Временная диаграмма работы триггера Шмита.

Основные логические элементы И, ИЛИ, НЕ. Примеры схемотехнической реализации.

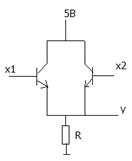

Элемент НЕ (NAND)

| Если х=0 то Uбэ=0, Iб=0, Iк=0, y=5В èy=1

Если x=1 то Uбэ>2,4Вy<0,7Вèy=0

|

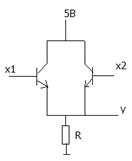

Элемент ИЛИ (OR)

| Если x1=x2=0 =>транзисторы закрыты и y=0

Если х1=01 и х2=0 =>y=1

Если х1=1 и х2=1 оба открыты и y=1

|

Элемент И (AND)

| X1=1 x2=1 y=1

X1=0 x2=1 y=0

X1=0 x2=0 y=0

|

Логич. элементы И-НЕ.Пример схемотехнической реализации. Реализация логических функций И, ИЛИ, НЕ.

Операция НЕ

| На входы подаем x и на выходе не x.

Либо на входы подаем x и 1 и на выходе не х

|

Операция И

| Y=x1*x2=НЕ(НЕ(x1*x2))

|

Операция ИЛИ

| y=x1+x2=НЕ(НЕ(x1+x2))=НЕ(НЕх1*НЕх2)

|

23. Логич. элементы ИЛИ-НЕ.Пример схемотехнической реализации. Реализация логических функций И, ИЛИ, НЕ.

Схемы отличаються от 22 вопроса только тем что используються элементы ИЛИ-НЕ вместо И-НЕ. Логические выражение меняються для:

НЕ: x+0=xx+x=x

ИЛИ: y=x1+x2=не(не(x1+x2))

И: y=x1x2=не(не(x1*x2))=не(нех1+нех2)

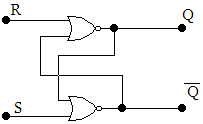

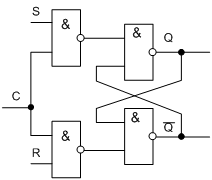

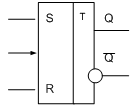

Асинхронный RS тригер

Триггер в котором при поочередном поступлении импульсов на установочные входы изменяеться состояние тригера.

S (set) – вход установки триггера в 1.

R (reset) – вход установки триггера в 0

При подаче активного уровня на R триггер = 0, акт. Уровень на S триггер = 1, два активных уровня – триггер не работает, два низких уровня – режим хранения памяти.

Таблица истиности:

| Qn

| R

| S

| Qn+1

| Не Qn+1

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| -

| -

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| -

| -

|

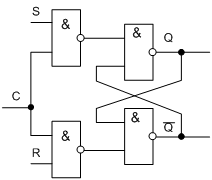

Схема тригера в базисе ИЛИ-НЕ

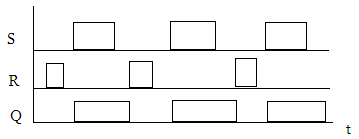

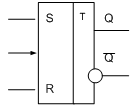

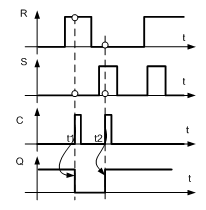

Синхронный CRS триггер

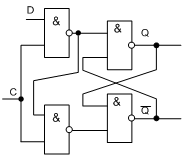

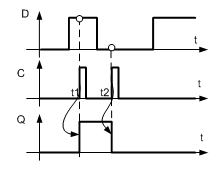

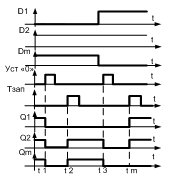

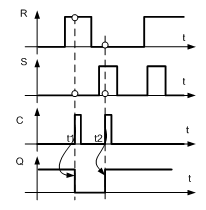

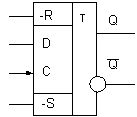

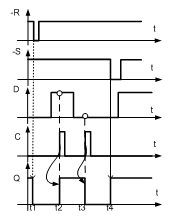

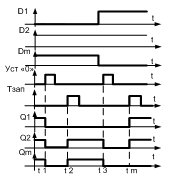

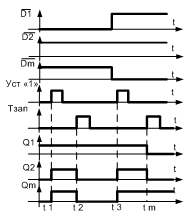

На Рис.3.15. представлено условное обозначение (а), схема (б), и диаграмма работы (в) синхронного RS триггера.

Как видно из диаграммы до прихода тактовых триггер находится в состоянии 1 (выход Q=1). В момент времени t1 на вход С поступает импульс синхронизации, в этот момент времени на входе R триггера присутствует сигнал логической 1, а на входе S сигнал логического 0, что вызывает переключение триггера в состояние «0» по прямому выходу Q.

В момент времени t2 на вход С поступает следующий импульс синхронизации, в этот момент времени на входе S триггера присутствует сигнал логической 1, а на входе R сигнал логического 0, что вызывает переключение триггера в состояние «1» по прямому выходу Q.

В момент времени, когда на входах R и S триггера присутствует одновременно сигнал логической 1 переход триггера в запрещенную комбинацию не осуществляется в связи с тем, что отсутствует импульс синхронизации на входе С.

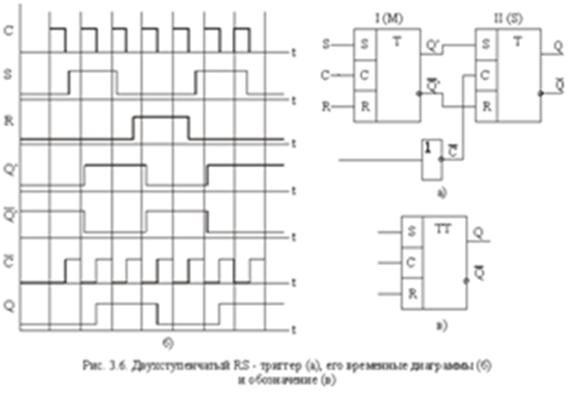

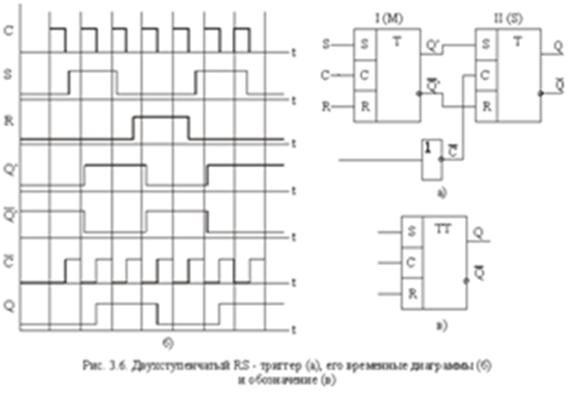

27.Двухступенчатый СRS - триггер. Применение одноступенчатых RS-триггеров в качестве самостоятельных запоминающих элементов ограничено. Это связано с неустойчивой работой последовательностной схемы (цифрового автомата), память которой выполнена на одноступенчатых RS-триггерах. Сигналы переключения триггера S(t), R(t) формируются в цифровом автомате комбинационной схемой, в их формировании участвуют, наряду с внешними логическими сигналами, сигналы Q(t) и Q(t)(c инверсией). Переключение одноступенчатого триггера под действием сигналов S(t) и R(t) вызывает изменение значений сигналов Q(t) и Q(t)(c инверсией), а их изменение может привести к изменениям сигналов S(t) или R(t) в том же такте времени t и, как следствие, к ложному срабатыванию триггера. Для устойчивой работы триггера необходимо, чтобы сигналы Q(t) и Q(t)(c инверсией)изменялись только после прекращения действия входного сигнала S(t) или R(t). Это требование выполняется в двухступенчатых триггерах (MS-триггерах). Базовыми схемами для построения двухступенчатых триггеров являются одноступенчатые RS-триггеры. Двухступенчатый триггер состоит из двух секций (ступеней), соединенных каскадно, как показано на рис. 3.6 а, причем, каждая секция содержит по синхронному RS-триггеру. Первая секция, ведущая или М-секция (М происходит от английского MASTER) принимает информацию со входных линий S и R. Состояние выходов ведущей секции подается на вторую секцию, ведомую, или S-секцию (S происходит от английского SLAVE).

Для ведущего триггера используется обычная синхронизация, в то время как для ведомого триггера импульс синхронизации инвертируется. Изменение состояния выхода ведущего триггера будет происходить в момент появления положительного импульса синхронизации, и эти изменения будут переданы на входы ведомого триггера. Однако, никакие изменения на выходе ведомого триггера не будут происходить до тех пор, пока не появится положительный сигнал инвертированного импульса синхронизации, т.е. отрицательный (задний фронт) фронт исходного синхроимпульса. Следовательно, изменения на выходах Q и Q(t)(c инверсией) не произойдет до тех пор, пока не завершится импульс синхронизации. На рис. 3.6, б показаны временные диаграммы работы триггера.

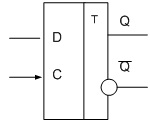

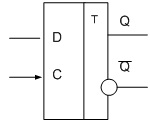

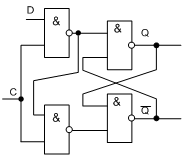

D-Триггер

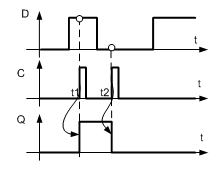

D-триггер (иначе триггер задержки) является самым распространенным триггером. Он имеет один информационный вход D (вход данных) и один тактовый вход C.

Тактируется триггер (то есть меняет свое состояние) по положительному фронту сигнала С (по его переходу из нуля в единицу) в зависимости от состояния входа данных D. Если на входе D единичный сигнал, то по фронту сигнала С прямой выход триггера устанавливается в единицу (инверсный — в нуль). Если же на входе D - нулевой сигнал, то по фронту сигнала С прямой выход триггера устанавливается в нуль (инверсный - в единицу).

Остановимся на работе D-триггера чуть подробнее, так как он наиболее часто используется.

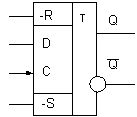

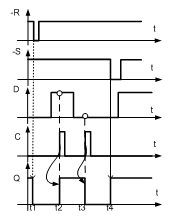

Ранее говорилось, что RS и -R-S триггера редко используются как самостоятельные, но могут быть использованы для построения триггеров с установочными входами. Условное обозначение такого триггера представлено на Рис. 3.17(а), диаграмма его работы на Рис. 3.17(б).

Как следует из диаграммы (Рис.3.17) в момент t1 работа триггера определяется установочным сигналом на входе – R (логический «0») – триггер перебрасывается в состояние «0». Нулевое состояние триггера сохраняется до момента t2, когда сигналы на установочных входах неактивны, на входе D присутствует сигнал «1», а на входе С – положительный фронт, что обеспечивает переключение триггера из состояние «0» в состояние «1».

В момент t2 работу триггера определяет вход D (логический «0») и положительный фронт сигнала С (триггер переходит в состояние «0»).

В момент t3работу триггера определяет установочный вход –S, который обеспечивает его переключение в состояние «1».

Следует отметить, что согласно схемотехнической организации триггера с установочными входами при одновременном действии сигналов на один из установочных входов, на информационный и вход С, состояние триггера определяет установочный вход.

На установочные входы –R–S активные сигналы (–R=–S=0) одновременно поданы быть не могут (согласно схеме –R–S триггера это запрещенная комбинация).

Все приведенные временные диаграммы относятся к первому уровню представления, к уровню логической модели. Конечно же, в реальности все триггеры имеют временные задержки установки выходных сигналов, а также предъявляют определенные временные требования к входным сигналам, при нарушении которых любой триггер будет работать неустойчиво или же не будет работать вообще. Это учитывается на втором уровне представления (в модели с временными задержками).

Длительность тактового сигнала C (как положительного, так и отрицательного импульса) не должна быть слишком малой, иначе триггер может переключаться неустойчиво. Это требование универсально для всех микросхем, срабатывающих по фронту входного сигнала.

Принципиально важна и величина временного сдвига (задержки) между установлением сигнала D и рабочим (положительным) фронтом сигнала C. Этот сдвиг тоже не должен быть слишком малым.

Не должен быть чрезмерно малым и сдвиг между окончанием сигналов –R и –S и рабочим фронтом сигнала С.

Повышенные требования предъявляются также к длительности фронта тактового сигнала С, которая не должна быть слишком большой. Это требование также универсально для всех микросхем, срабатывающих по фронту входного сигнала.

Т.е., чем сложнее микросхема, тем важнее для нее становятся ограничения второго уровня представления, тем выше требования к разработчику цифрового устройства по учету временных задержек и длительностей сигналов.

Следует обратить внимание на то, что цифровые схемы не любят слишком коротких входных сигналов и слишком малых задержек между входными сигналами, функционально связанными между собой. Ориентир здесь очень простой — величина задержки логического элемента данной серии. Поэтому для более быстрых серий ограничения будут менее жесткими, а для более медленных серий — более жесткими.

Несмотря на свою достаточно сложную внутреннюю структуру, микросхемы триггеров являются одними из самых быстрых. Задержка срабатывания триггера обычно не превышает 1,5–2 задержки логического элемента. (причем задержки по входам –R и –S чуть меньше, чем по тактовому входу С.) В некоторых сериях JK-триггеры несколько быстрее, чем D-триггеры, в других — наоборот.

Важный параметр триггера — максимальная частота тактового сигнала С. Для ее приблизительной оценки можно придерживаться следующего простого правила: период тактового сигнала С не должен быть меньше величины задержки переключения триггера по входу С.

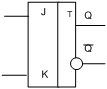

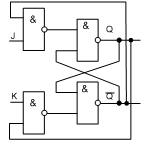

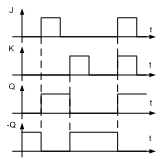

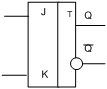

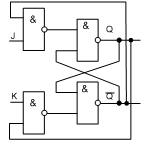

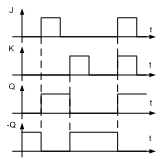

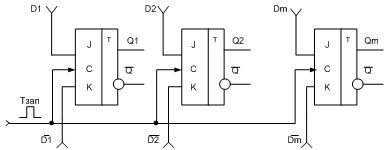

JK триггер

Условное обозначение асинхронного JK триггера (а), его схема (б) и диаграмма работы (в) представлены на Рис.3.12.

Особенностью JK триггера является то, что он не имеет запрещенных комбинаций. Если на входы J и K действует активный сигнал («1»), то триггер изменяет свое состояние на противоположное тому, в котором он находился до действия сигналов, иначе говоря работает в счетном режиме.

Вход J триггера (аналогично входу S) является входом установки триггера в единичное состояние по прямому выходу Q.

Вход S триггера (аналогично входу R) является входом установки триггера в нулевое состояние по прямому выходу Q.

|

|

|

| а)

| (б)

| (в)

|

|

Рис.3.11. Условное обозначение асинхронного JK триггера (а), его схема (б) и диаграмма работы (в)

|

Работа асинхронного JK триггера можно описать таблицей истинности

| J

| K

| Qt

| Qt+1

| Примечание

|

|

|

|

|

| Хранение «0» (сигналы на входах неактивны)

|

|

|

|

|

| Установка в состояние «0» (триггер стоял в состояние «0», устанавливается в состояние «0» по активному входу К=1)

|

|

|

|

|

| Установка в состояние «1» (триггер стоял в состояние «0», устанавливается в состояние «1» по активному входу J =1)

|

|

|

|

|

| Счетный режим, триггер переходит из сотояния «0» в состояние «1»

|

|

|

|

|

| Хранение «1» (сигналы на входах неактивны)

|

|

|

|

|

| Установка в состояние «0» (триггер стоял в состояние «1», устанавливается в состояние «0» по активному входу К=1)

|

|

|

|

|

| Установка в состояние «1» (триггер стоял в состояние «1», устанавливается в состояние «1» по активному входу J =1)

|

|

|

|

|

| Счетный режим, триггер переходит из сотояния «1» в состояние «0»

|

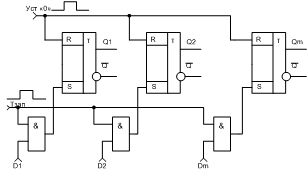

Параллельные регистры

Стробируемые регистры

Параллельные регистры, срабатывающие по уровню стробирующего сигнала (или, как их еще называют, регистры-защелки, английское "Latch"), можно рассматривать как некий гибрид между буфером и регистром. Когда сигнал на стробирующем входе - единичный, такой регистр пропускает через себя входные информационные сигналы, а когда стробирующий сигнал становится равен нулю, регистр переходит в режим хранения последнего из пропущенных значений входных сигналов.

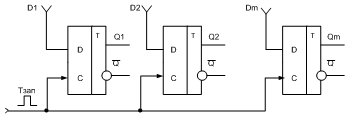

Рассмотрим способы ввода информации в регистр организованный на триггерах с установочными входами.

Существует несколько способов записи информации по установочным входам:

· в прямом коде по установочному входу S с предварительной установкой регистра в «0»;

· в обратном коде по установочному входу R с предварительной установкой в «1» всех триггеров;

· с подачей парафазного кода информации (прямой код на вход S, обратный код на вход R).

Во всех перечисленных способах запись информации осуществляется уровнем сигнала.

Запись информации по установочному входу S с предварительной установкой регистра в «0».

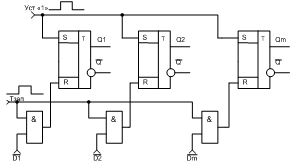

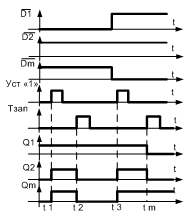

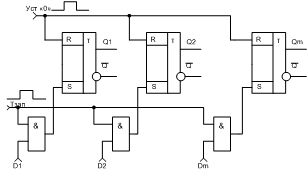

На Рис.4.7. представлена схема (а) и диаграмма (б) работы данного регистра.

Рассмотрим диаграмму работы регистра (Рис.4.7 б). Как видно из диаграммы, до момента действия сигнала Уст «0» (момент t1, регистр стоит в некотором состоянии (Q1=1, Q2=1 …. Qm=1), т.е. хранит некоторую ранее записанную информацию.

Для корректной работы схемы первым (момент времени t1) подается сигнал Уст. «0» (высокий уровень), который устанавливает все разряды регистра в нулевое состояние.

На входы регистра подана в прямом коде некоторая информация (D1=0,D2=1 … Dm=1), которая поступает на один из входов логических элементов, образующих управляющую комбинационную схему. В момент прихода управляющего сигнала Тзап (момент t2), информация, присутствующая на входах D1,D … Dm, записывается в регистр. Т.е. триггер, на вход которогоподается сигнал логической «1» с ЛЭ И (вход D=1, Тзап=1), переходит в состояние «1». Триггер на установочный вход S которого приходит сигнал логического «0» с ЛЭ И (вход D=0, Тзап=1) остается в состоянии логического «0», обусловленном сигналом Уст «0».

Регистр хранит записанную информацию до момента времени t3. К этому моменту времени на входах D1,D … Dm установлены новые данные. В момент t3 подается сигнал Уст «0», в момент t4 сигнал Тзап – в регистр будут записаны новые данные.

Недостатком приведенной схемы является необходимость подачи сигнала Уст «0».

Если триггер имеет установочные инверсные входы (-R-S), то для записи информации подаваемой на входы D в прямом коде необходимо вместо ЛЭ И использовать ЛЭ И-НЕ, а в цепь Уст»0» включить инвертор.

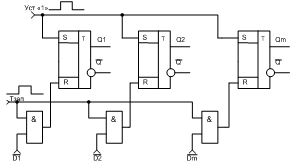

Запись информации по установочному входу R с предварительной установкой в «1» всех триггеров регистра.

На Рис.4.8. представлена схема (а) и диаграмма (б) работы данного регистра.

Особенностью работы данного регистра является то, что данные, которые подаются на его входы D, должны подаваться в обратном коде.

При записи числа в регистр в состояние логического «0» устанавливаются только те триггера, на которые подается обратный код разряда числа равный «1». Остальные триггера останутся в состояние «1».

Недостатком приведенной схемы является необходимость подачи сигнала Уст «1» всех разрядов триггеров.

Тактируемые регистры

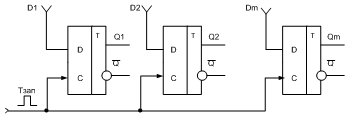

Принцип действия регистров, срабатывающих по фронту тактового сигнала, ничем не отличается от принципа действия D-триггера.

По положительному фронту тактового сигнала С каждый из выходов регистра устанавливается в тот уровень, который был в этот момент на соответствующем данному выходу входе D, и сохраняется таковым до прихода следующего положительного фронта сигнала С. То есть если триггер запоминает один сигнал (один двоичный разряд, один бит), то регистр запоминает сразу несколько (4, 6, 8, 16) сигналов (несколько разрядов, битов). Память регистра сохраняется до момента выключения питания схемы.

На Рис.4.11. представлена схема регистра на D триггерах, в котором данные в прямом коде подаются на входы D1,D … Dm.

Запись информации осуществляется фронтом сигнала Тзап (тактовый командный импульс) одновременно поступающего на входы С всех триггеров.

|

|

Рис.4.11. Запись информации параллельным кодом

|

На Рис.4.12. представлена схема регистра на JK триггерах. В данной схеме данные подаются парафазным кодом (прямой код D1,D … Dm – на вход J, обратный кода – на вход К).

|

|

Рис.4.12. Запись информации парафазным кодом

|

Изменение хранящейся информации в регистре памяти (запись новой информации) осуществляется после установки на входах D0... Dm новой цифровой комбинации (информации) при поступлении определенного уровня (регистр на асинхронных триггерах или запись осуществляется по установочным входам триггера) или фронта синхросигнала (синхроимпульса) Тзап=С на вход «С» регистра (синхронные триггера с записью по информационным входам).

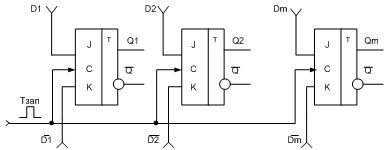

Регистры сдвига

Регистры сдвига или сдвиговые регистры (англ. shift register) представляют собой, последовательно соединенную цепочку триггеров.

Т.е. в сдвиговых регистрах все триггеры соединены в последовательную цепочку (выход каждого предыдущего триггера соединен со входом D следующего триггера). Тактовые входы всех триггеров (С) объединены между собой. В результате такой триггер может рассматриваться как линия задержки, входной сигнал которой последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С. Информационные входы и выходы триггеров могут быть выведены наружу, а могут и не выводиться - в зависимости от функции, выполняемой регистром.

Основной режим их работы - это сдвиг разрядов кода, записанного в эти триггеры,

Полосовой фильтр получается соединением фильтров верхних и нижних частот, он пропускает частоты в определенном диапазоне

Полосовой фильтр получается соединением фильтров верхних и нижних частот, он пропускает частоты в определенном диапазоне

, то

, то

, то

, то

(Поскольку

(Поскольку  является виртуальной землей)

является виртуальной землей)

,

,

.

.