В Формате безадресном (ФБА) кодируются операции управления процессором. Для выполнения их не требуется обращения в память. Поэтому одной из особенностей выполнения этих операций является то, что после выборки команды с начала ее расшифровки в устройстве управления процессора незамедлительно (в этом же цикле) делается обращение в ПЗУ за очередной командой. Рассмотрим особенности выполнения отдельных операций управления процессором.

Операции "Блокировка округления" и "Разрешение округления" непосредственно влияют на работу арифметического устройства. При выполнении первой из них устанавливается в единичное состояние триггер блокировки округления, что определяет выполнение операций "Умножение" и "Деление" без округления результата. Сброс данного триггера производится при выполнении второй операции.

Операция "Разрешение контрольного сложения" используется только режиме "Тест" для организации программного контроля правильности прошивки ПЗУ. При ее выполнении устанавливается в единичное состояние триггер контрольного сложения, в результате чего все последующие операции «сложение» выполняются на арифметическом устройстве как циклическое сложение. Это означает, что возникающая при переполнении единица из j-гo разряда прибавляется к младшему разряду сумматора, при этом на счетчике циклов производится подсчет единиц в 17 и 18 разрядах ячейки ПЗУ, выбранной по исполнительному адресу операции "Сложение". При единичном состоянии триггера контрольного сложения и выполнении операции "Нормализация" обнуление СчЦ, блокируется

Операция "Блокировка контрольного сложения" сбрасывает триггер контрольного сложения в нулевое состояние и тем самым запрещает контрольное сложение.

Операция "Останов" прекращает выполнение последующих команд в процессоре и выполняется только при включенном имитаторе. Возобновление работы процессора а этом случае осуществляется нажатием кнопки ПУСК на блоке ФB98I, кроме того, возможна блокировка операции тумблером БЛОКИРОВКА КОМ. СТОП.

При выключенном имитаторе операция "Останов" выполняется как oперация "Ничего не делать", которая состояние процессора не изменяет.

Операция "Выделение модуля" производится над числом, находящимся в Р2 арифметического устройства и являющимся результатом предыдущей операции. В начале операции производится пересылка его из Р2 в РСм’ и Р2’.Если число положительное, т.е. содержимое знакового разряда РСм’ равно нулю, то все остается без изменений. Если число отрицательное, то оно в Обратном коде подается в См1 и в См2. А к младшим разрядам См1 и СМ2 прибавляется "I" для образования дополнительного кода. Полученный результат операции пересылается из См1 в РСм и из См2 в Р2. Затем для контроля правильности выполнения операции содержимое Р2 и РСм сравнивается.

Операция "Сброс неисправности" очищает регистр сбоев и триггер переполнения.

Операция "Разрешение прерывания" обеспечивает сброс триггера блокировки прерываний и тем самым разрешает работу схемы прерывания.

34 Задачи, решаемые умножителем темпа 1 и умножителем темпа 2. Технические характеристики УТ. Структурная схема УТ, назначение узлов и элементов. Взаимодействие с внешними абонентами.

УТ – спецЭВМ, выполняет функции буферного устройства м\увычислительными средствами и аппаратурой отображения и управления.

Задачи УТ1-М:

1. обработка информации от РЛО (КО-1) для формирования разверток на ЭЛТ

2. выборка из потока данных информации о тех. состоянии РЛО и выдача её на индикаторы

3. обработка инф. от СВ1 и СВ2 для выдачи на индикаторы графической и цифровой инф. с учетом команд операторов РСД

4. формирование массивов данных для записи на АБД

5. Прием с АБД в режиме ВОСПР.

Задачи УТ2-М

1. Обработка данных от СВ2 для выдачи на индикаторы графической и цифровой инф. с учетом команд операторов и командира с ЦПУ. Преобразование темпа выдачи информации.

2. Обработка комнд операторов и командира и выдача их на СВ2

3. формирование массивов данных для записи на АБД

4. Прием с АБД в режиме ВОСПР.

ТТХ:

Сис-ма команд – 1- и 2-адресная. 36 разрядов в команде (1 кр). Всего 16 команд.

Числа – с фиксированной запятой в обратном коде. 25 разрядов (1 кр).

Быстродействие – 500 000 оп\с (2 мкс на простую команду).

Емкость: ОЗУ – 6х512 25-разрядных яч., ПЗУ – 8192 36-разрядных яч.

Цикл обращения к памяти – 2 мкс. Прерываний – 24.

Имеется 12 линий связи для обмена с внеш. абонентами:

УО1 – обмен по ЛС8-12 с СВ в параллельном 25-разр. коде.

УО2 – по ЛС1-6 с ЭЛТ на ПУ (односторонний, паралл-послед код)

УО3 – по ЛС7 с органами управления и отображения на ПУ и с АБД (последовательный 25-разр. код)

Сигналы обмена – НО - начало, ИЗЛС-N – запрос на обмен 1 словом, ИСЛС-N -импульс сдвига.

35 Структурная схема процессора УТ, назначение узлов и элементов. Функционирование при формировании адресов команд, расшифровке кодов операций, формировании АИ.

Основная задача УТ – прием и обработка сигналов от ВУ и выдача инфы на ПУ и АБД.

Состав процессора: {узел центрального управления, формирователи АИ и адресов команд}=УУ; УЛ, схема приоритета, коммутатор команд, коммутаторы чисел (ВХ и ВЫХ), сдвигатель, узел контроля и имитатор. (СМ СХЕМУ в альбомах)

Есть команды: центрального управления ЦУ, выдачи индикаторной инфы ВИ и командного канала КК.

Формирование адресов команд для обращения за командами в ПЗУ

Счетчик команд хранит номер текущей команды в данной программе. Для формирования следующей команды к значению на нем добавляется +1, а при переходе к другой программе - обнуляется, и в него запис. новый адрес – с тумблерного регистра (!только при включении имитатора), регистра команд (команды передачи управления) или с входного коммутатора.

Расшифровка КОП происходит в узле центрального управления.

Регистр команд принимает команды в формате ЦУ дешифратор расшифровывает операционную часть. Распределитель импульсов (РИ) вырабатывает временнУю диаграмму УТ (синхронизирует, последовательность сигналов определяется схемой приоритета – см. на схеме). По расшифрованным сигналам и сигналам РИ формирователь микрокоманд вырабатывает соотв. управляющие сигналы.

Формирование АИ для обращения в ОЗУ или ПЗУ или выдачи их в память.

Центральный элемент формирователя АИ – сумматор адреса – складывает содержимое одного из регистров(рег. адреса числа процессора РгА1ЦУ, рег. адреса числа 7 линии связи РгА1ЛС7) и соответствующего регистра модификатора (РгМКЦУ, РгМКЛС1…12). В РгА1ЛС7 содержится адресная часть(АЧ) команды в формате КК. В РгА1ЦУ хранится АЧ команды в формате ЦУ (из регистра команд ЦУ). РгМК ЦУ принимает и хранит код модификатора адреса для команд ЦУ. РгМК ЛС1…12 хранят модификаторы адреса для команд обмена. Всё это коммутируется к сумматору адреса коммутаторами 1 и 2 (см схему).

Выход с сумматора подключается через КМАЧ к ОЗУ или к КМАК и далее к ПЗУ… (см схему)

36 Состав узла логического процессора УТ. Назначение элементов. Функционирование УЛ при приеме кодов операндов и при выполнении команд различных форматов.

УЛ выполняет логические и арифметические операции над 24-разрядными числами. Арифм. операции выполняются раздельно над двумя 12-разрядными слогами (12 и 24 разряды в этом случае - знаковые). Лог. – над всем числом.

В составе УЛ: СМ, РгСМ1 1 числа, РгСМ2 2 числа, выходной регистр РгСМ.

Куда что идет:

На РгСМ1 из сдвигателя или РгСМ, записывется пред выполнением операции. На РгСМ2 - от входного коммутатора, записывается во время выполнения операции. Числа хранятся в прямом коде, поэтому отрицательное число инвертируется при передаче в РгСМ.

Форматы команд. – см таблицу в альбомах.

Опись форматов команд:

ФУЛ формат устройства логического – 1-адресный, для логических арифметических операций. 27 – признак модификации адреса 28 – признак памяти 1-озу, 0-пзу.

ФП пересылка информации 1,2 – связь программно-доступных регистров и ЗУ.

ФНД непосредственные данные – содержит операнд, а не адрес.

ФСИ сложение индексное – операция над содержимым РгКМЦУ – см. формирование АИ.

ФПУ – передача управления – «безусловный переход» и «КЦ». В адресной части А1 – куда сохранить старое содержимое СчКЦУ. В А2 – адрес перехода.

ФСД – операции сдвига чисел. В А1 – адрес числа, над которым вып. операция. 19 разряд - направление сдвига (1 вправо, 0 влево).

ФУП1,2 – условная передача управления. 31-33 или 31 разряды – маска. Переход только если маска и признак совпадут. 14-26 разряды - адрес перехода.

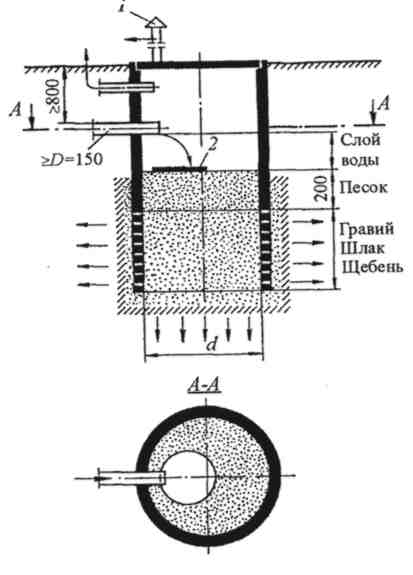

ФБА безадресный – для «останов» и «ничего не делать».

ФВИ выдача на индикаторы. А1 – яч памяти с отображаемым символом. 19-24 – адрес объекта, 29-35 – код, опред. момент выдачи. 25-26 – признак конца выдачи, предварительный и исполнительный. ПИ – инвертирование, ПМ – масштабирование(сдвиг на 1 разряд влево). ДопМК=+1 к адресу.

ФКК – командный канал – передача по ЛС7 (органы управления и индикации на ПУ)

37 Схема приоритета процессора УТ и коммутаторы чисел и команд. Назначение и работа.

Схема приоритета (СП) обеспечивает строгую очередность обработ** сигналов прерываний, поступающих от устройств обмена и процессора УТ, Кроме того, она приостанавливает работу процессора по сигналам управления обменом во время передачи данных между ОЗУ и ВУ. К входным каналам схемы приоритета относятся:

конец массива - КМЛС;

вызов программы обмена по линии связи - ВПЛС;

начало обмена - выдача данных первого рода в линии связи

I...6 - НОВыд.1;

сигнал требования приостанова - работает линия связи - РА.

Первые три из перечисленных являются сигналами прерывания. По сигналу РАБЛС в процессоре приостанавливается выполнение текущей программы, т.е. блокируется модификация содержимого СчКЦУ, осуществляется перезапуск РИ ЦУ и обеспечивается выработка ответного сигнала "Опрос ДС" одному из трех устройств обмена. Шифратором фиксированного адреса по одному из сигналов прерываний от- соответствующего УО формируется адрес обращения к ПЗУ за командой программы обмена. В СчК ЦУ при этом сохраняется адрес команды, перед которой на схему приоритета поступил запрос на приостанов (сигнал РАБЛС). По фиксированному адресу из памяти на РК процессора выбирается команда безусловной передачи управления (ЕЛ), выполнение которой обеспечивает сохранение старого содержимого СчКЦУ в ячейке ОЗУ и установку его нового значения, соответствующего началу программы "Диспетчер". Таким образом, осуществляется переход процессора к исполнению программы обработки прерывания "Диспетчер", которая анализирует- причину прерывания и оп-. ределяет дальнейший порядок исполнения программы обмена. Высшим приоритетом среди входных сигналов СП обладают РАБЛС1...РАБЛС6, приходящие от У02; затем РАБЛС7, поступающий от УОЗ, и в последнюю очередь обрабатываются сигналы РАБЛС8...РАБЛС12 от устройства обмена X. Среди сигналов прерываний высшим приоритетом обладает сигнал НОВыд.1 из У02, затем следует сигналы КШ1С9...КМЛС12, поступающие из У01:; далее-приходящие из У02 - *в последовательности ВПЛС1...ВПЛС6, причем все они обрабатываются только при отсутствии сигналов требования приостанова процессора РАБЛС.

Коммутаторы чисел и команд

Входной коммутатор чисел (ВхК) предназначен для приёма информа-

вии от ПЗУ1, ОЗУ, КМК (I...24 разряды), выходного коммутатора, тумблерного регистра числа (PrTЧ) и передачи её на различные устройства процессора через КШЧ Работа ВхК определяется соответствующими сигна-; вами управления от. узла ЦУ.

Выходной коммутатор4 чисел (ВК) подключает на запись в ОЗУ ряд программно-доступных регистров УТ, кодовую шину КШ2УВВ (т.е. информацию от УО СВ) или содержимое регистра сдвига ЛС7 в зависимости от поступившего сигнала управления.

Коммутатор команд (КМК) служит для приёма кода команд от ПЗУ1,13У4, РгТК и выдачи его в узлы и устройства УТ в зависимости от поступившего сигнала управления.

38 Классификация операций системы команд УТ. Структура форматов команд умножителя темпа.

В УТ выполняется 24 операции. Все операции УТ можно классифицировать:

по характеру выполняемых действий; по способу адресации;

По характеру выполняемых действий операции делятся на:

1. Арифметические и логические операции.

2. Операции пересылки ("запись", "считывание").

3. Операции передачи управления ("УП", "Ш", "КЦ").

4. Операции сдвига.

5. Прочие ("СИ", "ОСТ", "ВД").

По способу адресации операции делятся на: адресные;, безадресные.

Адресные, в свою очередь, делятся на две группы: одно- и двухадресные.

Адресные операции требуют при, выполнении обращения в память I! (или) к программно-доступным регистрам. В одноадресных операциях.формируется либо адрес ячейки памяти, либо адрес программно-доступного регистра (т.е. используется одна адресная часть - либо AI, либо А2).;

В двухадресных операциях формируются оба адреса (т.е. используются обе адресные части - и AI, и А2).

При выполнении безадресных операций адреса не формируются. При этом операнд либо отсутствует, либо находится в коде самой команды» '

К адресным операциям относятся арифметические и логические операции, операции пересылки, операции передачи управления и операции сдвига.

К безадресным операциям, в частности, относятся операции СИ (сложение индексное), ОСТАНОВ и "НИЧЕГО НЕ ДЕЛАТЬ", а также часть других операций (например, формата непосредственных данных).

39 Особенности взаимодействия узлов и элементов структурной схемы процессора УТ при выполнении операций: арифметических и логических, пересылки.

Логические и арифметические операции:

У ФУЛ - <РгСМI> x <АИ> ->РгСМ, х - некая операция

В ФНД - <РгСМI> Операнд ->РгСМ

Второй операнд для операций в формате ФМД находится в разрядах I...24 кода команды.

Из вышеприведенного алгоритма видно, что выполнение арифметических и логических операций реализовано довольно-таки просто и рассматривать их подробно нет необходимости. Особенностью выполнения операций в процессоре УТ является то, что результат операций фиксируется в выходном регистре сумматора узла логического РгСМI за исключением трех операций (ЛУ, КС и КСС) когда предусмотрена перепись его во входной регистр РгСМI, т.к. не сделав этого, данные операции выполнить нельзя. Если полученный результат предполагается использовать в следующей арифметической или логической операции, то в программе должна быть предусмотрена команда переписи содержимого РгСМ в РгСМI (например, СЧИТЫВАНИЕ С СУММАТОРА), расположенная перед предполагаемыми операциями. Напомним, что арифметические операции в УЛ выполняют над 12-разрядными слогами двух 24-разрядных операндов. Разряды 12 Я 24 являются знаковыми. Логические операции выполняются над всеми ш разрядами операндов.

Операции пересылки

К операциям пересылки относятся "Запись" (ЗП), "Запись с сумматора” ЗС, “Считываие” (СЧ)"Считывание с тумблерного регистра числа”(СТ) и Считывание с сумматора" (СС). Кодирование операций производится в форматах ФП1,ФП2 и ФНД, причем в последнем из них может быть закодирована только операция СЧ, которая в данном случае будет

выполняться как безадресная. При выполнении операций записи (ЗП, ЗС) числа пересылаются из программно-доступных регистров в память, а при считывании- наоборот В операции ЗС содержимое РгСМ переписывается в ячейку ОЗУ и одновременно в регистры, адреса которых закодированы в А2. Если в команде, кодирующей ЗС, присутствует знак КЗ, то осуществялется перекрёстная пересылка. т.е. содержимое первого слога РгСМ переписывается в разряды второго слога ячейки ОЗУ и программно-доступных регистров, а содержимое второго - в разряды первого. В результате выполнения операции СТ в регистр УТ, указанный в А2, переписывается содержимое тумблерного регистра числа, расположенного не передней панели блока ФВ985М, причём пересылка возможна только при работе имитатора. В противном случае в регистры, указанные в А2, будут записаны нули.

40 Особенности взаимодействия узлов и элементов структурной схемы процессора УТ при выполнении операций: передачи управления, сдвига, безадресных.

Операции передачи управления включают безусловный (БП) и условный переход (УП). Операция БП кодируется в формате ФПУ. Ее выполнение заключается в формировании нового значения Сч КЦУ, по которому процессор переходит к обработке команд другого участка программы. Новое состояние счетчика команд процессора получается путем переписи содержимого 14...26 разрядов (АИ) команды в Сч КЦУ. Старое значение этого счетчика сохраняется в ячейке ОЗУ по адресу АИ. Алгоритм выполнения операции БП показан в табл. 21. К операциям УП относятся «Конец цикла» (КЦ), «Условный переход – сравнение (УПС), «Условный переход – арифмет. Вычитание» (УПВ), Условный переход – логич. Умножение» (УПУ), «Сравнение границ» (СГ), которые кодируются в форматах ФПУ, ФПУ1, ФПУ2. Алгоритм выполнения перечисленных операций приведены в табл. 21. Операция КЦ обычно используется для организации циклического исполнения программы, при этом перед началом циклического участка в Рг МК записывается константа, определяющая в обратном коде количество циклов. В процессе выполнения операции содержимое Рг МК с каждым циклом уменьшается на «1» и записывается по АИ в ОЗУ. В процессе выполнения команды происходит перепись содержимого 14...26 разрядов (АП) команды в СчКЦУ, и осуществляется переход. При обнулении Рг МК происходит выход из цикла, из памяти считывается следующая по программе команда. Остальные операции условной передачи управления (УПС, УПВ, УПУ, СГ) в общем случае состоят из двух частей, первая из которых является арифметической или логической операцией, вторая – непосредственно операцией условной передачи управления, причем выполнение второй зависит от результатов первой. Если признак результата первой операции (r) соответствует заданному в команде условию (М), то происходит переход на другой участок программы; когда это условие не выполняется, последовательность выборки команд программы не меняется, и из памяти выбирается следующая за УП команда. Условие перехода задается «маской» в комаде. Для операции УПС, которая кодируется в формате ФУП1, «маска» является 3-разрядной, для остальных она одноразрядная. Соответствие кодов «масок» условиям перехода в операциях УПС, УПВ, УПУ, СГ показано в табл. 22,23,24.

В операциях «Условный переход – сравнение» и «Сравнение границ» кроме поразрядного сложения по модулю 2 двух операндов над ними выполняется «Арифметич. Вычитание». В выходной регистр Рг СМ пересылаются результаты операции сложения по модулю 2, а по результату арифметического вычитания в УЛ вырабатываются признаки, которые затем используются для проверки заданного «маской» условия перехода. В операциях УПВ и УПУ первыми выполняются действия АВ и ЛУ соответственно, их результаты фиксируются в Рг СМ и по его содержимому формируются соответствующие признаки, которые в дальнейшем используются для проверки заданного «маской» условия перехода.

Сдвиг. К операциям сдвига относятся СД, СДМ, СДС соответственно реализующие сдвиг слова, младшего или старшего слогов. Все названные операции выполняются в формате ФСД, причем они не требуют работы УЛ. Реализуются эти операции в специальном сдвигателе, а результат их выполения пересылается через Рг СМ1 и Рг СМ УЛ. Усли сдвиг арифметич., т.е. 26 – разряд формата равен «1», то знаковые разряды слогов (12-й и 24-й) не смещаются. В отличие от операции СД, реализуемой процессором СВ, при сдвиге вправо знаковый разряд числа не размножается.

«Безадресные» кодируются в форматах ФНД, ФСИ, ФБА. «Сложение индексное (СИ) вып. С целью изменения содержимого Рг МКЦУ путем прибавления к нему операнда, находящ. В 1...12 разрядах команды формата ФСИ. Суммирование значения, находящ. В Рг МКЦУ, с операндом команды происходит на сумматоре ФАИ, куда через КМ2 подается содержимое Рг МКЦУ, а через КМ1 – 1...12 разряды команды. Полученный результат записывается в Рг- МКЦУ. При кодировании этой операции признак МК в команде должен соответ. «1».

В отдельных случаях выполнения программы требуется пауза между командами, которая обеспечивается операцией «Ничего не делать» (НН), при этом состоян регистров проц. Не изменяется, а к содержимому Сч-КЦУ прибав. «1» и формируется адрес очередной программы.

Операция «Останов» прерывает выполнение процессором последующих команд и переводит его в режим ожидания сигнала «Пуск», причем выполняется она только в режиме регаментногоконтроя. Возобновлен. Работы проц. Осущ. Путем нажатия «Пуск» на передней панели блока ФВ 985М (при включенном имитаторе процессора). В режиме «боевая работа» эта операцвып процессором как НН.

Арифмет и логич. Операции, закодированные в формате ФНД, выполн. Как безадресные. При этом содержимое 1...24 разрядов от РК через входной коммутатор переписывается в Рг СМ2 УЛ. Для этого же формата при выполнении операции СЧ операнд от РК через входной коммутатор и сдвигатель переписывается в Рг СМ1 УЛ, причем через сдвигатель он переписывается без изменений.