Дисциплина:Цифровые устройства и микропроцессоры

Цели и задачи дисциплины

Целями и задачами преподавания дисциплины являются:

- изучение методов анализа и синтеза комбинационных и

последовательностных цифровых устройств с использованием математического аппарата алгебры Буля (дискретной алгебры).

- изучение методов проектирования цифровых устройств (ЦУ) на базе ПЛИС;

- изучение принципов построения и функционирования

микропроцессорных систем (МПС);

- разработка цифровых устройств и микропроцессорных систем с использованием современных средств компьютерного моделирования.

Объем дисциплины и виды учебной работы

Таблица 1

| Вид учебной работы

| Всего часов

| Семестр

|

|

| |

| Общая трудоемкость дисциплины

|

|

|

|

| Аудиторные занятия

|

|

| |

| Лекции

|

|

|

|

| Практические занятия (ПЗ) (семинары)

|

|

|

|

| Лабораторные работы (ЛР)

|

|

|

|

| Самостоятельная работа студентов (СРС)

|

|

| |

| Курсовые работы (проекты)

| -

| -

|

|

| Подготовка к практическим занятиям (семинарам)

|

|

|

|

| Подготовка к лабораторным работам

|

|

|

|

| Подготовка к зачету

|

|

|

|

| Подготовка к экзамену

| -

| -

|

|

| Вид итогового контроля

| зачет

| зачет

| |

Лекция 1 Введение в дисциплину

Введение.

Цифровая схемотехника нового поколения активно используется в различных научных и технических направлениях и широко внедряется в системы радио, радиовещание и телевидение.

Наступил перевод современного электронного оборудования на цифровые "рельсы". В настоящее время осуществляется переход в России на цифровое ТВ. Широкое применение цифровой техники резко увеличил спрос на специалистов соответствующего спроса.

Цифровое устройство (ЦУ) - это физическое устройство, в котором изменения напряжения, силы тока, частоты и др. параметров представлены импульсными (дискретными) сигналами, которые отображаются человеком в виде чисел двоичной системы счисления:1 или 0.

В зависимости от наличия или отсутствия памяти цифровые устройства разделяются на 2 класса:

1. Комбинационные ЦУ (КЦУ)

2. Конечные автоматы (последовательностные ЦУ)

Часть I.Комбинационные и последовательностные цифровые устройства

Литература

Основная

1. Амосов В.В. Схемотехника и средства проектирования цифровых устройств. – СПб: БХВ-Петербург, 2007г.

2. Тимченко В.И. Исследование цифровых устройств на компьютерной модели EWB 5.12; 2007г. Методические указания для проведения лабораторных работ.

Дополнительная

1. Микушин А., Сажнев А., Сединин В. Цифровые устройства и микропроцессоры. — СПб.: БХВ-Петербург, 2010 г. — 832 с.

2. Цифровая и вычислительная техника под редакцией Э.В. Евреинова.

1991г.

3.Дэвид М. Харрис, Сара Л. Харрис. Цифровая схемотехника и архитектура компьютера ( второе издание), Morgan Kaufman© English Edition 2013г.-1622с.

Можно скачать руководство и дополнительные материалы к этому учебному пособию по ссылке:

http://textbooks.elsevier.com/web/product_details.aspx?isbn=9780123944245&Search=9780123944245&SearchCr iteria=Keyword

Чтобы узнать больше об Университетской программе Imagination Technologies, посетите

сайт: www.imgtec.com/university

Раздел 1Комбинационные цифровые устройства

Лекция 1: Основные логические функции ЦУ.

Учебные вопросы:

1.Основные термины и определения.

2.Основные элементы логических функции алгебры логики ИЛИ (OR), И (AND), НЕ (NOT), И-НЕ (AND-NOT), И-ИЛИ -НЕ (AND-OR-NOT).

Задание логических функции с элементами структурных формул (СДНФ, СКНФ).

1-й учебный вопрос:

КЦУ - это ЦУ, в котором значения цифровых выходных сигналов в данный момент времени (на данном интервале) определяются только комбинацией цифровых входных переменных сигналов также в данный момент времени.

Примечание: Понятие цифрового сигнала рассмотрим позже.

Вход Выход

Yj= F(X1,X2…Xi…XN)

ПОМНИ!!!

КЦУ не обладает памятью!

Примеры КЦУ:

Элементарные логические функции, мажоритарные ЦУ, сумматор по модулю 2, шифратор, дешифратор, мультиплексор, демультиплексор.

Конечные автоматы (ПЦУ)- это ЦУ, в котором значение цифрового выходного сигнала Yj в данный момент времени (на данном интервале) определяется не только совокупностью цифровых входных сигналов Xi в данный момент времени, но и комбинацией цифровых входных сигналов, которые действовали на предыдущем интервале. Следовательно, КА обладает памятью, поскольку имеются обратные связи!!!

|

Обратная связь Q1

Обратная связь Q2

|

Yj= F {(X1, X2…Xi…XN)(Q1,Q2…QK)}

кцу зу

Пример КА:

Триггеры, регистры, счетчики.

Логическая функция (ЛФ)- математическое описание работы ЦУ.

Логический элемент (ЛЭ)- физическая реализация логической функции.

Понятие сигнала. Сигналом будем называть изменение физической величины, например, напряжение, частота. Сигналы являются носителем информации!!! Сигналы бывают аналоговые и дискретные (импульсные).

Аналоговый сигнал – несущая информацию величина (например, напряжение) меняется

непрерывно по времени и значению.

Дискретный сигнал – физическая величина (например, напряжение) изменяется дискретно по величине и непрерывно во времени.

Непрерывные и дискретные сигналы можно наблюдать с помощью измерительных приборов (например, на осциллографе)!!!

В цифровой схемотехнике введено понятие цифровой сигнал.

Цифрой сигнал – сигнал, который принимает значение двоичной системы счисления, а именно, U(t)≥Uпорог, то цифровой сигнал принимает значение 1. В противном случае, если U(t) Uпорог, то цифровой сигнал принимает значение 0.

Примечание: Далее в дисциплине будем рассматривать только цифровые сигналы.

2-ой учебный вопрос.

Основные элементы логических функции алгебры логики (или (or), и (and), не (not), и-не (and-not), и-или-не (and-or-not).

Рассмотрим (вспомним) основные элементы логических функций алгебры логики в виде сводной таблицы (отдельный файл - Базов_ЛФ Таблица).

3-й учебный вопрос:

Задание логических функций в виде структурных формул

(СДНФ, СКНФ)

На 3входа.

Табличное представление ЦУ:

Lнаб=2N

N=3, L=23=8

X

1

X2 Y

X3

Лекция 2

Лекция 3

Синтез дешифратора

Дешифратор - это КЦУ,которое преобразует двоичный цифровой код на входе в унитарный цифровой код на выходе.

Рассмотрим пример дешифратора, у которого на входе 3-х разрядный цифровой код, а на выходе 8-разрядный унитарный цифровой код.

| №

| Х2

| Х1

| X0

| Y7

| Y6

| Y5

| Y4

| Y3

| Y2

| Y1

| Y0

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

УГО дешифратора

Запись структурной схемы дешифратора в базисе AND-NOT

Применим два отрицания справа от знака равенства и получим формулы

вида:

Синтез мультиплексора

Мультиплексор – КЦУ, предназначенное для поочередной передачи на один выход одного из Nвходных сигналов, т.е. для мультиплексирования (объединения – multiplexer).Управление работой мультиплексора (выбор номера канала) осуществляется с помощью входного кода адреса. Например, для 4-х канального мультиплексора (4 входа и один выход) необходим 2-х разрядный управляющий (адресный) код, а для 16-ти канального 4-х разрядный

Рассмотрим синтез мультиплексора на 4 входа и 1 выход (MS 4/1)

Таблица переключений:

СДНФ:

Схема мультиплексора имеет вид

УГО мультиплкексора

Демультиплексор (разъединитель сигналов-каналов)

Демультиплексор осуществляет выдачу на выходе сигнала одного из информационных каналов в зависимости от содержания адреса

Таблица переключенийдемультиплексора (DMS 1/4):

СДНФ:

Раздел 2Конечные автоматы (КА) с малым объемом памяти(последовательные устройства - ПЦУ)

КА(ПЦУ) - это цифровое устройство, в котором значения выходного сигнала Yj в данный момент времени определяется не только значением входных сигналов Xi в данный момент времени,но и тем значением, которое было на предыдущем интервале.

Примеры КА: триггеры, регистры, счетчики

Лекция 4

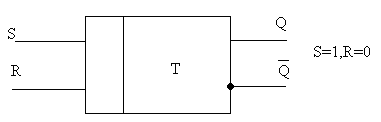

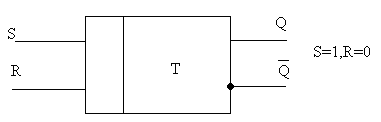

Асинхронные (RS) и синхронные (RSC) триггеры.

Учебные вопросы:

1.Общее сведенье о триггерах.

2.Асинхронный триггер.

3.Синхронный триггер.

1-й учебный вопрос:

Триггер- это цифровое устройство последовательного типа(обладает памятью) с двумя устойчивыми состояниями равновесияи предназначенное для записи, хранения и считывания одного бита информации.

Устойчивое состояние, когда на выходе триггера 1 или 0 удерживаются при постоянной подаче на вход определенной комбинации. Т.е. триггер может находиться в единичном или нулевом состоянии (Q=1,Q=0)(Q=1,Q=0). Равенство значений Q и Q будет определяться, как запрещенное состояние для триггера.

Классификация триггеров:

1. По способу записи информации

а) асинхронные триггеры - информация записывается в любой момент времени и значения на выходе триггера определяется только входными информационными сигналами;

б) синхронные триггеры (тактируемые) имеют кроме информационных входов синхровход(разрешающий сигнал). Срабатывание триггера происходит при подаче синхроимпульсов, а значение выходного сигнала определяется комбинацией информационных входных сигналов.

2. По логике работы:

а) триггеры установочные (RS триггеры), которые являются составной частью более сложных триггеров (JK, D- триггеров) и предназначены для начальной установки триггера;

б) триггеры со счетным входом(Т- триггеры) применяются в счетчиках;

в) триггеры задержки информации(D- триггеры);

г) универсальные JK- триггеры, которые могут выполнять перечисленных ранее триггеров.

Основными характеристиками триггера являются:

1. Быстродействие (кол-во переключений в единицу времени).

2. Нагрузочная способность (кол-во логических элементов, которые могут подключаться к выходам триггера)

2-й учебный вопрос: Асинхронный RSC триггер с инверсными входами

Активный переключающий сигнал 0

S (set) - для установки триггера в единичное состояние.

R (reset) - для установки триггера в нулевое состояние.

Q – прямой выход.

Q^ – инверсный выход.

Триггеры с прямыми и инверсными входами:

Триггер с прямыми входами

УГО

Активным переключающим сигналом является 1

Схема триггера с инверсными входами

Таблица переключения работы триггера с инверсными входами:

| Sn

| Rn

| Qn-1

| Qn

| Q^n

|

|

|

|

| -

| -

|

|

|

|

| -

| -

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Qn=Q^n -запрещенное состояние

Запись 1

Запись 0

хранение

Математическая запись работы триггера:

Qn= Snv(Rn-Qn-1)

Схема триггера с прямыми входами

3-й учебный вопрос: Синхронный (RSC) триггер.

В синхронных триггерах (RSC,T,D,JK) применяются 2 способа синхронизации:

1 ) статическая синхронизация, когда импульсом является наличие постоянного напряжения;

2) динамическая синхронизация, когда импульсом является наличие перепада напряжения

Триггеры бывают:

· Однотактные, когда требуется наличие переднего или заднего фронта сигнала;

· двухтактные, когда требуется наличие переднего и заднего фронта сигнала.

Двухтактные:1-0-1 задний и передний фронты;

0-1-0 передний и задний фронты.

РассмотримRSC триггер с прямыми входами и статической синхронизацией.

УГОRSC триггера

СхемаRSC триггера

Примечание: Любой синхронный триггер в отсутствии синхронизации находиться в режиме хранения

Таблица переключений RSC – триггера

| Сn

| Sn

| Rn

| Qn-1

| Qn

| Qn^

| Сост.триггера

|

|

|

|

|

|

|

| Хранение

|

|

|

|

| Хранение

|

|

|

|

|

|

|

| Хранение

|

|

|

|

| Хранение

|

|

|

|

|

|

|

| Хранение

|

|

|

|

| Хранение

|

|

|

|

|

|

|

| Хранение

|

|

|

|

| Хранение

|

|

|

|

|

|

|

| Хранение

|

|

|

|

| Хранение

|

|

|

|

|

|

|

| Запись «0»

|

|

|

|

| Запись «0»

|

|

|

|

|

|

|

| Запись «1»

|

|

|

|

| Запись «1»

|

|

|

|

|

| -

| -

| Запрещ.сост.

|

|

| -

| -

| Запрещ.сост.

|

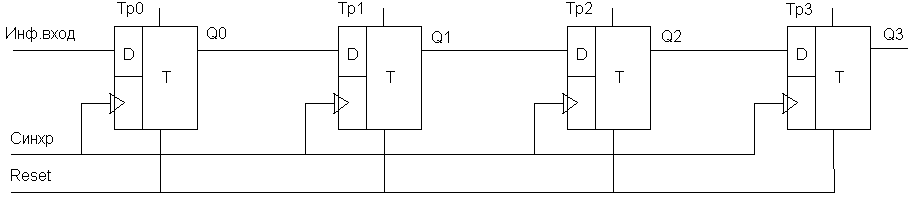

Классификация регистров.

В зависимости от содержания выполняемых операций в регистре, регистры бывают:

1)с параллельным приемом и параллельной выдачей информации. На этом принципе выполнено ОЗУ

2)с параллельным приемом и последовательной выдачей информации.

3)с последовательным приемом и параллельной выдачей информации.

2-й учебный вопрос. Синтез регистров (регистры памяти, сдвига, реверсивные регистры).

Принцип синтеза регистров: все регистры состоят из одинаковых блоков, количество которых определяется разрядом регистра. Каждый блок включает триггер(как правило, D- триггер) и сравнительно простое КЦУ. Следовательно, синтез регистра сводится к синтезу 1 блока с учетом связи между ними.

а) Регистры памяти (регистры с параллельным приемом и параллельной выдачей информации)

Рассмотрим схему 4-х разрядного регистра памяти:

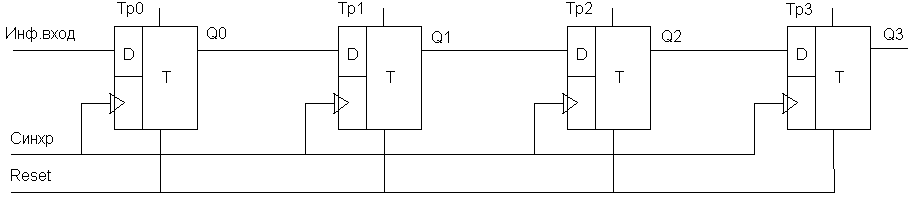

б) Регистры сдвига (регистры с последовательным приемом и параллельной выдачей информации)

Таблица переключений регистра сдвига без ОС

Реверсивный регистр

Это регистр, в котором информация сдвигается как влево, так и вправо.

Рассмотрим регистры сдвига с обратными связями:

· Если соединить выход любого разряда регистра с входом, то получим кольцевой регистр, в котором информация будет перемещатьсяпо кольцу.

УГО

· Кольцевой регистр с перекрестной обратнойсвязью, когда в цепи обратной связи включен инвертор:

УГО:

· Кольцевой регистр с логической обратной связью

Это регистр, в цепи обратной связи которого включено логическое устройство. В нашем примере логическим устройством является сумматор по модулю 2.

УГО:

· Регистр сдвига с самовоcстановлением

Рассмотрим одну из возможных схем регистра самовосстановления: данная схема обеспечивает перемещение по кольцу 1, т.е. наличие унитарного кода.

Лекция 7. Двоичные и двоично-десятичные счетчики

Учебные вопросы:

1. Определение и классификация счетчиков.

2. Синтез двоичных и двоично-десятичных счетчиков.

1-ый учебный вопрос: Определение и классификация счетчиков.

Определение: Счетчик- это последовательное цифровое устройство, которое обеспечивает хранение слова информации и выполнение над ним микрооперации счета.

Микрооперация счета- изменение числа на +-1.

Суммирующий счетчик- это то, что было в счетчике +1

С=С+1

Вычитающий счетчик- это то,что было в счетчике -1

С=С-1

Реверсивный счетчик: С= + -1(и то и другое выполняет)

Счетчики работают в двоичном коде и обеспечивают подсчет импульсов в интервале от 0 до 2N-1, где N- количество разрядов счетчика.

Смакс=2N-1

Например: 4- х разрядный счетчик имеет диапазон чисел от 0до (24-1)=15

Примечание: после достижения максимального значения суммирующий счетчик начинает счет с 0.

Пример: 0,…..,C,D,E,F,0,1……

Вычитающий счетчик: …..C,B,A,9…2,1,0,F…

Для построения счетчиков используются Т- триггеры(D,JK триггеры в режиме Т- триггера)

D- триггер

JK – триггер

УГО счетчика

>15(P) – перенос в старший разряд при суммировании

< 0(CR) – заем из старшего разряда при вычитании

2-й учебный вопрос:

Преобразователи информации

Учебные вопросы:

1. Принцип аналого-цифрового и цифроаналогового преобразования.

2. Цифро-аналоговые преобразователи (ЦАП) информации.

3. Аналого-цифровые преобразователи (АЦП) информации.

Литература:

1. Цифровая и вычислительная техника. Под ред. Э.В. Евреинова.

Радио и связь. 1991г. стр. 173-180

1. Принцип аналого-цифрового и цифроаналогового преобразования.

Речь, телефонные сообщения, музыка, видео информация, показания аналоговых измерительных приборов представлены в цифровых устройствах в цифровом коде.

Преобразование сигналов из аналоговой формы в цифровую выполняется в устройстве, называемом аналого-цифровым преобразователем (АЦП). В АЦП можно выделить следующие процессы:

Ø дискретизацию;

Ø квантование;

Ø кодирование.

Рассмотрим сущность этих процессов.

Квантование и кодирование.

Сущность этих операций заключается в следующем. Создается сетка так называемых уровней квантования, сдвинутых друг относительно друга на величину, называемую шагом квантования. Каждому шагу квантования можно приписать порядковый номер (0, 1, 2, 3 и т.д.). Полученные в результате дискретизации значения исходного аналогового напряжения U(t)

Заменяются ближайшими к ним уровнями квантования.

Описанный процесс носит название операции квантования. Смысл этого процесса состоит в округлении значений аналогового напряжения, выбранных в тактовые моменты времени. Как и всякое округление, процесс квантования приводит к погрешности (ошибкам квантования), создавая так называемый шум квантования.

Следующая операция, выполняемая при аналого-цифровом преобразовании сигналов, - кодирование. Округленные мгновенные значения сигналов в тактовые моменты времени представляются числами-номерами соответствующих уровней квантования.

Рассмотрим эти процессы на диаграмме:

2-й учебный вопрос. Цифро-аналоговые преобразователи (ЦАП) информации.

Назначение: Для преобразования цифрового двоичного кода в выходное напряжение, U(t) пропорциональное весовым двоичной коэффициентам разрядов двоичной системы счисления (….8,4,2,1).

Рассмотрим схему ЦАП, которая представляет взвешенную резисторную матрицу.

В рассмотренной схеме сумма токов  ,протекающих через резистор R0, пропорциональна весовым коэффициентам двоичных разрядов.

,протекающих через резистор R0, пропорциональна весовым коэффициентам двоичных разрядов.

Например:

3-й учебный вопрос. Аналого-цифровые преобразователи (АЦП) информации.

Назначение: для преобразования мгновенных значений аналогового входного сигнала x(t) двоичный m-разрядный код.

Рассмотрим вначале принцип действия АЦП на временных диаграммах, а затем одну из возможных схем АЦП.

Лекция: Общие сведение о работе цифровых устройств на основе ПЛИС

Учебные вопросы:

1. Определение и классификация ПЛИС.

2. Особенность построения микросхем на ПЛИС

Литература:

1. В.В. Амосов Схемотехника и средства проектирования цифровых устройств. СПб: БХВ-Петербург, 2007 (Учебное пособие).

2.

1-й учебный вопрос. Определение и классификация ПЛИС.

История развития ПЛИС

Запрограммируем функциюY=a&b^

Многократно перепрограммируемые ПЛИС:

Микросхема (как заготовка ПЛИС) включает:

Ø матрицы однотипных логических ячеек (микро ячеек) в базисе 2-И-НЕ или 2-ИЛИ-НЕ;

Ø блок ввода/вывода с устройствами буферизации (тристабильное состояние, открытый или закрытый коллектор);

Ø матрица трассировки, соединение которой обеспечивает соединение между ячейками и микро ячейками и устройствами ввода/вывода.

В настоящее время выделяют двух уровневые ПЛИСы. На первом уровне собираются комбинационные устройства. На втором уровне разрабатываются устройства цифровой обработки сигнала. Цифровая обработка сигнала- это цифровые фильтры и микроконтроллеры. В одном чипе можно собрать МПС со сложным КЦУ. Емкость ПЛИСов условно определяется количеством однотипных логических элементов. ПЛИСы содержат от нескольких сотен до нескольких миллионов логических элементов.

Й учебный вопрос

Структура (архитектура) однокристального восьмиразрядного микропроцессора МП580ВМ80

Определение МП – программно-управляемое устройство, реализуемое на одном или нескольких чипах, которое осуществляет процесс цифровой обработки информации и управление им.

Структура МП

МП состоит из трех блоков:

1. Блок обработки информации ().

2. Блок управления ().

3. Блок хранения информации ().

Блок обработки информации включает восьмиразрядный регистр – аккумулятор, предназначенный для хранения одного из операндов команды и результата операции (выполнения команды).

MOVB,C; (B)←(C)

АЛУ – арифметическое логическое устройство, которое выполняет необходимые арифметические и логические действия над операндами и результат записывает в аккумулятор.

Восьмиразрядный регистр признаков (регистр флагов) необходим для хранения признаков выполнения действий в АЛУ.

7 6 5 4 3 2 1 0

S – признак отрицательного результата (S=1).

Z – признак нулевого результата (Z=1).

0 – не используется.

AC – признак переноса между полубайтами (АС=1).

Р – признак четного числа единиц в байте результата, т.е. в аккумуляторе (Р=1).

СY – признак переноса старшего разряда результата (СY=1).

Блок управления включает восьмиразрядный регистр команд, предназначенный для хранения КОП-а.

Дешифратор команд дешифрирует КОП и выдает управляющие сигналы на устройство управления.

Устройство управления осуществляет управление процессом выполнения команд.

Блок хранения информации включает шесть восьмиразрядных регистров (регистры общего назначения – РОН) – В, С, D, E, H, L. Они предназначены для временного хранения информации в МП (в КЭШ памяти).

Регистры РОН могут использоваться как по отдельности (восьмиразрядные), так и парами (шестнадцатиразрядные).

Только такие пары регистров могут быть В-С, D-E, H-L.

Указатель стека (SP) – шестнадцатиразрядный регистр, предназначенный для хранения адреса стековой памяти.

Стековая память – выделенная память ОЗУ, в которой реализуется принцип: «первый записал, последний прочитал».

Счетчик команд – шестнадцатиразрядный регистр, предназначенный для хранения адреса выполняемой команды.

Принцип работа МП

Работу МП рассмотрим на примере выполнения команды арифметического сложения.

Команда на языке ассемблера (пользователя):

ADDB; (А)←(А)+(В)

Комнда в машинном коде (микропроцессора):

Команды программы предварительно записаны в ЗУ (ОЗУ или ПЗУ).

Все команды в МП выполняются в два этапа:

1) выборка (чтение из ЗУ) и дешифрование команды;

2) выполнение команды.

На первом этапе выполнения команды адрес выполняемой команды, записанной в счетчике команд (PC), под воздействием сигнала управления выставляется на 16-ти разрядную шину адреса (ША) и по ША поступает в ЗУ. В ЗУ ячейка памяти (ЯП) с указанным адресом под воздействием сигналов управления инициализируется на чтение. Содержимое ЯП по шине данных (ШД) поступает в регистр команд и далее на дешифратор команд. Содержимое регистра команд (КОП) хранится в течение выполнения команд. В результате дешифрования команды формируется управляющие сигналы для устройства управления.выполнения команды

На втором этапе осуществляется выполнение команды по микротактам под воздействием сигналов управления. В нашем примере ADDB: содержимое регистра В (РОН) по внутренней шине данных МП поступает в АЛУ, где суммируется с содержимым аккумулятора в АЛУ, т.е. арифметическое сложение содержимого регистров А+В. Результат сложения записывается в аккумулятор. Кроме того, в регистр признаков заносятся признаки выполняемой операции (Z=1, если 0-й результат; S=1, если отрицательное значение результата операции записывается в Ак). После выполнения арифметической операции (в нашем примере) в счетчике команд (PC) будет записан адрес очередной выполняемой команды.

Лекция 2

Система команд.

Трёхбайтные.

В однобайтной команде хранится код операции и операнды. Например:

MOVB,C; в регистр В записывается содержимое регистра С: (В)←(С),

Где В и С – операнды.

Помни!!!: Код операции (команды), в нашем примере хранится только в 1-м байте любой команды (одно, двух, трех байтной).

В двухбайтной команде: в первом байте записывается код операции и один из операндов (операнда может и не быть), во втором – только операнд.

Примеры двухбайтных команд:

([FB])←(A). Из аккумулятора пересылаются данные в порт, адрес которого (FB) во 2-м байте команды (Б2).

Где:

Из аккумулятора (А) вывести информацию на устройство вывода с адресом FB.

Круглые скобки (…) - содержимое ЯП или устройства вывода/ввода;

Квадратные скобки [..] – адрес ЯП или устройства вывода/ввода.

(В)←7Вh. В регистр В заносится 8-ми разрядная (однобайтная) константа 7Вh 16-й системы счисления

В трехбайтной команде: в первом байте команды записывается код операции (КОП), во втором и третьем байтах операнды.

Пример:

(А)←([8A7F]).

Исходная программа на языке ассемблер состоит из последовательности команд, которые называют также ассемблерными строками. Запись строки осуществляется в соответствии с некоторыми формальными правилами (как синтаксис и орфография в русском и др. языках).

Строка (предложение) делятся на несколько полей, разделенных одним и более пробелами:

Ø поле метки;

Ø поле мнемоники кода операции;

Ø поле операнда;

Ø поле комментария.

Таким образом, строка (команда) имеет следующий формат:

[метка] <мнемоника КОП> [операнд]; [комм

,протекающих через резистор R0, пропорциональна весовым коэффициентам двоичных разрядов.

,протекающих через резистор R0, пропорциональна весовым коэффициентам двоичных разрядов.