Особенности сооружения опор в сложных условиях: Сооружение ВЛ в районах с суровыми климатическими и тяжелыми геологическими условиями...

Кормораздатчик мобильный электрифицированный: схема и процесс работы устройства...

Особенности сооружения опор в сложных условиях: Сооружение ВЛ в районах с суровыми климатическими и тяжелыми геологическими условиями...

Кормораздатчик мобильный электрифицированный: схема и процесс работы устройства...

Топ:

Процедура выполнения команд. Рабочий цикл процессора: Функционирование процессора в основном состоит из повторяющихся рабочих циклов, каждый из которых соответствует...

Оснащения врачебно-сестринской бригады.

Методика измерений сопротивления растеканию тока анодного заземления: Анодный заземлитель (анод) – проводник, погруженный в электролитическую среду (грунт, раствор электролита) и подключенный к положительному...

Интересное:

Искусственное повышение поверхности территории: Варианты искусственного повышения поверхности территории необходимо выбирать на основе анализа следующих характеристик защищаемой территории...

Средства для ингаляционного наркоза: Наркоз наступает в результате вдыхания (ингаляции) средств, которое осуществляют или с помощью маски...

Что нужно делать при лейкемии: Прежде всего, необходимо выяснить, не страдаете ли вы каким-либо душевным недугом...

Дисциплины:

|

из

5.00

|

Заказать работу |

Содержание книги

Поиск на нашем сайте

|

|

|

|

Как было сказано выше, каждый порт имеет два регистра - для контроля и управления. Некоторые каналы МК мультиплицирован с периферийными модулями. Это значит, что когда периферийный модуль включён, канал ввода / вывода порта не может быть использован.

Регистр TRIS<X>, обычно, используется для настройки битов порта на вход или на выход. В зависимости от модели, порт может иметь другое назначение, тогда соответствующий регистр управления, также приобретает иную функцию, описанную в документации.

Регистр PORT<Х> - призван хранить входные / выходные данные, поступающие на порт. То есть, по сути, он используется для чтения информации поступающей на порт или из него.

Чтобы установить определённый бит порта на вход – необходимо записать в регистр TRIS<X> логическую единицу – In ‘1’.

Чтобы установить определённый бит порта на выход – необходимо записать в регистр TRIS<X> логический ноль – Out ‘0’.

Чтение PORT<X> происходит по принципу «чтение – модификация – запись» и возвращает состояние выводов порта. При выполнении операций, необходимо учитывать один нюанс, а иначе полученная с порта информация будет лишена смысла.

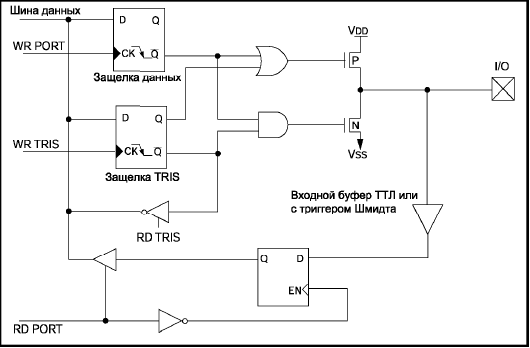

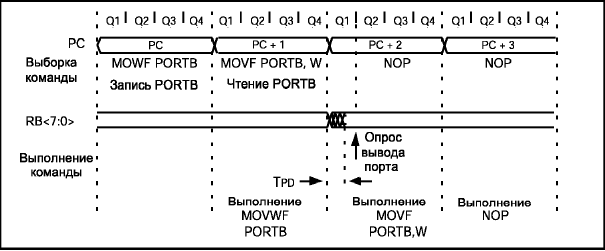

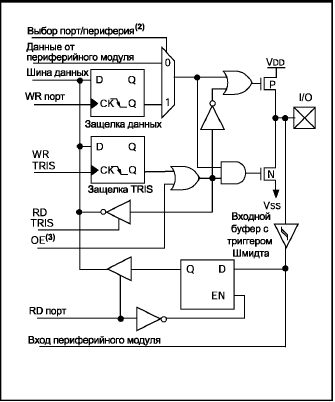

Информация считывается с выводов порта – «чтение», подвергается изменению – «модификация», после чего записывается в защёлку PORT<X> - «запись». Фактически, процесс записи, происходит в конце машинного цикла. Если ей предшествовала операция «чтении», то необходим некоторый промежуток времени, чтобы установилось напряжение на выводе порта, прежде чем, произойдёт другая операция, иначе могут быть считаны старые данные. Чтобы избежать подобной ситуации, необходимо разделить операции «чтение» и «запись» одной или несколькими командами nop. Также возможно применение иных команд, не обращённых к портам ввода / вывода. Для полноты ситуации на рис.8.1 представлена структурная схема одного из каналов порта ввода / вывода. На рис.8.2. изображён процесс «чтение – модификация - запись».

Рис.8.1 - структурная схема канала порта ввода / вывода

Рис.8.2 - операции с каналом порта ввода / вывода

Примечание: на рисунке показан пример чтения PORTB, сразу после записи в него. Время установления данных на PORTB равно: T = 0.25 и расчитано согласно выражению: TCY – TPD. Где длительность TCY – машинного цикла, а TPD – длительность распространения. При высокой тактовой частоте, чтение с порта ввода / вывода, после записи, может возвращать неверные значения.

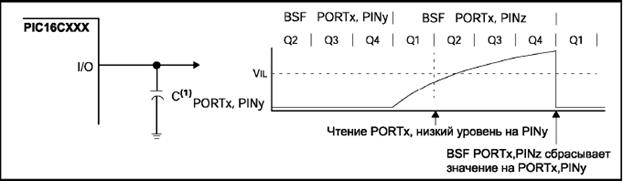

На рис.8.3 – показана модель канала ввода / вывода с описанной ситуацией. С увеличением ёмкости – С, увеличивается длительность спада и нарастания напряжения на выводе. При увеличении тактовой частоты – усиливается влияние ёмкости на выполнение команд «чтение – модификация – запись» с регистром порта ввода / вывода PORT<X>. В состав ёмкости – С, входит паразитная ёмкость проводника и выводов компонентов, подключённых к выводу порта ввода / вывода.

Лучшим способ решения этой проблемы может послужить подключение резистора к выводу порта. Подключённый резистор к выводу порта позволяет достигнуть нужного напряжения перед выполнением следующей команды.

Рис.8.3 – подключение к выводу порта

Примечание: С – это не конденсатор, а ёмкостная нагрузка.

Информация о каждом из портов будет представлена в следующем порядке: краткое описание, пример инициализации порта, а также схема подключения и таблица с описание битов порта.

Регистры PORTA и TRISA

PORTA – 6 разрядный порт ввода / вывода информации. Регистр TRISA позволяет настроить соответствующий канал порта на вход или выход, подав на него '1' или '0' соответственно.

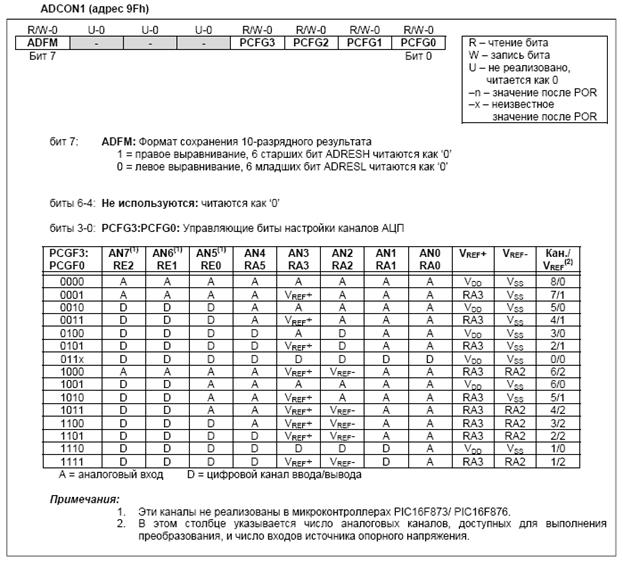

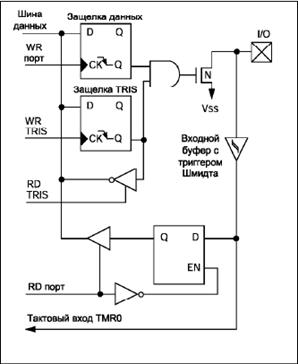

RA4 - имеет триггер Шмидта на входе и открытый сток на выходе, мультиплицирован с тактовым входом T0CKI. Все остальные каналы PORTA имеют TTL буфер на входе и полнофункциональные выходные КМОП буферы. Каналы PORTA мультиплицированы с аналоговыми входами АЦП и аналоговым входом источника опорного напряжения VREF. Биты управления режимом работы каналов порта ввода/вывода PORTA находятся в регистре ADCON1 – рис.8.4.

Биты регистра TRISA управляют направлением каналов порта PORTA, даже когда он используется как аналоговый. В качестве примера, представлена инициализация защёлки PORTA, и установка необходимых битов на вход.

; инициализация PORTA как цифрового

bcf STATUS,6; выбрать банк 00

bcf STATUS,5;

clrf PORTA; инициализация защёлок PORTA

BANKSEL ADCON1; выбрать банк для ADCON1

movlw B‘00001010’; значения для инициализации направления каналов

movwf ADCON1; каналы PORTA – установлены как цифровые

movwf TRISA; бит 1,3 установить – на вход

; бит 0,2,4,5 – на выход

; бит 6,7 – не используются. Читаются как ‘0’.

; инициализация PORTA как обычного

bcf STATUS,6; выбрать банк 00

bcf STATUS,5;

clrf PORTA; инициализация защёлок PORTA

BANKSEL TRISA; выбрать банк для TRISA

movlw B‘00001010’; значения для инициализации направления каналов

movwf TRISA; бит 1,3 установить – на вход

; бит 0,2,4,5 – на выход

; бит 6,7 – не используются. Читаются как ‘0’.

Рис.8.4 – управляющий регистр ADCON1

Необходимые биты, любого порта ввода / вывода, можно устанавливать при помощи бит ориентированных команд – BCF, BSF, пример:

; инициализация PORTA как обычного

bcf STATUS,6; выбрать банк 00

bcf STATUS,5;

clrf PORTA; инициализация защёлок PORTA

BANKSEL TRISA; выбрать банк для TRISA

bsf TRISA,1; бит 1,3 установить – на вход

bsf TRISA,3;

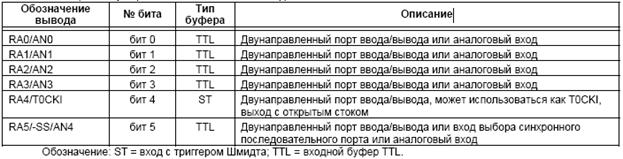

На рис.8.5 – представлена таблица функционального назначения каналов PORTA, а на рис.8.6 – регистры и биты связанные с работой PORTA.

Рис.8.5 – функциональное назначение каналов PORTA

Рис.8.6 – регистры и биты, связанные с работой PORTA

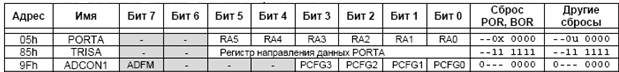

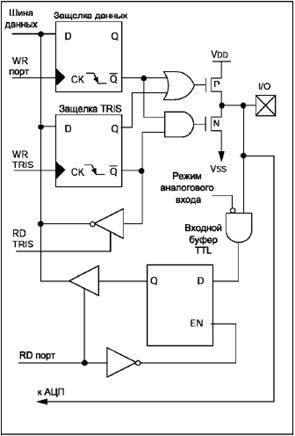

Для общего развития - на рис.8.7 представлена структурная схема выводов RA3:RA0 и RA5, а на рис.8.8 - схема вывода RA4 / T0CKI.

Рис.8.7 - структурная схема выводов RA3:RA0 и RA5

Рис.8.8 – структурная схема вывода RA4 / T0CKI

Регистры PORTB и TRISB

PORTB – 8 разрядный двунаправленный порт ввода / вывода. Регистр TRISB позволяет настроить соответствующий канал порта на вход или выход, подав на него '1' или '0' соответственно.

Три вывода PORTB мультиплицированы со схемой низковольтного программирования: RB3/PGM, RB6/PGC, RB7/PGD.

К каждому выводу PORTB подключен внутренний подтягивающий резистор. Бит -RBPU (OPTION_REG <7>) определяет подключены (-RBPU=0) или нет (-RBPU=1) подтягивающие резисторы. Подтягивающие резисторы автоматически отключаются, когда каналы порта настраиваются на выход и после сброса по включению питания POR.

Четыре канала PORTB RB7:RB4, настроенные на вход, могут генерировать прерывания по изменению логического уровня сигнала на входе. Если один из каналов RB7:RB4 настроен на выход, то он не может быть источником прерываний. Сигнал на выводах RB7:RB4 сравнивается со значением, сохраненным при последнем чтении PORTB. В случае несовпадения одного из значений устанавливается флаг RBIF (INTCON<0>), и если разрешено, генерируется прерывание.

Это прерывание может вывести микроконтроллер из режима SLEEP. Прерывания по изменению сигнала на входах рекомендуется использовать для определения нажатия клавиш, когда PORTB полностью задействован для реализации клавиатуры. Не рекомендуется опрашивать PORTB при использовании прерываний по изменению входного сигнала.

Пример настройки регистров PORTB и TRISB в программе.

; инициализация PORTB

bcf STATUS,6; выбрать банк 00

bcf STATUS,5;

clrf PORTB; инициализация защёлок PORTB

BANKSEL TRISB; выбрать банк для TRISB

movlw B‘00110011’; значения для инициализации

; направления каналов порта PORTB

movwf TRISB; установка битов:

; бит 0,1,4,5 – на вход

; бит 2,3,6,7 – на выход

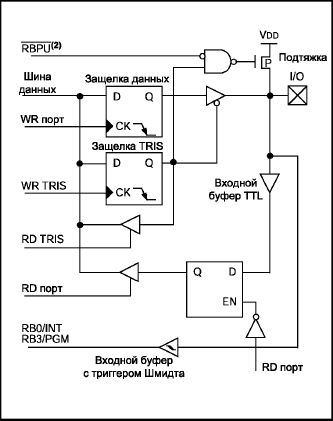

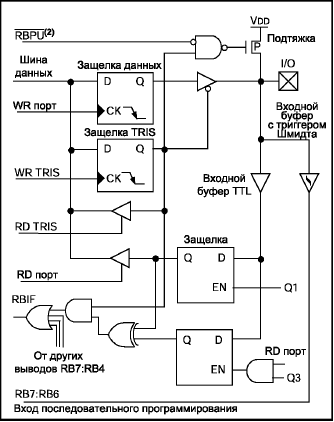

Программно настройка остальных портов не отличается от предыдущей, так что примеры кода приводиться не будут, в целях экономии места. На рис.8.9 изображена структурная схема выводов RB3:RB0, а на рис.8.10 – структурная схема выводов RB7:RB4.

Рис.8.9 - структурная схема выводов RB3:RB0

Рис.8.10 - структурная схема выводов RB7:RB4

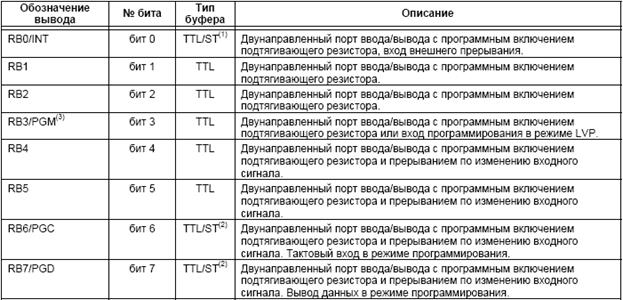

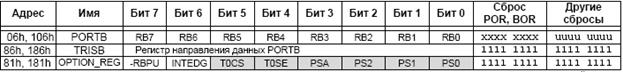

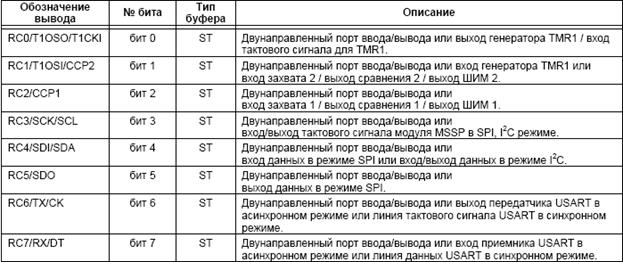

На рис.8.11 представлено функциональное назначение битов PORTB, а на рис.8.12 – регистры и биты, связанные с работой порта.

Рис.8.11 - функциональное назначение битов порта

Рис.8.12 – регистры и биты, связанные с работой порта

Регистры PORTC и TRISC

PORTС – 8 разрядный двунаправленный порт ввода / вывода. Регистр TRISС позволяет настроить соответствующий канал порта на вход или выход, подав на него '1' или '0' соответственно.

Выводы PORTC мультиплицированы с несколькими периферийными модулями. На каналах PORTC присутствует входной буфер с триггером Шмидта.

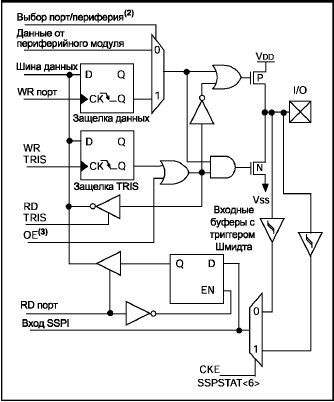

Когда модуль MSSP включен в режиме I2C, выводы PORTC <4:3> могут поддерживать уровни выходных сигналов по спецификации I2C или SMBus в зависимости от состояния бита CKE(SSPSTAT<6>).

При использовании периферийных модулей необходимо соответствующим образом настраивать биты регистра TRISC для каждого вывода PORTC. Некоторые периферийные модули отменяют действие битов TRISC, принудительно настраивая вывод на вход или выход. В связи с чем, не рекомендуется использовать команды "чтение - модификация - запись" с регистром TRISC.

На рис.8.13 изображена структурная схема выводов RC7:RC5, RC2:RC0, а на рис.8.14 – структурная схема выводов RC4:RC3.

Рис.8.13 - структурная схема выводов RC7:RC5, RC2:RC0

Рис.8.14 - структурная схема выводов RC4:RC3

На рис.8.15 представлено функциональное назначение битов PORTC, а на рис.8.16 – регистры и биты, связанные с работой порта.

Рис.8.15 - функциональное назначение битов PORTC

Рис.8.16 - регистры и биты, связанные с работой порта

Регистры PORTD и TRISD

PORTD – 8 разрядный двунаправленный порт ввода / вывода. Регистр TRISD позволяет настроить соответствующий канал порта на вход или выход, подав на него '1' или '0' соответственно. PORTD может работать как 8-разрядный микропроцессорный порт (ведомый параллельный порт), если бит PSPMODE (TRISE<4>) установлен в '1'. В режиме ведомого параллельного порта к входам подключены буферы TTL.

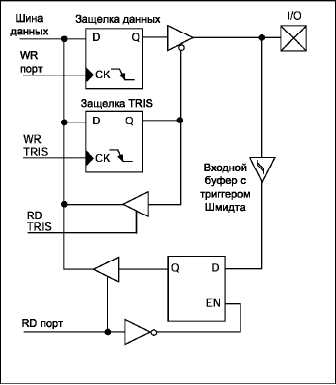

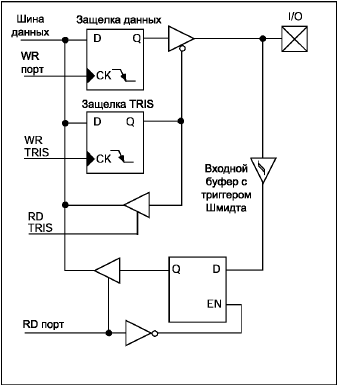

На рис.8.17 представлена функциональная схема выводов PORTD, а точнее режим цифрового порта ввода / вывода.

Рис.8.17 - функциональная схема выводов PORTD

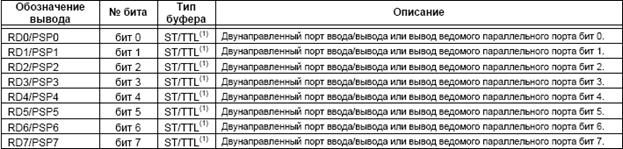

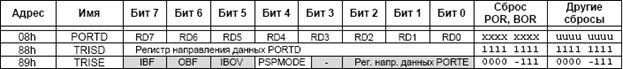

На рис.8.18 представлено функциональное назначение битов PORTD, а на рис.8.19 – регистры и биты, связанные с работой порта.

Рис.8.18 - функциональное назначение битов PORTD

Рис.8.19 - регистры и биты, связанные с работой порта

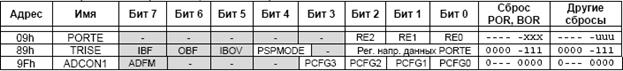

Регистры PORTE и TRISE

PORTE имеет три вывода (RE0/-RD/AN5, RE1/-WR/AN6, RE2/-CS/AN7), индивидуально настраиваемые на вход или выход. Выводы PORTE имеют входной буфер Шмидта.

Каналы PORTE станут управляющими выводами ведомого параллельного порта, когда бит PSPMODE(TRISE<4>) установлен в '1'. В этом режиме биты TRISE<2:0> должны быть установлены в '1'. В регистре ADCON1 необходимо также настроить выводы PORTE как цифровые каналы ввода/вывода.

В режиме ведомого параллельного порта к выводам PORTE подключены входные буферы TTL. Выводы PORTE мультиплицированы с аналоговыми входами. Когда каналы PORTE настроены как аналоговые

входы, биты регистра TRISE управляют направлением данных PORTE (чтение будет давать результат '0').

На рис.8.20 представлена структурная схема выводов PORTE, а точнее режим цифрового порта ввода / вывода.

Рис.8.20 - структурная схема выводов PORTE

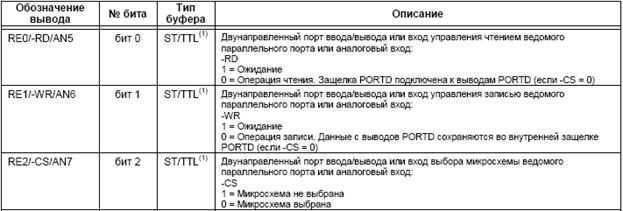

На рис.8.21 представлено функциональное назначение битов PORTE, а на рис.8.22 – регистры и биты, связанные с работой порта.

Рис.8.21 - функциональное назначение битов PORTE

Рис.8.22 - регистры и биты, связанные с работой порта

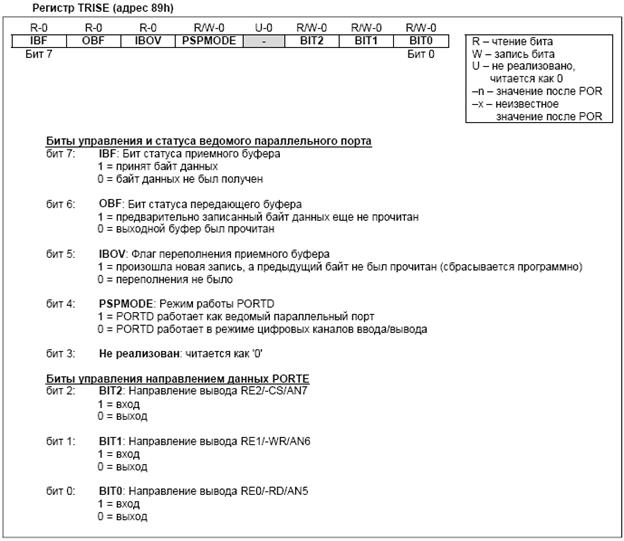

Регистр TRISE имеет особое назначение, в отличие от других регистров, так что заслуживает внимания. Описание битов представлено на рис.8.23.

Рис.8.23 – управляющий регистр TRISE

Информация о регистрах контроля и управления портами ввода / вывода представлена для ознакомления. Вы всегда сможете обратиться к официальной документации, если вдруг решите всерьёз заняться программированием МК.

Автор решил, что описание портов PORTF, PORTG, GPIO не будет включено в данный раздел, так как не относится к последующим лабораторным работам. Ещё раз просмотрите сначала весь материал, представленный о двунаправленных портах ввода / вывода, и постарайтесь отметить для себя важные моменты. Перед тем, как приступить к выполнению лабораторной работы – следует познакомиться с инструментами, которые предоставляет нам интегрированная среда разработки, для отладки и тестирования. Если кажется, что программирование портов ввода / вывода сложная и трудновыполнимая задача, то вы серьёзно ошибаетесь. Арсенал методов и настроек для каждого из портов, конечно же велик, но быть может вы никогда не воспользуетесь и половиной предоставленного.

|

|

|

Историки об Елизавете Петровне: Елизавета попала между двумя встречными культурными течениями, воспитывалась среди новых европейских веяний и преданий...

Автоматическое растормаживание колес: Тормозные устройства колес предназначены для уменьшения длины пробега и улучшения маневрирования ВС при...

Механическое удерживание земляных масс: Механическое удерживание земляных масс на склоне обеспечивают контрфорсными сооружениями различных конструкций...

История развития хранилищ для нефти: Первые склады нефти появились в XVII веке. Они представляли собой землянные ямы-амбара глубиной 4…5 м...

© cyberpedia.su 2017-2026 - Не является автором материалов. Исключительное право сохранено за автором текста.

Если вы не хотите, чтобы данный материал был у нас на сайте, перейдите по ссылке: Нарушение авторских прав. Мы поможем в написании вашей работы!