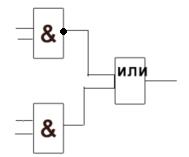

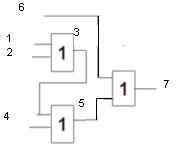

Задача №4

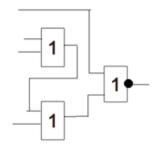

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. Каждый логический элемент д.б. описан как отдельный объект, т.е. описание в целом д.б. выполнено в структурном стиле.

Решение

-- Интерфейс "И"

entity entity_and is port (in1, in2: in BIT; q: out BIT); end entity_and;

-- Архитектура "И"

architecture architecture_and of entity_and is begin

q<=in1 and in2;

end architecture_and;

-- Интерфейс "И-НЕ"

entity entity_and_not is port (in1, in2: in BIT; q: out BIT); end entity_and_not;

-- Архитектура "И-НЕ"

architecture architecture_and_not of entity_and_not is begin

q<= not (in1 and in2);

end architecture_and_not;

-- Интерфейс компонента "ИЛИ"

entity entity_or is port (in1, in2: in bit; q: out bit); end entity_or;

-- Архитектура компонента "ИЛИ"

architecture architecture_or of entity_or is begin

q<=in1 or in2;

end architecture_or;

-- Интерфейс основного компонента

entity entity_main is port (i1,i2,i3,i4:in bit; QQ: out BIT); end entity_main;

-- Архитектура основного компонента

architecture architecture_main of entity_main is

component entity_and port (in1, in2: in BIT; q: out BIT); end component;

component entity_and_not port (in1, in2: in BIT; q: out BIT); end component;

component entity_or port (in1, in2: in BIT; q:out BIT); end component;

signal q1,q2: BIT;

begin

label1: entity_and_not port map (i1,i2,q1);

label2: entity_and port map (i3,i4,q2);

label3: entity_or port map (q1,q2,QQ);

end architecture_main;

В поведенческом стиле

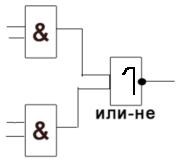

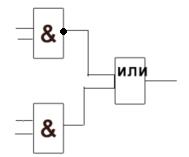

Задача №5

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. Описание в целом д.б. выполнено в поведенческом стиле.

Решение

-- Интерф основного компонента

entity entity_main is

port (i1, i2, i3, i4: in BIT;

QQ: out BIT);

end entity_main;

-- Архитектура осн. компонента -

architecture architecture_main of entity_main is

begin

QQ<=not((i1 and i2) or (i3 and i4));

end architecture_main;

Исп комп эл «ИЛИ»

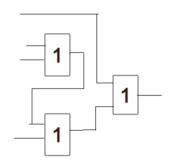

Задача №6

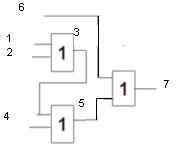

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. При описании архитектуры используйте компонент элемента “ИЛИ” и оператор конкретизации компонента.

Решение

-- Интерфейс компонента “ИЛИ”

entity entity_or is

port (in1, in2: in bit;

q: out bit);

end entity_or;

-- Архитектура компонента “ ИЛИ ”

architecture architecture_or of entity_or is begin

q<=in1 or in2;

end architecture_or;

-- Интерфейс основного компонента

entity entity_main is

port (i1, i2, i3, i4: in BIT;

QQ: out BIT);

end entity_main;

-- Архитектура основного компонента

architecture architecture_main of entity_main is

component entity_or

port (in1, in2: in BIT;

q: out BIT);

end component;

signal q1,q2: BIT;

begin

label1: entity_or

port map (i2, i3, q1);

label2: entity_or

port map (q1, i4, q2);

label3: entity_or

port map (i1, q2, QQ);

end architecture_main;

Исп комп эл «ИЛИ» и «ИЛИ-НЕ»

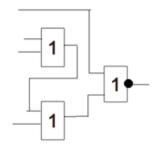

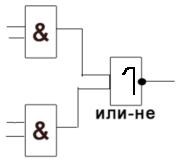

Задача №7

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. При описании архитектуры используйте компонент элемента “ИЛИ” и “ИЛИ-НЕ” и оператор конкретизации компонента.

Решение

-- Интерфейс компонента “ИЛИ”

entity entity_or is

port (in1, in2: in bit; q: out bit);

end entity_or;

-- Архитектура компонента “ИЛИ”

architecture architecture_or of entity_or is begin

q<=in1 or in2;

end architecture_or;

-- Интерфейс компонента “ИЛИ-НЕ”

entity entity_or_not is

port (in1, in2: in bit; q: out bit);

end entity_or_not;

-- Архитектура компонента “ИЛИ-НЕ”

architecture architecture_or_not of entity_or_not is begin

q<=not (in1 or in2);

end architecture_or_not;

-- Интерфейс основного компонента

entity entity_main is

port (i1, i2, i3, i4: in BIT; QQ: out BIT);

end entity_main;

-- Архитектура основного компонента

architecture architecture_main of entity_main is

component entity_or

port (in1, in2: in BIT; q: out BIT);

end component;

component entity_or_not

port (in1, in2: in BIT; q: out BIT);

end component;

signal q1,q2: BIT;

begin

label1: entity_or port map (i2, i3, q1);

label2: entity_or port map (q1, i4, q2);

label3: entity_or_not port map (i1, q2, QQ);

end architecture_main;

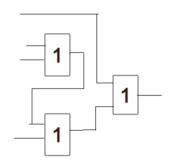

8 Оператор generate

Задача №8

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. При описании архитектуры используйте оператор generate.

Решение

-- Интерфейс компонента "ИЛИ"

entity entity_or is

port (in1, in2: in bit; q: out bit);

end entity_or;

-- Архитектура компонента "ИЛИ"

architecture architecture_or of entity_or is begin

q<=in1 or in2;

end architecture_or;

-- Интерфейс основного компонента

entity entity_main is

port (inp: in BIT_VECTOR (1 to 4);

QQ: out BIT);

end entity_main;

-- Архитектура основного компонента

architecture architecture_main of entity_main is

component entity_or

port (in1, in2: in BIT; q: out BIT);

end component;

signal qi: BIT_VECTOR (1 to 7);

begin

qi(1)<=inp(2);

qi(2)<=inp(3);

qi(4)<=inp(4);

qi(6)<=inp(1);

q1: for i in 1 to 3 generate

label1: entity_or

port map (qi(2*i-1), qi(2*i), qi(2*i+1));

end generate;

QQ<= qi(7);

end architecture_main;