Особенности сооружения опор в сложных условиях: Сооружение ВЛ в районах с суровыми климатическими и тяжелыми геологическими условиями...

Семя – орган полового размножения и расселения растений: наружи у семян имеется плотный покров – кожура...

Особенности сооружения опор в сложных условиях: Сооружение ВЛ в районах с суровыми климатическими и тяжелыми геологическими условиями...

Семя – орган полового размножения и расселения растений: наружи у семян имеется плотный покров – кожура...

Топ:

Методика измерений сопротивления растеканию тока анодного заземления: Анодный заземлитель (анод) – проводник, погруженный в электролитическую среду (грунт, раствор электролита) и подключенный к положительному...

Комплексной системы оценки состояния охраны труда на производственном объекте (КСОТ-П): Цели и задачи Комплексной системы оценки состояния охраны труда и определению факторов рисков по охране труда...

Характеристика АТП и сварочно-жестяницкого участка: Транспорт в настоящее время является одной из важнейших отраслей народного...

Интересное:

Как мы говорим и как мы слушаем: общение можно сравнить с огромным зонтиком, под которым скрыто все...

Принципы управления денежными потоками: одним из методов контроля за состоянием денежной наличности является...

Инженерная защита территорий, зданий и сооружений от опасных геологических процессов: Изучение оползневых явлений, оценка устойчивости склонов и проектирование противооползневых сооружений — актуальнейшие задачи, стоящие перед отечественными...

Дисциплины:

|

из

5.00

|

Заказать работу |

|

|

|

|

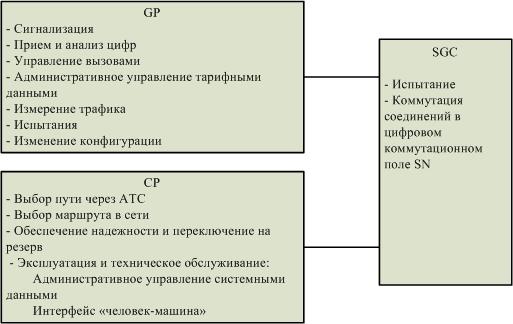

Рисунок 2.11 – Структура управляющей системы

Верхний уровень управления представлен координационным процессором CP, который взаимодействует с групповыми процессорами GP линейных групп через каналы коммутационного поля. Распределение функций между CP и GP показано на рисунке 2.12. Для организации взаимодействия CP и GP в линии SDC каждой линейной группы выделен нулевой канал. Процессор GP, в свою очередь, взаимодействует с контроллерами абонентских блоков через каналы 64 кбит/c линий PDC.

Рисунок 2.12 – Распределение функций между процессорами

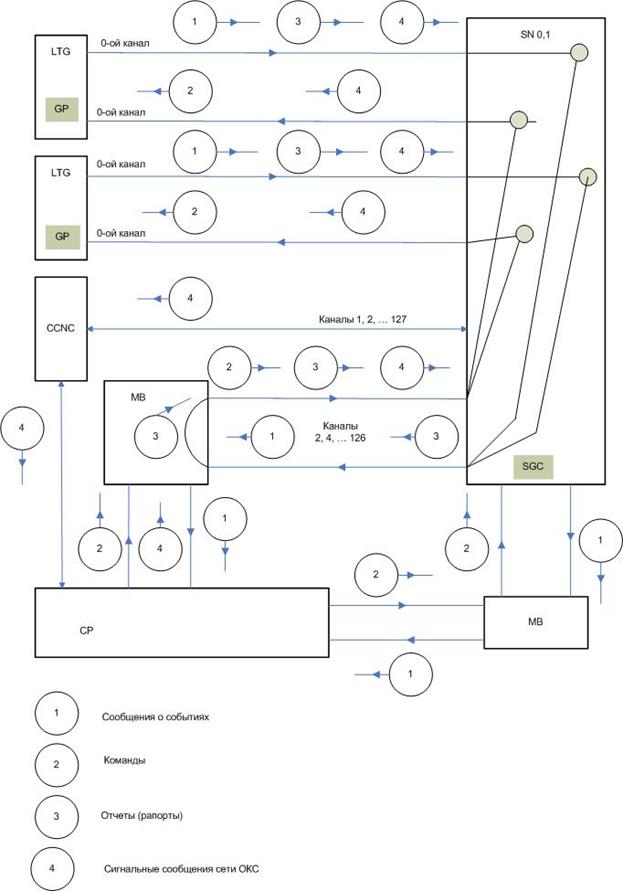

2.6. 2. Все устройствасоединяются с полем SN по линиям SDC с потоком 8,192 Мбит/c (128 каналов по 64 кбит/c каждый). Нулевые каналы SDC задействуются для образования внутренних каналов передачи данных между GP разных LTG, между GP и СР (рисунок 2.13). Управление межпроцессорным обменом обеспечивает буфер сообщений МВ.

По внутренним каналам межпроцессорного обмена передаются следующие виды данных:

· сообщения о событиях (от GP LTG к CP, от SGC к СР);

· команды – указания на действия (от CP к GP LTG, от СР к SGC);

· рапорты – квитанции (отчеты) о выполненных действиях (между GP разных LTG);

· сигнальные сообщения ОКС№7 (между CP и ССNC, между GP LTG и CCNC).

Каждый GP LTG отправляет свои сообщения и рапорты в нулевом канале SDC. В коммутационном поле эта информация от 63-х LTG мультиплексируется в 2, 4 …126 каналы и поступает в буфер сообщений МВ, который производит сортировку данных. Сообщения о событиях направляются в CP, а рапорты, по возможности, перенаправляются в LTG, минуя СР.

Сигнальным трафиком ОКС№7 управляет CCNC (рисунок 2.14), который выполняет функции подсистемы передачи сообщений МТР, а также часть функций подсистемы управления сигнальным соединением SCCP. При использовании SSNC (сетевой контроллер системы сигнализации) все сигнальные сообщения ОКС№7 обрабатываются без участия СР.

|

|

Рисунок 2.13 – Взаимодействие CP и GP

Рисунок 2.14 – Организация взаимодействия по ОКС для оконечного пункта (входящее соединение)

Каналы передачи сигнальной информации 64 кбит/c подключаются к CCNC через линейные группы LTG и полупостоянные соединения в коммутационном поле. CCNC соединяется с коммутационным полем линиями SDC (8,192 Мбит/c).

2.6.3 В системе EWSD V.15 используются два типа координационных процессора CP113D и CP113C/CR. Процессоры CP113C/CR входят в состав станций большой емкости в сочетании с буфером сообщений MBD, коммутационным полем SN(D) и контроллером системы сигнализации ОКС№7 SSNC. Процессоры CP113D применяются на станциях меньшей емкости в сочетании с буфером сообщений МВВ, коммутационным полем SN(B) и управляющим устройством сигнализации ОКС№7 CCNC.

Координационный процессор CP выполняет функции обработки вызовов, технической эксплуатации, обеспечения надежности.

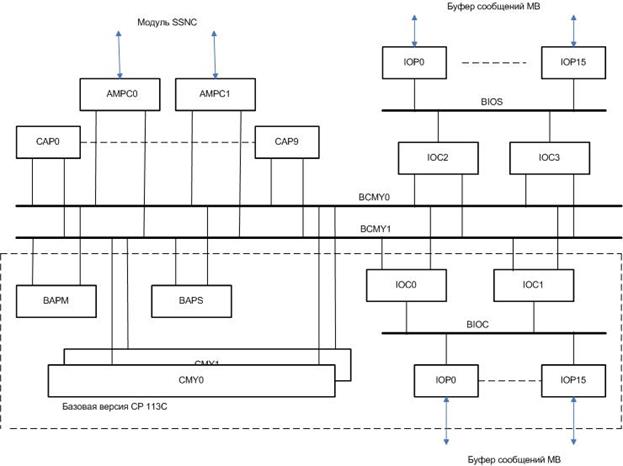

В состав CP входят (рисунок 2.15):

· BAP – базовый процессор, выполняющий функции обработки вызовов и технической эксплуатации;

· CAP – сопроцессор обработки вызовов;

· IOP – процессор ввода/вывода, управляет обменом данными с оборудованием коммутационной станции и периферийными устройствами технической эксплуатации ОА&М;

· CMY – общая память для хранения общей базы данных, списков ввода/выводадля интерфейсовIOP:MB и информации, используемой процессорами IOP для обмена данными с периферийными устройствами технической эксплуатации ОА&М;

· BCMY – шина общей памяти для межпроцессорной связи и реализации процедур обращения кCMY;

· IOC – контроллер ввода/вывода, образует интерфейс между шиной общей памятиBCMY и процессором IOP.

Кроме того, CP113C/CR содержит мостовой АТМ-процессор (процессор асинхронного режима передачи) типа C (АМРС), который является интерфейсом с сетевым контроллером SSNC.

|

|

Для повышения надежности все наиболее важные блоки координационного процессора дублируются.

Конфигурация координационного процессора зависит от требуемой производительности (таблица 2.6).

Таблица 2.6 – Комплектация CP 113

| Виды процессоров | Тип CP 113 | ||

| CP 113С | CP 113D | CP 113CR | |

| Максимальное количество процессоров | |||

| BAP | 2 | 2 | 2 |

| CAP | 10 | 10 | - |

| IOC | 4 | 4 | 2 |

| IOP | 64 | 64 | 32 |

| АМРС | 2 | 2 | 2 |

Во всех конфигурациях присутствуют два основных процессора ВАР:

· ведущий ВАРМ, выполняющий функции обработки вызовов и технической эксплуатации,

· ведомый ВАР S, который в нормальном режиме выполняет функции только обработки вызовов.

|

|

|

Механическое удерживание земляных масс: Механическое удерживание земляных масс на склоне обеспечивают контрфорсными сооружениями различных конструкций...

Состав сооружений: решетки и песколовки: Решетки – это первое устройство в схеме очистных сооружений. Они представляют...

История создания датчика движения: Первый прибор для обнаружения движения был изобретен немецким физиком Генрихом Герцем...

Двойное оплодотворение у цветковых растений: Оплодотворение - это процесс слияния мужской и женской половых клеток с образованием зиготы...

© cyberpedia.su 2017-2024 - Не является автором материалов. Исключительное право сохранено за автором текста.

Если вы не хотите, чтобы данный материал был у нас на сайте, перейдите по ссылке: Нарушение авторских прав. Мы поможем в написании вашей работы!