В этой теме приведена методика синтеза комбинационных логических устройств и алгоритмы работы шифратора (CD), дешифратора (DC), мультиплексора (MS), демультиплексора (DMS), цифрового компаратора (СА) и сумматора (SM), рассмотрены особенности выполнения операций сложения и вычитания бинарных чисел.

Установочная лекция 8

Дидактические единицы:

Алгоритм синтеза комбинационных логических устройств (КЛУ).

1.2. Преобразователи кодов (CD, DC, MS, DMS, СА и CM ).

Операции сложения и вычитания бинарных чисел.

1.4.Операция «Исключающее ИЛИ-НЕ ».

1.5.Полусумматоры и сумматоры ( SM).

СОДЕРЖАНИЕ

ОБЩИЕ ПРИНЦИПЫ ПОСТРОЕНИЯ КЛУ

Алгоритм синтеза КЛУ

Согласно приведенной ранее классификации логических устройств отличительной особенностью комбинационных устройств (КЛУ) является выражаемая в виде таблицы истинности однозначная связь входных и выходных кодовых слов (чисел). Поэтому таблица истинности и соответствующие ей ФАЛ позволяют однозначно определить алгоритм работы устройства, провести анализ и синтезировать его логическую схему.

Построение КЛУ ведут в следующей последовательности:

· составляют таблицу истинности, характеризующую алгоритм работы синтезируемого устройства,

· получают минимальную дизъюнктивную форму (МДФ) записи ФАЛ, описывающую работу устройства,

· приводят логические элементы МДФ к единому базису,

· синтезируют схему устройства.

Во многих случаях при проектировании комбинационных устройств используют однотипные алгоритмы, реализация которых привела к созданию класса типовых устройств. К ним в первую очередь относят (кроме основных и базисных логических элементов): шифраторы (CD), дешифраторы (DC), мультиплексоры (MS), демультиплексоры (DMS), цифровые компараторы (устройства сравнения (СА)) и сумматоры (SM). Эти узлы являются микросхемами, но могут быть изготовлены на основе нескольких более простых в функциональном отношении ИС.

Рассмотрим свойства и алгоритмы типовых комбинационных устройств.

Шифратор

В цифровой технике используют различные методы кодирования информации. Задача преобразования одного вида кода в другой вид решается посредством устройств, называемых преобразователями кодов. Основой для разработки таких устройств являются их таблицы истинности.

Ввиду большого разнообразия видов кодирования, преобразователи кодов, как правило, не выпускаются в виде готовых интегральных схем, а проектируют по приведенной выше методике. Одним из преобразователей кодов является шифратор.

Шифратор (СD) или кодер – комбинационное логическое устройство, преобразующее унитарный n код в двоичный код (унитарный код содержит единицу только в одном разряде).

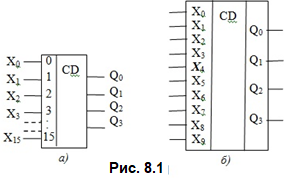

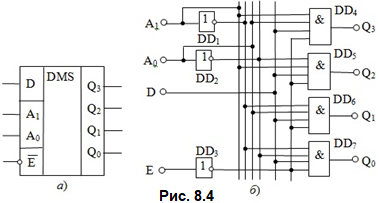

Классический шифратор имеет n входов и m выходов (m < n), и при подаче сигнала на один из входов (и не более) на выходе логической схемы появляется двоичный код номера активированного входа. Число входов и выходов такого шифратора связано соотношением n = 2 m. Условное графическое изображение на схемах шифратора 16×4 (читается “шестнадцать в четыре”) показано на рис. 8.1 а.

При подаче сигнала 1, например, на вход Х 3, на выходе получим двоичный код (шифр) Q 3 Q 2 Q 1 Q 0 = 00112, при подаче 1 на вход Х 12 – код 11002 и т.д.

Области использования шифраторов: отображение в виде двоичного кода номера нажатой кнопки или положения многопозиционного переключателя, номера устройства, подавшего сигнал на обслуживание в микропроцессорных системах и т.п. Шифраторы входят в состав микросхем контроллеров прерываний.

В качестве примера рассмотрим преобразователь 10-разрядного унитарног о кода в двоичный, который может быть использован для ввода десятичных чисел с клавиатуры в ЭВМ.

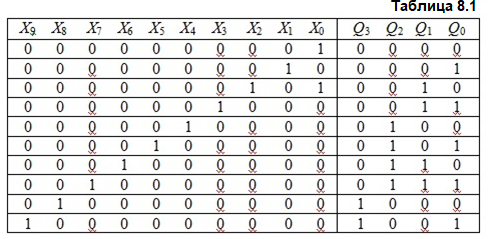

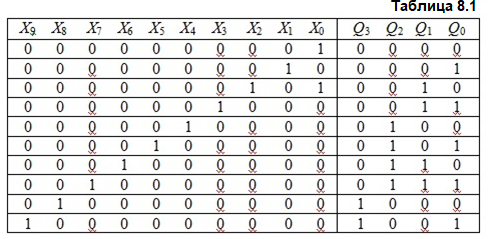

Появление сигнала логической единицы в одном из разрядов входного кода соответствует вводу определенной десятичной цифры. Алгоритм работы такого шифратора (преобразователя кода 10×4), приведен в таблице истинности (табл. 8.1), а его условное графическое и буквенное обозначения – на рис. 8.1 б.

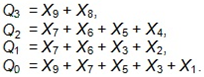

Используя приведенную таблицу, составим систему ФАЛ, по которой синтезируют в заданном базисе логическую схему шифратора:

Дешифратор

Дешифратор (DC) или декодер – комбинационное логическое устройство с п входами и m выходами (m > n), предназначенное для преобразования двоичных входных п- кодов (кодовых слов) в унитарный код.

По определению дешифратор относится к классу преобразователей кодов. В дешифраторе каждому входному двоичному числу ставится в однозначное соответствие сигнал, формируемый на определенном выходе устройства (на всех остальных выходах дешифратора выходные сигналы равны нулю), т.е. дешифратор выполняет преобразование сигнала, обратное шифратору.

Дешифратор используют, когда нужно обращаться к различным цифровым устройствам. При этом номер устройства – его адрес представлен двоичным кодом.

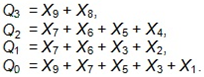

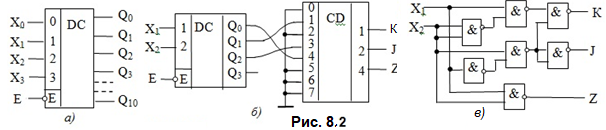

Полный дешифратор содержит число выходов, равное числу комбинаций входных переменных, например, при п = 4, m = 2 п = 16: от Q 0 = X̅ 3 X̅ 2 X̅ 1 X̅ 0 до Q 15 = X 3 X 2 X 1 X 0. Когда ряд комбинаций на входе не используется, то получают неполный дешифратор (m < 2 n) с меньшим числом выводов. Примером неполного дешифратора является двоично-десятичный дешифратор, который для 4-разрядного адресного кода формирует только 10 выходных сигналов (рис. 8.2 а).

Дешифраторы часто снабжают инверсным разрешающим (управляющим) входом E̅. При E̅ = 0 дешифратор функционирует как обычно, a при E̅ = 1 на всех выводах устанавливается 0 независимо от поступающего кода на входе. Таблица истинности дешифратора может быть получена из таблицы истинности шифратора (см. табл. 8.1) при замене входных сигналов выходными и наоборот.

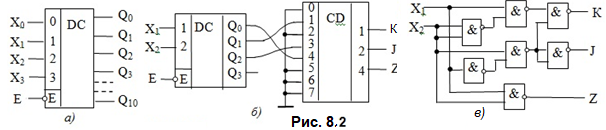

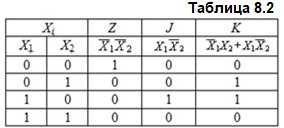

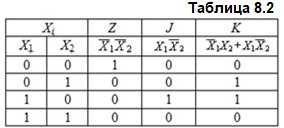

Для решения многих конкретных задач необходимо синтезировать преобразователи разных кодов. В качестве примера, на рис. 8.2 б представлена схема кодового преобразователя, состоящая из пары DС–CD, реализующая логику работы некоторого трёхцветного светофора К (красный), J (желтый) и Z (зелёный свет), управляемого двухразрядным двоичным кодом Хi в соответствии с заданной таблицей истинности (табл. 8.2).

Число входов дешифратора DC равно двум (X 1 и X 2), число выходов – трем (Q 0, Q 1 и Q 2). Соединение дешифратора и шифратора выполнено в соответствии с ФАЛ (см. табл. 8.2). Часть выходов DC и входов СD не используется.

Проектирование кодовых преобразовательной схемы на паре декодер-кодер иногда оказывается более выгодным и по числу микросхем, и по быстродействию, чем при ее проектировании на основе логических микросхем, например на базе элементов И-НЕ (рис. 8.2 в).

Затраты времени инженера на логическое проектирование по схеме декодер-кодер неизмеримо меньше, чем затраты на проектирование преобразователя из россыпи. Однако потребляемая мощность в этом случае может оказаться больше, чем у схемы из отдельных элементов.

Мультиплексор

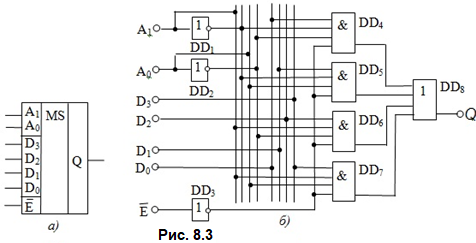

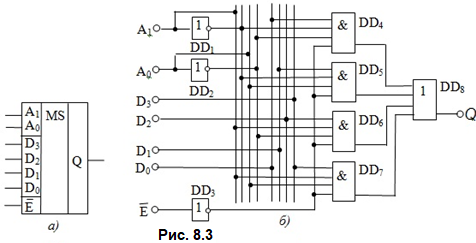

Мультиплексор (MS) – комбинационное логическое устройство, осуществляющее управляемое подключение (коммутацию) одного из нескольких источников информации (одного из входов) к единственному выходу (рис. 8.3 a).

Мультиплексор имеет две группы входов: адресные Ai и информационные Di, и один выход Q. Двоичный код, подаваемый на адресные входы, определяет, какой из информационных входов Di должен быть подключен к выходу. Поскольку n -разрядный двоичный код, подаваемый на адресные входы мультиплексора, может принимать 2 n значений, то число информационных входов также должно быть равно 2 n.

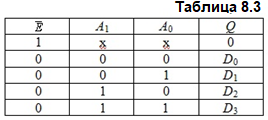

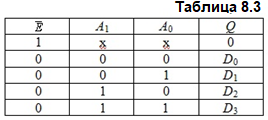

Алгоритм работы мультиплексора, управляемого двухразрядным кодом A 1 A 0 адреса, отражен в таблице истинности (табл. 8.3).

Мультиплексор обычно снабжают инверсным входом разрешения работы, позволяющим блокировать его работу при E̅ = 1.

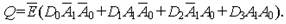

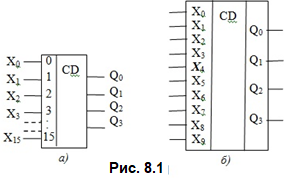

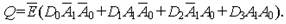

Воспользовавшись таблицей истинности мультиплексора, запишем ФАЛ, описывающую его работу:

Ф ункциональная логическая схема MS, реализующая записанный выше ФАЛ), представлена на рис. 8.3 б.

Обычно число входов мультиплексоров, выпускаемых в виде готовых интегральных схем, не превышает 16. При необходимости иметь большее число информационных входов Di, используют структуру так называемого мультиплексорного дерева. В ней выходные сигналы мультиплексоров нижнего уровня, управляемых младшими разрядами адресного слова A 1 A 0, являются входными для мультиплексора верхнего уровня, управляемого разрядами адресного слова A 3 A 2 и т.д.

Демультиплексор

Демультиплексор (DMS) – комбинационное логическое устройство, предназначенное для управляемой передачи данных от одного источника информации в несколько выходных каналов, т.е. демультиплексор выполняет преобразование сигнала, обратное мультиплексору. Поэтому при управлении n -разрядным адресным словом Аi он имеет один информационный вход D и 2 n выходов Qi.

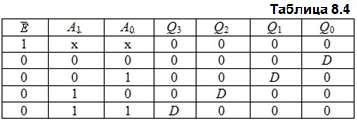

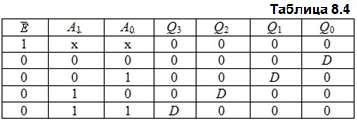

Алгоритм работы демультиплексора, управляемого двухразрядным адресным словом А 1 А 0, приведен в таблице истинности (табл. 8.4).

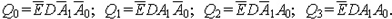

Этой таблице соответствует система из четырех ФАЛ:

В ФАЛ учтено наличие инверсного входа разрешения работы E̅.

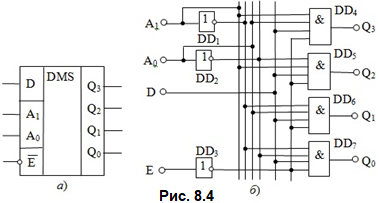

Н а рис. 8.4 показаны условное графическое обозначение (a) и комбинационная логическая схема (б) демультиплексора.

Чтобы увеличить число выходов устройства до требуемого значения, на базе демультиплексоров строят демультиплексорное дерево. При этом выходные сигналы DMS первого уровня используются для формирования сигнала E̅ разрешения работы демультиплексоров второго уровня.

Цифровой компаратор