Ктн, доц. В.Л. Савиных,

http://studopedia.ru/7_28905_osnovnie-opredeleniya.html

Закон двойственности (Правило де Моргана)

(1.11)

(1.11)

На основании правила де Моргана логическое сложение может быть заменено умножением и, наоборот, при соответствующем инвертировании переменных и всей логической функции.

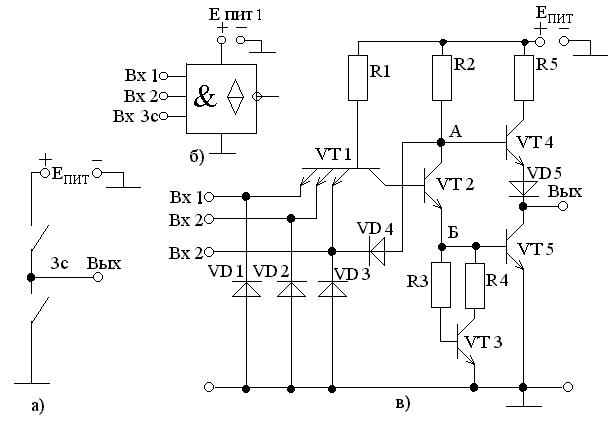

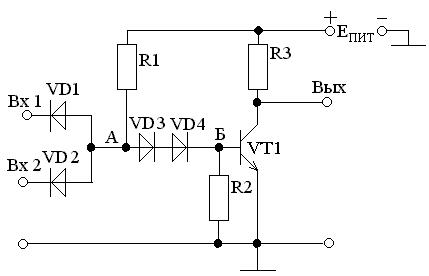

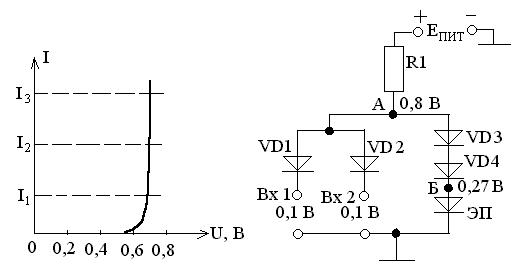

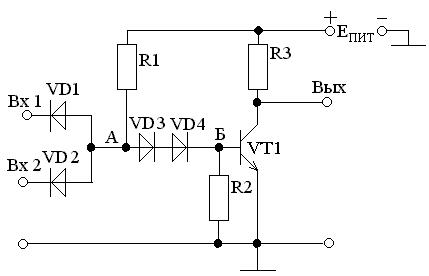

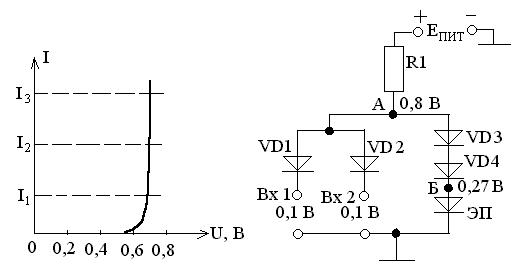

| Принципиальная схема диодно-транзисторной логики (ДТЛ) изображена на рисунке 1.5. Число входов можно увеличить, подключая диоды параллельно VD1 и VD2, но в этом случае усложнится анализ схемы.

Рисунок 1.5

Предположим, что ЕПИТ =5 В. Тогда, если БТ закрыт (ток через него отсутствует), напряжение на выходе будет равно 5 В, что соответствует логической ²1² (U1=5 B). Если БТ находится в режиме насыщения, то на его выходе будет напряжение примерно равное 0,1 В, это соответствует логическому ²0² (U0=0,1 B). Принцип работы схемы поясним при помощи таблицы 1.7

Если на оба входа подано напряжение U0=0,1 В (рисунок 1.6 б), тогда напряжение в точке А будет равно UА=0,8 В. Оно состоит из входного напряжения U0 и падения напряжения на диоде, которое примерно равно |

Таблица 1.7

| Вх 1

| Вх 2

| UВХ 1, В

| UВХ 2, В

| UА, В

| UБ, В

| БТ

| UВЫХ, В

| Вых

|

|

|

| 0,1

| 0,1

| 0,8

| 0,27

| Закр

|

|

|

|

|

| 0,1

|

| 0,8

| 0,27

| Закр

|

|

|

|

|

|

| 0,1

| 0,8

| 0,27

| Закр

|

|

|

|

|

|

|

| 2,1

| 0,7

| Откр

| 0,1

|

|

0,7 В. Характеристика диода, выполненного на основе кремния, приведена на рисунке 1.6 а. Из рисунка видно, что при различных токах I1, I2, I3 падение напряжения на диоде примерно составляет 0,7 В.

Предполагая, что все три pn-перехода VD 3, VD 4 и эмиттерный переход (ЭП) транзистора одинаковы, получаем напряжение на базе транзистора (точка Б) составляет UБ =UА/3» 0,27 В. Входная характеристика транзистора соответствует характеристики pn-перехода (рисунок 1.6а), и, следовательно, ток базы отсутствует, ток коллектора равен нулю, транзистор закрыт. Напряжение на выходе будет около 5 В. Падением напряжения на резисторе R3 за счет тока IКЭ0 можно пренебречь. Это напряжение соответствует логической ²1². (Первая строчка таблицы).

а) б)

Рисунок 1.6

При подаче на вход 1 логической ²1² диод VD 1 будет включен в обрат- ном направлении, ток от источника питания будет проходить через диод VD 2 и напряжение в точке А будет по прежнему равно 0,8 В. Как и в преды -дущем случае транзистор будет закрыт и напряжение на выходе будет соот- ветствовать логической ²1². (Вторая и аналогично третья строчки таблицы).

При подаче на оба входа логической ²1²диоды VD 1 и VD 2 будут включены в обратном направлении, через них будет протекать обратный ток. Основной ток в этом случае протекает через VD 3, VD 4 и эмиттерный пере- ход транзистора. На каждом из pn-переходов падает напряжение 0,7 В (UА=2,1 В). Резистор R1выбирается таким образом, чтобы транзистор находился в режиме насыщения и тогда напряжение на его коллекторе составит примерно равно 0,1 В, что соответствует логическому ²0² (четвертая строчка таблицы).

Сравнивая два первых и последний столбцы таблицы видим, что данная схема выполняет логическую операцию И-НЕ.

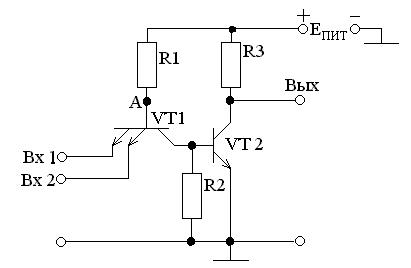

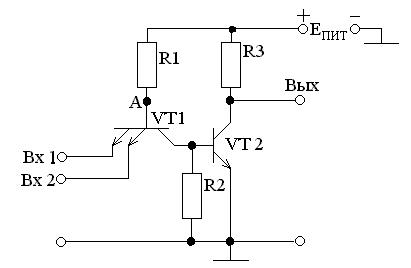

Если в предыдущей схеме ДТЛ диоды VD 1, VD 2 и VD 3 заменить на двухэмиттерный транзистор, то получится транзисторно – транзисторная логика (ТТЛ), принципиальная схема которой приведена на рисунке 1.11.

Рисунок 1.11

В качестве VT1 можно использовать транзистор с большим числом эмиттеров, схема в этом случае будет иметь соответствующее число входов.

Принцип работы, таблица истинности и характеристики ТТЛ такие же, как у ДТЛ.

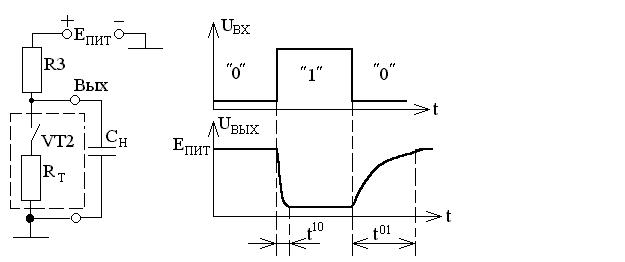

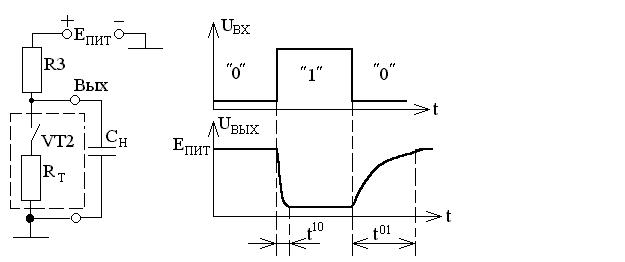

Недостаток предыдущих схем заключается в следующем. Заменим транзистор VT2 ключом с сопротивлением RТ (рисунок 1.12а).

В исходном состоянии (на входе схемы логический ²0²), транзистор закрыт (ключ разомкнут), на выходе напряжение равно напряжению питания ЕПИТ (рисунок 1.12б). При подаче на вход логической ²1²ключ замыкается. В этом случае ёмкость нагрузки СН разряжается через малое сопротивление ключа RT и время включения будет составлять t10. При подаче на вход логического²0² ключ вновь размыкается и, в этом случае, ёмкость СН будет заряжаться через сопротивление R3, которое намного больше, чем RT и время выключения будет t01> t10, из-за этого быстродействие схемы будет низким.

а) б)

Рисунок 1.12

Кроме того между точкой А и общим проводом находятся два pn-перехода, следовательно на эмиттерном переходе при подаче на вход логического ²0² напряжение будет составлять 0,4 В и для того, чтобы открыть транзистор надо приложить меньшее напряжение, т.е. помехо-устойчивость схемы снижается.

Задача состоит в том, чтобы снизить t01 (t01» t10) и повысить помехоустойчивость.

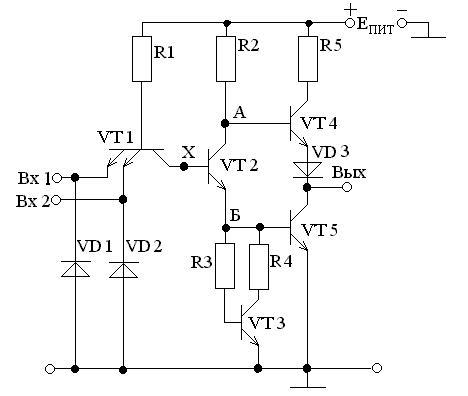

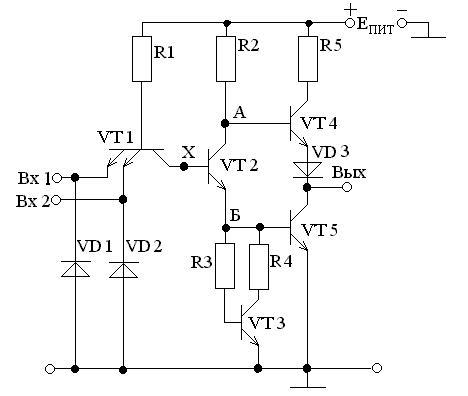

Типовая схема ИМС со сложным инвертором представлена на рисунке 1.13. Принцип работы схемы поясним с помощью таблицы 1.7. Если в точке Х (Х=Х1×Х2) низкий потенциал (на входе присутствует хотя бы один логический ²0²), то транзистор VT2 закрыт и ток через него отсутствует.

Таблица 1.7

| Х

| VT2

| UА, В

| UБ, В

| VT4

| VT5

| UВЫХ

| Y

|

|

| закр

|

|

| откр

| закр

| 3,8

|

|

|

| откр

| 0,8

| 0,7

| закр

| откр

| 0,1

|

|

В этом случае потенциал в точке А будет около 5 В, а в точке Б UБ» 0 В (токами IКЭ0 и I Б4 пренебрегаем). Транзистор VT4 будет открыт, а тран-зистор VT5 будет закрыт. Следовательно, на выходе будет логическая ²1².

Рисунок 1.13

Если в точке Х будет высокий потенциал (на входах логические ²1²), то транзистор VT2 находится в режиме насыщения, через него протекает ток. В точке Б напряжение будет равно UБ= 0,7 В (падение напряжения на открытом эмиттерном переходе VT5), а в точке А UА= 0,8 В (добавляется 0,1 В, которое на выходе).

В этом случае транзистор VT5 открыт, а транзистор VT4 закрыт. Причина того, транзистор VT4 закрыт, следующая. Между точкой А и выходом напряжение равно примерно 0,7 В (0,1 В падает на VT5. Это напряжение распределяется между двумя pn-переходами (эмиттерный переход VT4 и диод VD3). Считая, что переходы одинаковы, получаем на эмиттерном переходе VT4 напряжение равно 0,35 В. А этого недостаточно, чтобы открыть транзистор VT4. Следовательно, на выходе будет логический ²0². Так как ёмкость нагрузки будет заряжаться и разряжаться через малое сопротивление транзисторов, то время включения t10 и выключения t01 будут приблизительно одинаковы (резистор R5 имеет малую величину 20-50 Ом и служит для ограничения тока в момент переключения).

Диоды VD1 и VD2 – антизвонные, служат для исключения переходных процессов на входе. Элементы R3, R4 и VT3 служат для получения более крутой характеристики прямой передачи (в момент перехода с уровня логической ²1² в логический ²0²) и термостабилизации.

Входная характеристика такая же, как у ДТЛ. Характеристика прямой передачи отличается от характеристики ДТЛ тем, что уровень логического нуля составляет около 4 В.

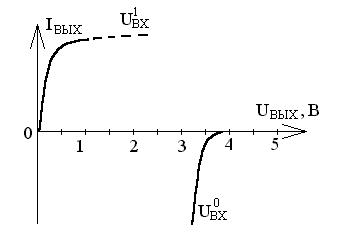

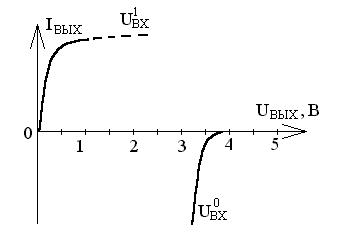

Выходная характеристика изображена на рисунке 1.14.

При подаче на вход U1ВХ открыт транзистор VT5 и при увеличении напряжения на выходе, т.е. на его коллекторе характеристика совпадает с выходной характеристикой транзистора. Выходную характеристику при U0ВХ лучше рассматривать при снижении напряжения на выходе. При снижении напряжения от 5 В до 3,8 В открываются оба pn-перехода (эмиттерный

Рисунок 1.14

переходVT4 и диод VD3) и при дальнейшем снижении напряжения ток возрастает из-за увеличения тока базы транзистора VT4.

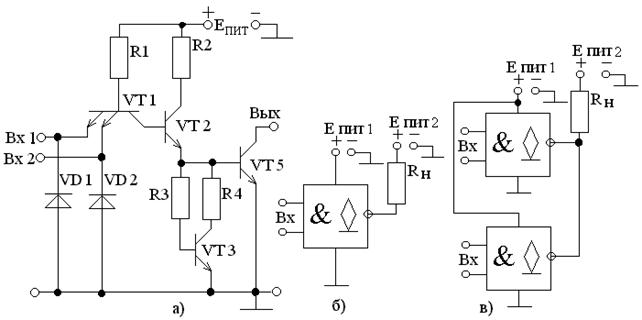

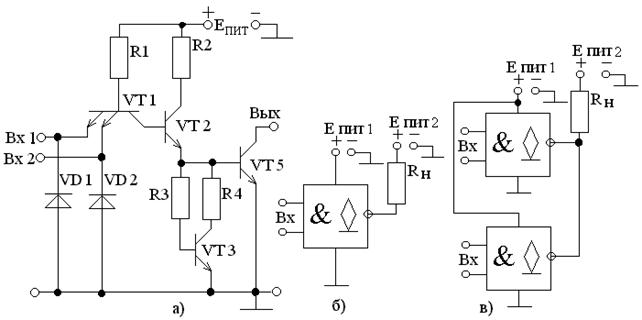

Схема с открытым коллекторным выходом используется для подключения нестандартной нагрузки (светодиодов, реле, нагрузки с повышенным напряжением питания и т. д.). Принципиальная схема приведена на рисунке 1.15а. Отличием от предыдущей является то, что в ней отсутствуют элементы VT4, VD3 и R5.

На рисунке 1.15б приведено условное обозначение схемы И-НЕ с

Рисунок 1.15

открытым коллекторным выходом (значок  ), к нему подключена нагрузка RН с источником питания Е ПИТ2. Источник питания Е ПИТ2 в некоторых схемах может достигать 30 В.

), к нему подключена нагрузка RН с источником питания Е ПИТ2. Источник питания Е ПИТ2 в некоторых схемах может достигать 30 В.

На рисунке 1.15в показано включение двух схем на общую нагрузку (монтажное ИЛИ).

Принцип работы схем с тремя состояниями на выходе поясняется рисунком 1.16а. Если верхний ключ замкнут, а нижний разомкнут, то на выходе будет логическая ²1². Если наоборот – логический ²0². А если оба ключа разомкнуты (как показано на рисунке 1.16а), то это и будет третье состояние на выходе, т. е. выходное сопротивление равно бесконечности. Такие схемы позволяют соединять их выходы параллельно и работать на общую шину. Одна из схем работает в обычном режиме (на её выходе ²0² или ²1²), все остальные должны находиться в третьем состоянии. Условное обозначение схемы дано на рисунке 1.16б (значок  ). Принципиальная схема приведена на рисунке 1.16в.

). Принципиальная схема приведена на рисунке 1.16в.

Рисунок 1.16

Принцип работы схемы следующий. Если на вход 3с подать высокий потенциал (логическая ²1²), то третий эмиттерный переход VT1 и диод VD4

включены в обратном направлении, они не влияют на работу схемы и схема работает в обычном режиме выполняя операцию 2И-НЕ. При подаче на вход 3с низкого потенциала (логический ²0²), третий эмиттерный переход и диод VD4 открыты. Транзистор VT2 закрыт, в точке Б напряжение UБ=0, транзистор VT5 закрыт. В точке А напряжение будет составлять 0,8 В. Оно склады- вается из входного напряжения, равного 0,1 В и падения напряжения на диоде VD4, равного 0,7 В. Как было рассмотрено выше транзистор VT4 будет закрыт (т.е. оба ключа разомкнуты) и схема находится в третьем состоянии.

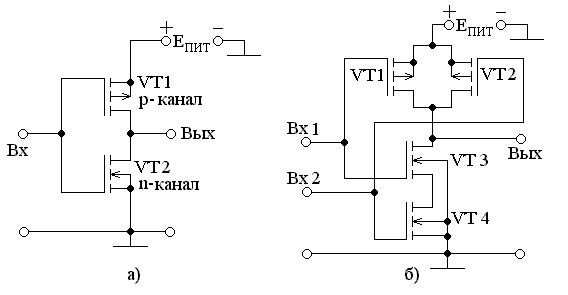

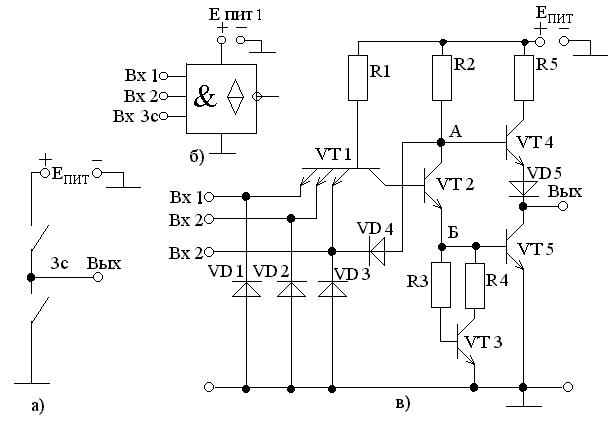

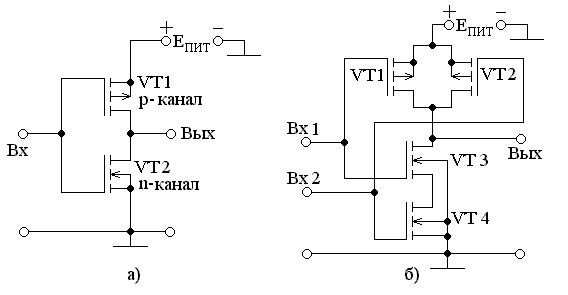

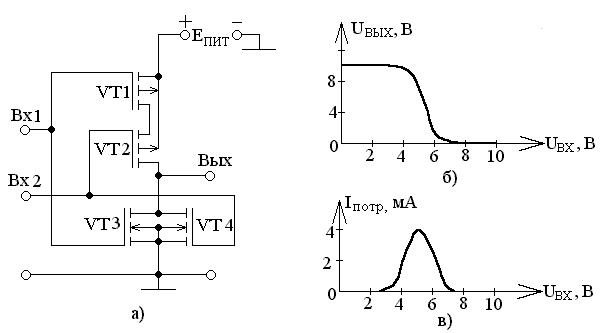

| Комплиментарная МДП (КМДП) логика включает в себя пары p- и n-канальных полевых транзисторов с индуцированным каналом. Простейшая схема, выполняющая операцию НЕ представлена на рисунке 1.18а.

Рисунок 1.18

Принцип её работы поясним с помощью таблицы 1.10.

Таблица 1.10

| Вх

| UВХ, В

| VT1

| VT2

| IС

| UВЫХ, В

| Вых

| |

|

| Откр

| Закр

|

|

|

| |

|

| Закр

| Откр

|

|

|

| Предположим, что напряжение питания равно ЕПИТ=10 В. Как будет показано ниже напряжение U0=0 В, а U1=10 В. Пороговое напряжение, подаваемое на затвор, у таких транзисторов составляет примерно UЗИ ПОРОГ » 4 В. Тогда при подаче на вход напряжения логического ²0² (первая строчка таблицы) транзистор VT2 будет закрыт, а транзистор VT1 будет открыт. Так как напряжение между его затвором и истоком, который соединен с подложкой, равно UЗИ=-10 В, а пороговое напряжение для р-канального транзистора составляет UЗИ ПОРОГ »-4 В. Поскольку транзистор VT2 закрыт, ток стока IС=0. Напряжение на выходе составит UВЫХ= 10 В и, следовательно, это соответствует логической ²1².

При подаче на вход логической ²1² U1=10 В (вторая строчка таблицы) транзистор VT1 будет закрыт, поскольку напряжение между его затвором и истоком составляет UЗИ=0 В, а транзистор VT2 будет открыт. Так как транзистор VT1 закрыт, ток стока так же будет равен IС=0. Напряжение на выходе составит UВЫХ= 0 В и, следовательно, это соответствует логическому ²0². Таким образом, в статическом состоянии ток через схему отсутствует за исключением тока утечки, который составляет единицы мкА.

Рассмотрим схему, приведенную на рисунке 1.18б. Принцип её работы также поясним с помощью таблицы 1.11.

Таблица 1.11

| Вх 1

| Вх 2

| UВХ 1, В

| UВХ 2, В

| VT1

| VT2

| VT3

| VT4

| I

| UВЫХ, В

| Вых

| |

|

|

|

| Откр

| Откр

| Закр

| Закр

|

|

|

| |

|

|

|

| Закр

| Откр

| Откр

| Закр

|

|

|

| |

|

|

|

| Откр

| Закр

| Закр

| Откр

|

|

|

| |

|

|

|

| Закр

| Закр

| Откр

| Откр

|

|

|

| При подаче на оба входа логического ²0², как было рассмотрено выше транзисторы VT1 и VT2 открыты, а транзисторы VT3 и VT4 закрыты. На выходе будет высокий потенциал и ток через схему отсутствует (первая строчка таблицы 1.11).

При подаче на вход хотя бы одной логической ²1² один из транзисторов VT3 или VT4 открывается, а один из транзисторов VT1 или VT2 закрывается. Поскольку один из транзисторов закрыт VT3 или VT4, то ток через схему отсутствует, а на выходе будет высокий потенциал, т.е. логическая ²1² (вторая и третья строка таблицы).

При подаче на оба входа логических ²1² оба транзистора VT3 и VT4 открыты, а транзисторы VT1 и VT2 закрыты. На выходе будет логический ²0² и ток через транзисторы по-прежнему отсутствует (четвертая строчка таблицы). Таким образом, данная схема выполняет операцию И-НЕ. В статическом режиме она не потребляет тока.

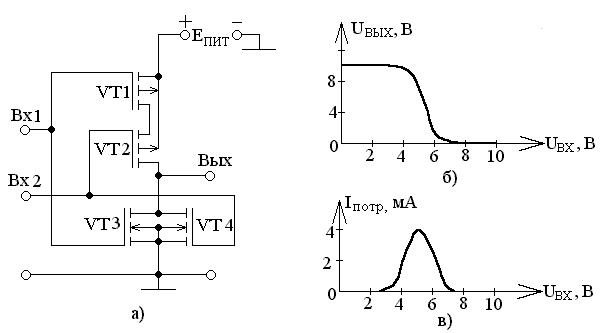

Схема ИЛИ-НЕ представлена на рисунке 1.19а, а её принцип работы поясним с помощью таблицы 1.12.

Таблица 1.12

| Вх 1

| Вх 2

| UВХ 1, В

| UВХ 2, В

| VT1

| VT2

| VT3

| VT4

| I

| UВЫХ, В

| Вых

| |

|

|

|

| Откр

| Откр

| Закр

| Закр

|

|

|

| |

|

|

|

| Закр

| Откр

| Откр

| Закр

|

|

|

| |

|

|

|

| Откр

| Закр

| Закр

| Откр

|

|

|

| |

|

|

|

| Закр

| Закр

| Откр

| Откр

|

|

|

| В этом случае, в отличие от предыдущего, при подаче на один из входов логической ²1²(вторая и третья строчки таблицы) на выходе будет логический ²0², так как один из транзисторов VT1 и VT2 закрыт, а один из транзисторов VT3 или VT4 открыт, т.е. на выходе будет нулевой потенциал.

Рисунок 1.19

Характеристики КМДП

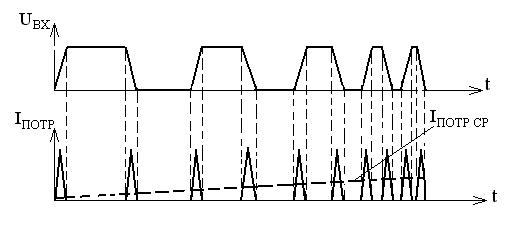

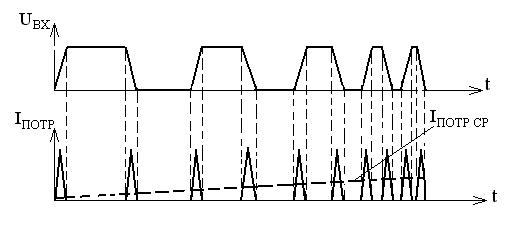

Характеристика прямой передачи приведена на рисунке 1.19б. При подаче низкого потенциала на вход, как было показано выше, на выходе будет высокий потенциал (логическая ²1²). Увеличивая напряжения на входе (при достижении порогового напряжения) открываются транзисторы VT3 и VT4 и начинают закрываться транзисторы VT1 и VT2, напряжение на выходе падает до нуля. Аналогично можно и объяснить характеристику тока потребления от входного напряжения (рисунок 1.19в), т.е. при напряжении от 3 до 7 вольт все транзисторы ²приоткрыты² и в этом случае через схему протекает ток. Это приводит к тому, что при увеличении частоты переключения средний ток, потребляемый схемой, увеличивается (рисунок 1.20) и на высоких частотах он может сравняться с током потребления ТТЛ и ТТЛШ.

Рисунок 1.20

Ниже приведены параметры некоторых серий микросхем КМДП. Средний ток потребления от источника питания IПОТР СР приведен в статическом режиме. Из таблицы видно, что с совершенствованием технологии растут энергетические показатели.

Таблица 1.13

|

| Серия

| | Параметры

|

|

|

|

| | ЕПИТ, В

|

|

|

|

| | IПОТР СР, мкА

|

| 1,5

| 1,25

|

| | tЗДР СР, нс

|

|

|

|

| | WДЖ, 10-12

| 4,4

| 1,65

| 0,1125

| 0,04

|

|

D-триггер: принцип работы, таблица истинности - Читайте подробнее на FB.ru: http://fb.ru/article/116811/d-trigger-printsip-rabotyi-tablitsa-istinnosti#image270132

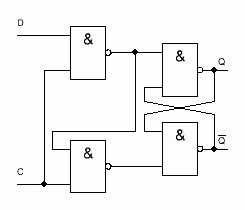

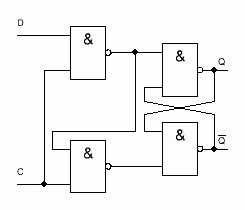

Триггер – элементарное устройство, представляющее собой цифровой автомат с двумя состояниями устойчивости, одному из которых присваивается значение «1», а другому - «0». По способу реализации логических связей различают следующие виды устройств: T-триггер, D-триггер, JK-триггер, RS-триггеры. Естественно, здесь перечислены наиболее распространенные варианты, но кроме них существуют автоматические устройства и других типов. В этой статье мы более подробно рассмотрим D-триггер. Упомянутый автомат имеет один-единственный информационный (D) вход, таким образом, он предназначен для реализации функции временной задержки. D-триггер -

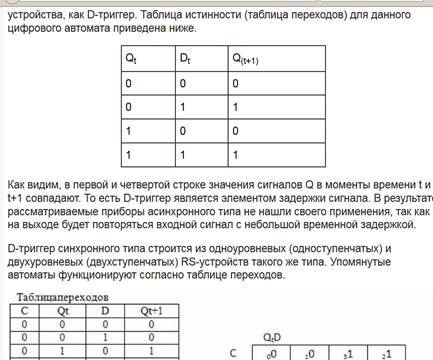

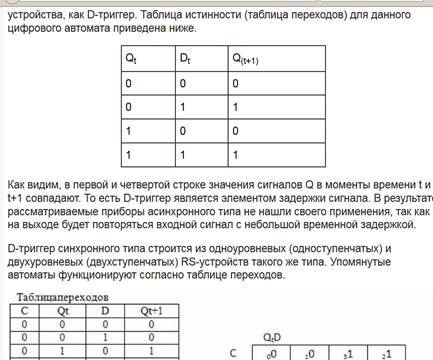

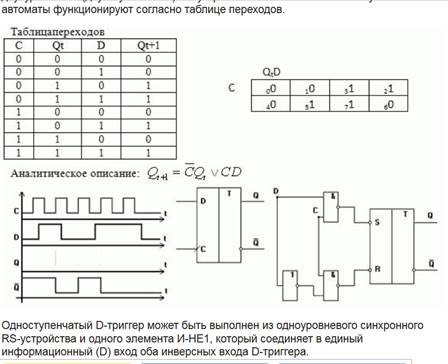

Принцип работы Характеристическое уравнение Q(t+1)=Dt описывает функционирование такого типа устройства, как D-триггер. Таблица истинности (таблица переходов) для данного цифрового автомата приведена ниже.

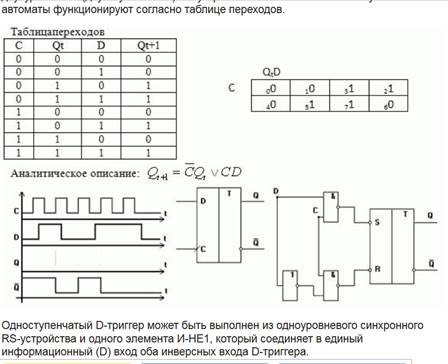

Как видим, в первой и четвертой строке значения сигналов Q в моменты времени t и t+1 совпадают. То есть D-триггер является элементом задержки сигнала. В результате рассматриваемые приборы асинхронного типа не нашли своего применения, так как на выходе будет повторяться входной сигнал с небольшой временной задержкой. D-триггер синхронного типа строится из одноуровневых (одноступенчатых) и двухуровневых (двухступенчатых) RS-устройств такого же типа. Упомянутые автоматы функционируют согласно таблице переходов.

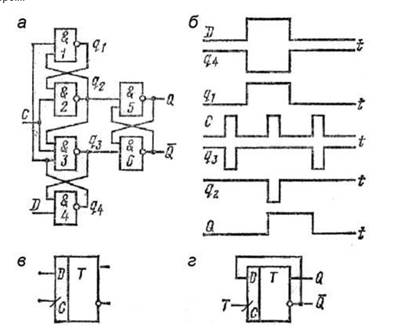

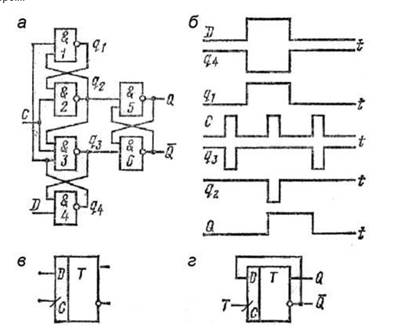

Одноступенчатый D-триггер может быть выполнен из одноуровневого синхронного RS-устройства и одного элемента И-НЕ1, который соединяет в единый информационный (D) вход оба инверсных входа D-триггера. При поступлении логического нуля на синхронизирующий вход автомат типа RS заблокирован уровнем логической единицы с выходов элементов И-НЕ2 и И-НЕ3. При смене сигнала синхронизации уровень, поданный на информационный вход, создаст логический нуль либо на входе S (при D=1), либо на входе R (при D=0) асинхронного триггера Т. Он переключится в состояние, соответствующее логическому уровню D. Одноступенчатый триггер D-типа задерживает распространение входного на время паузы между синхронизирующими сигналами. D-триггер с динамическим управлением. Описание работы, функциональная схема Автоматическое устройство такого вида конструируется из трех RS-триггеров асинхронного типа. Они построены на элементах И-НЕ, при этом два из них выполняют коммутирующую функцию, а третий является выходным. Выходные сигналы коммутирующих триггеров предназначены для управления выходным триггером.

При уровне сигнала С, равного логическому нулю, на входы выходного триггера поступает нейтральная для него комбинация сигналов, и он переключается в режим хранения. При изменении информационного сигнала коммутирующие триггеры переходят в режим ожидания, и как только поступает сигнал логической единице на разрешающий вход триггера С, выходной автомат устанавливается в новое состояние, которое соответствует информационному сигналу на D-входе в предыдущем такте. В случае если изменение уровня информационного сигнала пройдет в период установки выходного триггера, тогда коммутирующие устройства сигнал не пропустят. Получается, что цель коммутирующих триггеров заключается в приеме информационных сигналов, передаче их на вход выходного прибора в момент перемены сигнала на управляющем входе С от логического нуля к логической единице и самоблокировки от воздействия сигнала на информационном входе. - Читайте подробнее на FB.ru: http://fb.ru/article/116811/d-trigger-printsip-rabotyi-tablitsa-istinnosti#image270126

Базовые понятия

Триггер — это запоминающий элемент с двумя (или более) устойчивыми состояниями, изменение которых происходит под действием входных сигналов и предназначен для хранения одного бита информации, то есть лог. 0 или лог. 1.

Все разновидности триггеров представляют собой элементарный автомат, включающий собственно элемент памяти (ЭП) и комбинационную схему (КС), которая может называться схемой управления или входной логикой (рис. 7).

Рис. 7 структура триггеров в виде КС и ЭП

В графе триггера каждая вершина графа соединена со всеми другими вершинами, при этом переходы от вершины к вершине возможны в обе стороны (двухсторонние). Граф двоичного триггера — две точки соединённые отрезком прямой линии, троичного триггера — треугольник, четверичного триггера — квадрат с диагоналями, пятеричного триггера — пятиугольник с пентаграммой и т.д. При N=1 граф триггера вырождается в одну точку, в математике ему соответствует унарная единица или унарный ноль, а в электронике — монтажная «1» или монтажный «0», то есть простейшее ПЗУ. Устойчивые состояния имеют на графе триггера дополнительную петлю, которая обозначает, что при снятии управляющих сигналов триггер остаётся в установленном состоянии.

Состояние триггера определяется сигналами на прямом и инверсном выходах. При положительном кодировании (позитивная логика) высокий уровень напряжения на прямом выходе отображает значение лог. 1 (состояние = 1), а низкий уровень — значение лог. 0 (состояние = 0). При отрицательном кодировании (негативная логика) высокому уровню (напряжению) соответствует логическое значение «0», а низкому уровню (напряжению) соответствует логическое значение «1».

Изменение состояния триггера (его переключение или запись) обеспечивается внешними сигналами и сигналами обратной связи, поступающими с выходов триггера на входы схемы управления (комбинационной схемы или входной логики). Обычно внешние сигналы, как и входы триггера, обозначают латинскими буквами R, S, T, C, D, V и др. В простейших схемах триггеров отдельная схема управления (КС) может отсутствовать. Поскольку функциональные свойства триггеров определяются их входной логикой, то названия основных входов переносятся на всю схему триггера.

Входы триггеров разделяются на информационные (R, S, T и др.) и управляющие (С, V). Информационные входы предназначены для приёма сигналов запоминаемой информации. Названия входных сигналов отождествляют с названиями входов триггера. Управляющие входы служат для управления записью информации. В триггерах может быть два вида управляющих сигналов:

- синхронизирующий (тактовый) сигнал С, поступающий на С-вход (тактовый вход);

- разрешающий сигнал V, поступающий на V-вход.

На V-входы триггера поступают сигналы, которые разрешают (V=1) или запрещают (V=0) запись информации. В синхронных триггерах с V-входом запись информации возможна при совпадении сигналов на управляющих С и V-входах.

Работа триггеров описывается с помощью таблицы переключений, являющейся аналогом таблицы истинности для комбинационной логики. Выходное состояние триггера обычно обозначают буквой Q. Индекс возле буквы означает состояние до подачи сигнала (t) либо (t-1) или после подачи сигнала (t+1) или (t). В триггерах с парафазным (двухфазным) выходом имеется второй (инверсный) выход, который обозначают как Q, /Q или Q'.

Кроме табличного определения работы триггера существует формульное задание функции триггера в секвенциальной логике. Например, функцию RS-триггера в секвенциальнойлогике представляет формула (x ¯ ∨ x ∠ y) {\displaystyle \left({\bar {x}}\lor x\,\angle \,y\right)}. Аналитическая запись SR-триггера выглядит так: Q = S ∨ S ¯ ∠ R ¯ {\displaystyle Q=S\lor {\overline {S}}\,\angle \,{\overline {R}}}.

Типы триггеров

RS-триггеры

RS-триггер асинхронный

| S

| R

| Q(t)

| Q(t)

|

| 0

| 1

| 0

| 1

|

| 1

| 0

| 1

| 0

|

| 0

| 0

| 0

| 0

|

| 1

| 1

| 1

| 1

|

Асинхронный RS-триггер с инверсными входами

RS-триггер [10][11], или SR-триггер (от англ. Set/Reset — установить/сбросить — асинхронный триггер, который сохраняет своё предыдущее состояние при неактивном состоянии обоих входов и изменяет своё состояние при подаче на один из его входов активного уровня. При подаче на оба входа активного уровня состояние триггера вообще говоря неопределённо, но в конкретных реализациях на логических элементах оба выхода принимают состояния либо логического нуля, либо логической 1. В зависимости от конкретной реализации активным входным уровнем может быть как логическая 1, так и логический 0. Так, в RS-триггере выполненном на 2 элементах 2И-НЕ активным входным уровнем является логический 0.

При подаче активного уровня на вход S (от англ. Set — установить) выходное состояние становится равным логической единице. А при подаче активного уровня на вход R (от англ. Reset — сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы активные уровни не определено и зависит от реализации, например в триггере на элементах «или-не» оба выхода переходят в состояние логической 1, которое сохраняется пока на входах удерживаются логические 0. Перевод одного из входов в неактивное состояние, в данном примере в логическую 1, переводит триггер в одно из разрешённых устойчивых состояний. Одновременный перевод обоих входов из активного в неактивное состояние вызывает непредсказуемое переключение триггера в одно из устойчивых состояний.

В некоторой литературе триггеры, у которых документировано, какое именно состояние на выходах соответствует одновременным активным уровням на входах (т. е. RS-триггеры, у которых запрещённое состояние доопределено тем или иным образом), называются Rs, rS или даже R- и S-триггеры, по названию того входа, который является приоритетным. Тем не менее, выход из доопределённого состояния должен всё равно производиться последовательным (не одновременным) переводом входов в неактивное состояние, с соблюдением паспортных задержек (соответствующих физическому быстродействию триггера).

RS-триггер используется для формирования сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством подачи импульсов на входы, которые разнесены во времени. Также RS-триггеры часто используются для исключения ложного срабатывания цифровых устройств от так называемого «дребезга контактов».

RS-триггеры иногда называют RS-фиксаторами[12].

Условное графическое обозначение асинхронного RS-триггера.

Асинхронный RS-триггер на элементах 2И–НЕ.

Граф (математика) переходов асинхронного RS-триггера.

Карта Карно асинхронного RS-триггера.

Асинхронный RS-триггер на элементах 2ИЛИ-НЕ.

- Схема устранения дребезга контактов.

RS-триггер синхронный

| C

| S

| R

| Q(t)

| Q(t+1)

|

| 0

| x

| x

| 0

| 0

|

| 1

| 1

|

| 1

| 0

| 0

| 0

| 0

|

| 1

| 0

| 0

| 1

| 1

|

| 1

| 0

| 1

| 0

| 0

|

| 1

| 0

| 1

| 1

| 0

|

| 1

| 1

| 0

| 0

| 1

|

| 1

| 1

| 0

| 1

| 1

|

| 1

| 1

| 1

| 0

| не определено

|

| 1

| 1

| 1

| 1

| не определено

|

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1.

Алгоритм функционирования синхронного RS-триггера можно представить формулой

Q (t + 1) = R ¯ ⋅ (Q (t) + S) + x ⋅ S ⋅ R, {\displaystyle Q(t+1)={\overline {R}}\cdot \left(~Q(t)+S~\right)+x\cdot S\cdot R,}

где x — неопределённое состояние.

Аналогично, триггер с доопределённым состоянием (Rs или rS) допускает наличие двух активных сигналов на момент тактирования, и переключается согласно тому сигналу, который для него является приоритетным.

Условное графическое обозначение синхронного RS-триггера.

Схема синхронного RS-триггера на элементах 2И-НЕ.

Граф переходов синхронного RS-триггера.

Карта Карно синхронного RS-триггера.

D-триггеры

D-триггеры также называют триггерами задержки(от англ. Delay).

D-триггер синхронный

Пример условного графического обозначения (УГО) D-триггера с динамическим синхронным входом С и с дополнительными асинхронными инверсными входами S и R

| D

| Q(t)

| Q(t+1)

|

| 0

| 0

| 0

|

| 0

| 1

| 0

|

| 1

| 0

| 1

|

| 1

| 1

| 1

|

D-триггер (D от англ. delay — задержка [13][14][15], либо от data [16] — данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом С информация записывается в течение времени, при котором уровень сигнала C=1. В триггерах с динамическим входом С информация записывается только в течение перепада напряжения на входе С. Динамический вход изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы (прямой динамический вход), то триггер срабатывает по фронту входного импульса, если от неё (инверсный динамический вход) — по срезу импульса. В таком триггере информация на выходе может быть задержана на один такт по отношению к входной информации.Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

Условное графическое обозначение D-триггера со статическим входом синхронизации С

D-триггер двухступенчатый

В одноступенчатом триггере имеется одна ступень запоминания информации, при этом, в состоянии записи триггер "прозрачен", т.е. все изменения на входе триггера повторяются на выходе триггера, что может привести к ложным срабатываниям устройств стоящих после триггера. В двухступенчатом триггере две ступени. Вначале информация записывается в первую ступень, все изменения на входе триггера во вторую ступень до сигнала перезаписи не попадают, затем, после перехода D-триггера первой ступени в режим хранения, информация переписывается во вторую ступень и появляется на выходе, что позволяет избежать состояния "прозрачности". Двухступенчатый триггер обозначают ТТ. Если первая ступень двухступенчатого D-триггера выполнена на статическом D-триггере, то двухступенчатый D-триггер называют двухступенчатым D-триггером со статическим управлением, а если на динамическом D-триггере, то двухступенчатый D-триггер называют двухступенчатым D-триггером с динамическим управлением.

T-триггеры

Т-триггер (от англ. Toggle — переключатель) часто называют счётным триггером, так как он является простейшим счётчиком до 2.

Т-триггер асинхронный

Асинхронный Т-триггер не имеет входа разрешения счёта - Т и переключается по каждому тактовому импульсу на входе С.

T-триггер синхронный

| T

| Q(t)

| Q(t+1)

|

| 0

| 0

| 0

|

| 0

| 1

| 1

|

| 1

| 0

| 1

|

| 1

| 1

| 0

|

Условное графическое обозначение (УГО) синхронного T-триггера с динамическим входом синхронизации С на схемах.

Синхронный Т-триггер [17], при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер можно построить на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе.

Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К.

В двухступенчатом (Master-Slave, MS) D-триггере инверсный выход Q соединяется со входом D, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение Q, то есть будет переключаться в противоположное состояние.

Работа схемы асинхронного двухступенчатого T-триггера с парафазным входом на двух парафазных D-триггерах на восьми логических вентилях 2И-НЕ. Слева — входы, справа — выходы. Синий цвет соответствует 0, красный — 1

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

JK-триггер

JK-триггер с дополнительными асинхронными инверсными входами S и R

| J

| K

| Q(t)

| Q(t+1)

|

| 0

| 0

| 0

| 0

|

| 0

| 0

| 1

| 1

|

| 0

| 1

| 0

| 0

|

| 0

| 1

| 1

| 0

|

| 1

| 0

| 0

| 1

|

| 1

| 0

| 1

| 1

|

| 1

| 1

| 0

| 1

|

| 1

| 1

| 1

| 0

|

JK-триггер [18][19] работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное, т.е. выполн

(1.11)

(1.11)

), к нему подключена нагрузка RН с источником питания Е ПИТ2. Источник питания Е ПИТ2 в некоторых схемах может достигать 30 В.

), к нему подключена нагрузка RН с источником питания Е ПИТ2. Источник питания Е ПИТ2 в некоторых схемах может достигать 30 В. ). Принципиальная схема приведена на рисунке 1.16в.

). Принципиальная схема приведена на рисунке 1.16в.