РАЗРАБОТКА КОММУТАТОРА ETHERNER 802.3 НА ЯЗЫКЕ ОПИСАНИЯ АППАРАТУРЫ VERILOG HDL

ОТЧЕТ

ПО РЕЗУЛЬТАТАМ

Производственной практики: практика по получению профессиональных умений и опыта профессиональной деятельности.

|

| Обучающийся гр. 1B7

_______________ Ковыляев А.Д.

(подпись)

_______________

(дата)

|

|

________

оценка

М.П.

| Руководитель практики от профильной организации:

Начальник отдела мультиплексорного оборудования департамента телекоммуникаций

_______________ Филатов Д.С.

(подпись)

_______________

(дата)

|

|

_________

оценка

| Руководитель практики от Университета:

Доцент, к.т.н.

_______________ Громов В.А.

(подпись)

_______________

(дата)

|

Томск 2019

Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное

учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР)

Кафедра радиотехнических систем

|

| УТВЕРЖДАЮ

Зав.кафедрой РТС

Мелихов С.В.

__________________

(подпись)

|

ЗАДАНИЕ

на производственную практику: практика по получению профессиональных умений и опыта профессиональной деятельности.

студенту гр. 1B7 радиотехнического факультета

Ковыляеву Алексею Дмитриевичу

1. Тема практики: разработка коммутатора ETHERNER 802.3 на языке описания аппаратуры VERILOG HDL;

2. Цель практики:

- Знакомство с предприятием «МИКРАН»;

- Знакомство с сетевыми технологиями передачи данных;

- Получить практические навыки в ходе работы над проектом;

3. Задачи практики:

- Ознакомиться с должностными инструкциями и обеспечением безопасности жизнедеятельности на предприятии;

- Изучение языка описания оборудование VERILOG HDL;

- Создание прототипа модульной схемы коммутатора по технологии

Ethernet 802.3;

- Написать отчёт по практике.

4. Исходные данные для практики:

4.1Методические указания по производственной практике для студентов - Томск 2018;

4.2https://edu.tusur.ru/publications/6159;

4.3ОС ТУСУР 01-2013.

5. Технические требования к отчету по практике: структура отчета должна соответствовать Положению о практиках, оформление отчета должно соответствовать требованиям ОС ТУСУР 01-2013, объем отчета не менее 30 страниц А4.

Дата выдачи: «24» июня 2019 г.

Руководитель практики от университета

| Доцент, к.т.н.

| ___________________

(Подпись)

| Громов В.А.

|

Согласовано:

Руководитель практики от профильной организации

| Начальник отдела мультиплексорного оборудования департамента телекоммуникаций

|

___________________

(Подпись)

|

Филатов Д.С.

|

Задание принял к исполнению «24» июня 2019 г.

| Студент гр.1B7

| ___________________

(Подпись)

| Ковыляев А.Д.

|

Реферат

Отчет по производственной практике, 33 с., 9 рис., 7 источников.

ЦИФРОВОЕ ТЕЛЕВЕЩАНИЕ, DVB-T/T2, ОДНОЧАСТОТНАЯ СЕТЬ, СДК, CONTROLCAST.

Цель производственной практики – реализация коммутатора Ethernet 802.3 на ПЛИС на языке описания аппаратуры Verilog HDL.

В процессе разработки применялись программы WireShark, modelsim, Quartus

Cодержание

Реферат. 3

Введение. 4

1 Ход работы.. 6

1.1 Подготовительный этап. 7

1.2 Захват пакетов в программе WireShark. Исследование на соответствие формату кадров IEEE 802.3(3.1.1) 9

2 Разработка коммутатора. 12

2.1 Формат пакета Ethernet 802.3: 12

2.2 Понятие контрольной суммы, виды, алгоритмы. Cyclic redundancy check (crc). CRC-32-IEEE 802.3 (0x04C11DB7) 13

2.3 Однопортовая\двухпортовая память. 15

2.4 FIFO и LIFO, кольцевой буфер. 15

2.5 Память для MAC-адресов. 16

2.6 Разработка архитектуры коммутатора. 18

2.7 Выделение функциональных модулей и их описание. 22

2.8 Взаимодействия модулей между собой. 24

2.9 Описание модулей. 25

Заключение. 30

Список использованных источников. 31

Введение

В данное время существует тенденция стремительного роста сетевого трафика, который становится непосильной нагрузкой на сетевое оборудование. Для решения этой проблемы производители повышают быстродействие, надежность и качество работы своего сетевого оборудования, за счет расширения функциональных возможностей. В частности, повышение работы коммутирующего оборудования достигалось за счет возможностей следующих уровней модели OSI. Так, коммутаторы сетевого уровня способны существенно изменить характер работы сети, являясь универсальным средством решения многих проблем вычислительных сетей.

Коммутатор – это устройство, обеспечивающее соединение узлов компьютерной сети для организации единой системы доступа пользователей к программным, техническим и информационным ресурсам. Узлом сети считается любое устройство с IP-адресом способное совершать обмен данными.

Основой для разработки коммутаторов послужила технология сетевого моста, которая подразумевает последовательную передачу пакетов информации. Коммутаторы, как устройства следующего поколения, обеспечивают одновременную передачу пакетов данных для всех своих портов.

Принцип работы коммутатора основывается на заполнении логической матрицы MAC-адресами в контентно-адресуемой памяти устройства. Каждый из адресов соответствует определённому узлу сети и ему назначается отдельный порт коммутации. Для того чтобы заполнить матрицу MAC-адресами, при первом включении устройство отправляет входящие на один из портов фреймы (или их ещё называют "кадры") с данными на все остальные существующие порты. После анализа всех фреймов коммутатор заполняет таблицу MAC-адресами хостов сети и локализует трафик.

Канальный уровень – уровень сетевой модели OSI, предназначенный для обмена данными между узлами, находящимся в том же сегменте локальной сети, путем передачи специальных блоков данных, которые называются кадрами (frame). В процессе формирования кадров данные снабжаются служебной информацией (заголовком), необходимой для корректной доставки получателю, и, в соответствии с правилами доступа к среде передачи, отправляются на физический уровень. Таким образом канальный уровень обеспечивает создание, передачу и прием кадров данных.

Этот уровень обслуживает запросы сетевого уровня и использует сервис физического уровня для приема и передачи пакетов.

Рассмотрев всё выше перечисленное были сформулированы следующие цели:

1. Разработать архитектуру коммутатора Ethernet L2 на языке Verilog;

2. Реализовать интерфейс GMII на 4 порта со скоростью передачи 1Гб/с;

3. Написать и соединить необходимые модули.

Ход работы

Прежде всего возникла необходимость выбрать языка описания аппаратуры. В настоящее время основными HDL-языками являются: VHDL и Verilog/SystemVerilog. Язык VHDL – язык со строгой типизацией, похожий на Ada или Pascal. Verilog и его «расширенная версия» SystemVerilog имеют синтаксис схожий с языком C. Для реализации коммутатора использовался второй вариант (Verilog/SystemVerilog), что обусловлено использованием языка в компании.

Для удобной разработки было выбрано следующее ПО:

1. Altera Quartus II 9.1SP2 – Среда разработки для микросхем фирмы Альтера. Эта программа САПР позволяет проектировать логику работы микросхем на языках VHDL и Verilog, позволяет производить симуляцию проектов и программировать микросхемы. Также ПО имеет встроенный инструмент classic timing analyzer, который позволяет без реализации дополнительных модулей отслеживать временные задержки сигналов.

2. ModelSim – среда для симуляции и отладки программ на HDL языках. Данный пакет программных средств в настоящее время является одной из наиболее распространенных систем HDL-моделирования, имеет простой визуальный пользовательский интерфейс и подробная справочная система, что сокращает время освоения пакета моделирования.

3. WireShark – программа-анализатор трафика для компьютерных сетей. Wireshark работает с подавляющим большинством известных протоколов, в том числе с Ethernet, позволяет пользователю просматривать весь проходящий по сети трафик в режиме реального времени, имеет графический пользовательский интерфейс и широкие возможности по сортировке и фильтрации информации.

4. VS Code – редактор исходного кода, поддерживающий в том числе языки описания аппаратуры, обеспечивающий подсветку синтаксиса, форматирование кода, всплывающие подсказки, поддержку git и удобную навигацию по коду.

Для совместной работы использовалась система контроля версий git. В качестве веб-сервиса использовался GitHub, где был создан приватный репозиторий (виден только участникам команды).

Работа над проектом велась в два этапа: подготовительный и собственно разработка коммутатора. Каждый из этапов включал изучение новых теоретических материалов и сопровождался выполнением практических заданий. Подготовительный этап предполагал знакомство с предметной областью и языком Verilog/SystemVerilog, приобретение навыков написания простых модулей на данных языках, знакомство с программным обеспечением, необходимым для разработки коммутатора. Задачи второго этапа сосредоточились вокруг разработки архитектуры коммутаторы и реализации её на Verilog, изучении соответствующих теоретических материалов для возможности реализации отдельных модулей.

Подготовительный этап

Первый этап работы заключался в закреплении теоретического материала по цифровой электронике и проектированию цифровых схем. В качестве методического пособия использовалась книга Дэвида М. Харриса и Сары Л. Харрис «Цифровая схемотехника и архитектура компьютера» – [1]. Основное внимание удалялось таким разделам как «Логические элементы», «Проектирование комбинационной логики», «Проектирование последовательностной логики» и «Языки описания аппаратуры».

В разделе «Логические элементы» были рассмотрены логические вентили, их графические изображения, способ описания зависимости выходного сигнала от входных.

В данных разделах были изучены триггеры (RS-триггер и MS-триггер), счетчики, конечные автоматы Мура и Мили.

Модуль приема кадра проще всего описать с помощью конечных автоматов, поэтому наиболее подробно были рассмотрены конечные автоматы – схемы с k-регистрами, которые могут находится в одном из 2k состояний (т.е. в конечном числе состояний). Конечный автомат состоит из двух блоков комбинационной логики: логики перехода в следующее состояние и выходной логики и регистра, в котором хранится текущее состояние. По фронту каждого тактового импульса автомат переходит в следующее состояние, которое определяется текущим состоянием и значениями на входах. Принято выделять два основных класса конечных автоматов: Мура, где входные значения зависят лишь от текущего состояния, и Мили, где выход зависит как от текущего состояния, так и от входных данных. Важно отметить, что автоматы Мили имеют меньшее количество состояний по сравнению с автоматом Мура, решающего ту же задачу, поскольку автомат Мили реагирует на вход, а не ждет изменения состояния, как автомат Мура. Следовательно, выходы автомата Мили будут опережать выходы автоматы Мура.

Важный этап – изучение основ языка описания аппаратуры Verilog: написание модулей (цифровых блоков аппаратуры, имеющих входы и выходы), использование битовых операторов, их приоритет, условные присваивания, блокирующие и неблокирующие присваивания, типы данных, операторы case и if, конструкции always.

Как правило при разработке программисты часто сталкиваются с различными багами и ошибками. И очень часто успешная компиляция схемы не дает гарантий, что она работает как надо. Следовательно, возникает необходимость быстро находить и исправлять ошибки. Есть два способа это сделать: локализация ошибки и редактирование кода, что не является самым оптимальным и быстрым способом, и написание тестов (наиболее быстрый и удобный способ). Testbench – это модуль для тестирования на языке Verilog, не имеющий входов и выходов, не синтезируемый в Quartus.

В testbench определяются входные воздействия на тестируемый модуль и их изменения в процессе работы и содержится ряд инструкций (например, отладочный вывод или вывод значений переменных вдоль конкретной трассы выполнения схемы), которые содержат информацию, полезную для отладки и симуляции. Выводить информацию можно как в консоль при работе средства симуляции. Основная цель написания таких модулей тестирования – выявление ошибок в работе схемы и их исправления, из этого можно сделать вывод, что задаваемые входные воздействия должны покрывать как можно большую часть комбинаций возможных входных значений.

Разработка коммутатора

2.1 Формат пакета Ethernet 802.3:

Практически каждой сетевой технологии (вне зависимости от её уровня) соответствует единица передачи данных. Такой единицей данных, передаваемых в сети Ethernet, является кадр.

Стандарт 802.3 определяет семь полей заголовка:

1. Поле преамбулы, состоящее из семи синхронизирующих байтов (каждый байт содержит одну и ту же последовательность битов – ‘b10101010). Преамбула используется для того, чтобы дать время и возможность схемам приемопередатчиков прийти в устойчивый синхронизм с принимаемым тактовыми сигналами;

2. Начальный ограничитель кадра (Start Frame Delimiter – SFD) состоит из одного байта с набором битов ‘b10101011. Данное поле указывает на предстоящий прием кадра.

3. Адрес назначения (Destination Address field) – состоит из 6 байт и содержит физический адрес устройства в сети, которому адресован данный кадр. Значение этого поля может быть уникальным или нет (широковещательный – предназначен для всех устройств сети).

4. Адрес источник (Source address field) – состоит из 6 байт и содержит физический адрес устройства в сети, которое отправило данный кадр. Первый бит адреса отправителя всегда равен нулю.

5. Поле длины/типа протокола следующего уровня (Length/Type field) может содержать соответственно длину или тип кадра в зависимости от используемого формата кадра. В нашем случае данное поле захваченных пакетов (в программе Wireshark) указывало на тип протокола верхнего уровня, которому принадлежит данный кадр. Состоит из двух байтов.

6. Поле данных (Data field) – содержит от 48 до 1500 байт. Если длина поля меньше 48 байт, то используется поле заполнения, которое и обеспечивает определенную минимальную длину поля данных (48 байт). Это обеспечивает корректную работу механизма обнаружения коллизий. Если длина поля данных достаточна, то поле заполнения в кадре не появляется.

7. Поле контрольной суммы (FCS field) – 4 байта, содержащие значение, которое вычисляется по определенному алгоритму (алгоритм циклического избыточного кода с использованием полинома CRC32 ('h04C11DB7)), подсчет начинается с поля Destination Address и заканчивается последним байтом поля данных. Данное поле предназначено для проверки корректности передачи данных, оно формируется на устройстве-отправителе пакета, а станция-получатель при приеме пакета выполняет собственно вычисление контрольной суммы для этого кадра по известному алгоритму, однако вычисление теперь заканчивается после прохождения последнего байта поля контрольной суммы. Таким образом при получении фиксированного заранее известного остатка (C704DD7B) можно сделать вывод о том, что пакет передан без ошибок.

2.2 Понятие контрольной суммы, виды, алгоритмы. Cyclic redundancy check (crc). CRC-32-IEEE 802.3 (0x04C11DB7)

Контрольная сумма – некоторое значение, рассчитанное по набору данных путём применения определённого алгоритма и используемое для проверки целостности данных при их передаче или хранении. Несмотря на своё название, контрольная сумма не обязательно вычисляется путём суммирования.

Популярность использования контрольных сумм для проверки целостности данных обусловлена тем, что подобная проверка просто реализуема в двоичном цифровом оборудовании, легко анализируется и хорошо подходит для обнаружения общих ошибок, вызванных наличием шума в каналах передачи данных.

Среди простых можно выделить проверку общей чётности (бит четности) и код Хэмминга, среди наиболее распространенными алгоритмами в данное время являются CRC (циклический избыточный код), MD5 (используется на только для проверки целостности данных, но и позволяет получить довольно надежный идентификатор файла) и SHA-1 (алгоритм криптографического хеширования).

Для подсчета контрольной суммы поля FSM кадра Ethernet используется алгоритм CRC32. Данный алгоритм базируется на свойствах деления с остатком двоичных многочленов. Существует несколько вариантов реализации данного алгоритма:

1. Классический (побитовый алгоритм) реализуется с помощью последовательного итерационного сдвига данных в регистре с обратной связью на один бит. Недостатком является низкая скорость работы;

2. Табличный алгоритм, которые при расчете контрольной суммы использует таблицу с предвычисленными значениями на основе образующего полинома. При использовании данного метода используется большой объем памяти, поскольку приходится хранить предвычисленные данные;

3. Матричный алгоритм работает также, как и табличный, за исключением того, что вместо таблицы используется операция умножения выдвинутого вектора на матрицу по модулю 2.

В работе решено было использовать классический алгоритм с выдвижением сразу одного байта. Таким образом вычисление происходит по приходу нового байта данных: пришел байт – пересчитали контрольную сумму. Важно отметить, что алгоритм имеет некоторые входные параметры, которые влияют на результат работы алгоритма, например, значение используемого полинома, начальная инициализация CRC, инверсия конечного результата и инверсия порядка бит в байте и прочее.

Для подсчета контрольной суммы в протоколе Ethernet необходимо начальное значение для регистра, хранящего текущую контрольную сумму как 0xFFFFFFFF. Принятые байты необходимо передавать развернутым, ведь старший бит – на самом деле младший в байте и наоборот. Вычисленная контрольная сумма разворачивается и инвертируется.

2.3 Однопортовая\двухпортовая память

Стандартное однопортовое ОЗУ имеет по одной шине адреса, данных и управления и в каждый момент времени обеспечивает доступ к ячейке памяти только одному устройству. В отличие от стандартного в n-портовом ОЗУ имеется n независимых наборов шин адреса, данных и управления, гарантирующий одновременный и независимый доступ к ОЗУ n устройствам.

В двухпортовой памяти имеются два набора адресных, информационных и управляющих сигнальных шин, каждый из которых обеспечивает доступ к общему массиву запоминающих элементов.

Другими словами, одновременное выполнение операций чтения и записи в однопортовая памяти невозможно. А к двухпортовой могут сразу обращаться два устройства, так как она обладает способностью одновременного выполнения операций чтения и записи данных.

Так как двухпортовая память обеспечивает гораздо лучшее быстродействие, то было решено реализовывать этот вид запоминающих устройств.

Память для MAC-адресов

Память для MAC-адресов является важнейшей составляющей частью коммутатора, так как в ней хранятся данные о MAC-адресах и номер порта, откуда они приходили. И на основании этих данных происходит передача данных с одного порта на другой.

Наиболее популярный способ структурирования MAC-адресов у производителей коммутаторов – хеш-таблица. Смысл в том, что при вычислении хеш-функции от MAC-адреса на выходе имеем сразу адрес в памяти (индекс), обратившись по которому вычитываем номер порта.

Хеш-функция (на английском hash – «превращать в мешанину, в фарш») или функция свёртки – функция, осуществляющая преобразование массива входных данных произвольной длины в (выходную) битовую строку установленной длины, выполняемое определённым алгоритмом.

Наиболее простым примером является «обрамление» данных циклическим избыточным кодом (CRC, cyclic redundancy code), алгоритм, который используется для подсчёта контрольной суммы.

На практике существует проблема коллизий (случай, при котором хеш-функция преобразует более чем один массив входных данных в одинаковые сводки) но при правильно подобранной хеш-функции она минимизируется.

На этапе работы стоял выбор между использованием хеш-функцию, которая будет преобразовывать MAC-адрес в определённое число битов и использование некоторое число последних битов MAC-адреса. Выбор был сделан был в пользу второго варианта, так как он проще. К тому же коллизии были бы возможно при обоих случаях.

Следующий этап – выбор количества битов MAC-адреса для адресации таблицы. Для этого были изучены документации таких популярных моделей коммутаторов, как ZyXEL GS-3012F, D-Link DGS-3426, Metrotek X10-24. В модели от D-Link поддерживается 8192 адресов, а в остальных моделях – 16368 адресов. Эти числа являются степенями двойки, что очень удобно. Поэтому было принято решение работать с последними 14 битами MAC адреса, получим адресное пространство на 214 = 16368 адресов –[2].

В итоге была написана MAC-таблица на 16368 адреса, которая хранит номер порта и время записи. Работа данного модуля будет описана ниже.

Описание модулей

1) Receiver- Модуль приёма кадра;

На вход этого модуля поступают данные по интерфейсу GMII поступают:

- i_clk – тактовый сигнал;

- i_data - 8 бит данных (из кадра, захваченного WireShark);

- i_dv – валидность данных (разрешение на запись);

- i_er – сигнализирует об ошибке.

Модуль приёма представляет собой конечный автомат, в котором 7 состояний. Он отслеживает текущее поле кадра. В данном модуле данные задерживаются на 4 такта.

Первое состояние – NO_DATA, остальные – поля кадра Ethernet стандарта IEEE 802.3.

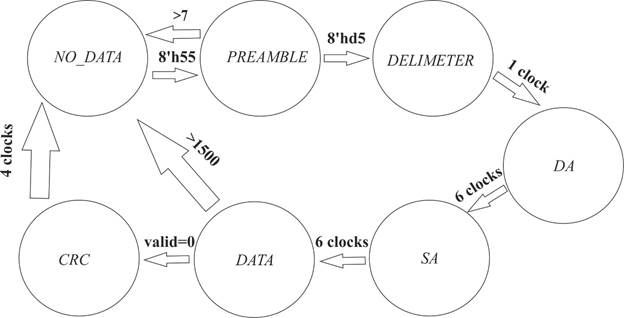

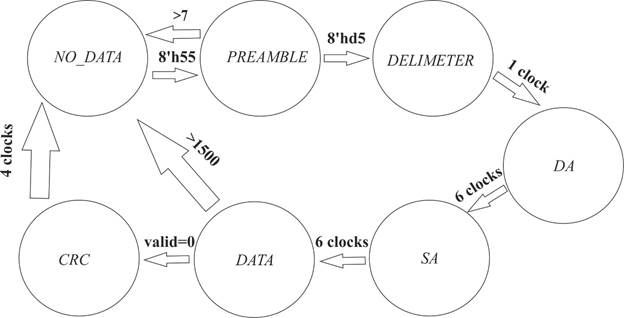

Рисунок 2.7 – Граф автомата приёмника

Состояние NO_DATA – автомат выходит из него в Preamble, когда приходит первый байт преамбулы - 8’h55.

Preamble – преамбула. Если она длиннее чем 7 байт, то автомат возвращается в состояние NO_DATA. Когда приходит байт - 8’hD5 – автомат переключается в состояние Delimeter.

Delimiter – через 1 байт переходит в состояние SA.

DA – адрес назначения - через 6 байт переходит в состояние DA.

SA - адрес источника - через 6 байт переходит в состояние DATA.

DATA – поле данных кадра. Если поле данных длиннее чем 1500 байтов, то это ошибка и автомат переключается в состояние NO_DATA.

CRC – поле контрольной суммы. Также тут происходит проверка контрольной суммы. Для этого была использована готовую функцию для подсчёта CRC, предоставленную компанией “МИКРАН”. Проверка проходила по следующему алгоритму: параллельно с приёмом пакета, начиная с поля DA до CRC данные обрабатываются функцией; если после этого получился остаток 32’hC704DD7B, то контрольная сумма подсчитана верно. В противном случае –

это ошибка.

У этого модуля 7 выходов:

- o_rx_dv_4cd, o_rx_d4cd, o_rx_er_4cd - поступают те же входные данные (i_dv, i_data, i_er), но задержанные на 4 такта;

- o_fsm_state – состояние автомата;

- o_fsm_state_changed – сигнал о смене состояния автомата;

- osa – адрес источника, для записи в таблицу маршрутизации;

- osa_new – сигнал о том, что приходит новый пакет.

Чтение SA происходит сразу с приёмника кадра.

2) Модуль RAM - Копирование пакета в память;

Модуль соединён с выходами приёмника. На него поступают:

- i_rx_data - данные;

- i_dv;

- i_er;

- i_fsm_state – состояние приёмника;

Модуль тоже представляет собой конечный автомат, его работу можно представить графом на рисунке 2.8.

Рисунок 2.8 – Граф конечного автомата модуля записи в память

В память записываются данные, соответствующие всем состояниям, кроме NO_DATA, Preamble, Delimeter. Делиметр выступает сигналом для записи. Запись прекращается, когда сигнал i_dv переходит в состояние логического нуля. Если i_er = 1 (неправильная контрольная сумма), то кадр удаляется.

Память выполнена в виде кольцевого буффера - т.е когда она заполнилась, указатель записи идёт в самое начало.

Кроме записи в память RAM модуль выполняет следующую функцию:

Когда - DA, модуль ищет этот адрес в таблице маршрутизации. Если он находит его, то модуль считывает номер порта из таблицы.

3) FIFO буфер:

После того, как кадр записался в память, информация о его длине и указатель на начало кадра передаётся в одно из 3 FIFO. Их 3, так как, к примеру, данные с 0 порта могут быть переданы на 1,2,3 порт.

4) Таблица для MAC-адресов:

Данная таблица имеет 214 адресов. В ячейки кладутся номер порта и время, которое хранится этот номер. Через 5 минут после записи ячейка очищается. Адресация проводится по последним 14 битам MAC адреса.

В этом модуле 3 входа:

- i_port_num – номер порта;

- i_SA – через этот вход с приёмника поступают SA, а затем регистрируется и записывается номер порта;

- i_DA – адрес получателя, который приходит с предыдущего модуля RAM. Как только приходит DA, этот MAC адрес ищется в таблице и на выход подаётся номер порта.

5) MAC арбитр:

Данный модуль обеспечивает поочерёдный доступ приёмников к таблице MAC-адресов путём поочерёдного опроса на наличие новых пакетов.

6) Transmitter - Модуль формирования кадра.

Этот модуль представляет собой конечный автомат, в котором 8 состояний. Первое состояние указывает на паузу, когда формирование нового кадра не происходит. Остальные 6 состояний соответствуют формированию соответствующих полей кадра Ethernet IEEE 802.3.

Заключение

По итогам прохождения практики достигнуты следующие результаты:

1. Изучены части стандарта протокола Ethernet и структура его кадра. Были изучены основы языка Verilog.

2. Разработана архитектура коммутатора с 4 портами на основе коммутационной матрицы с арбитражем (на виртуальных очередях).

3. На языке Verilog написано 50% модулей из разработанной архитектуры, а именно: блок приема кадра, включающий в себя модель приема кадра, модуль двухпортовой памяти и модуль очередей, блок адресации, включающий в себя модуль таблицы MAC-адресов и логику записи в таблицу, частично разработан модуль передатчика пакета.

4. Начат процесс соединения модулей коммутатора, имеется рабочая входная часть коммутатора.

РАЗРАБОТКА КОММУТАТОРА ETHERNER 802.3 НА ЯЗЫКЕ ОПИСАНИЯ АППАРАТУРЫ VERILOG HDL

ОТЧЕТ

ПО РЕЗУЛЬТАТАМ

Производственной практики: практика по получению профессиональных умений и опыта профессиональной деятельности.

|

| Обучающийся гр. 1B7

_______________ Ковыляев А.Д.

(подпись)

_______________

(дата)

|

|

________

оценка

М.П.

| Руководитель практики от профильной организации:

Начальник отдела мультиплексорного оборудования департамента телекоммуникаций

_______________ Филатов Д.С.

(подпись)

_______________

(дата)

|

|

_________

оценка

| Руководитель практики от Университета:

Доцент, к.т.н.

_______________ Громов В.А.

(подпись)

_______________

(дата)

|

Томск 2019

Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное

учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР)

Кафедра радиотехнических систем

|

| УТВЕРЖДАЮ

Зав.кафедрой РТС

Мелихов С.В.

__________________

(подпись)

|

ЗАДАНИЕ

на производственную практику: практика по получению профессиональных умений и опыта профессиональной деятельности.

студенту гр. 1B7 радиотехнического факультета

Ковыляеву Алексею Дмитриевичу

1. Тема практики: разработка коммутатора ETHERNER 802.3 на языке описания аппаратуры VERILOG HDL;

2. Цель практики:

- Знакомство с предприятием «МИКРАН»;

- Знакомство с сетевыми технологиями передачи данных;

- Получить практические навыки в ходе работы над проектом;

3. Задачи практики:

- Ознакомиться с должностными инструкциями и обеспечением безопасности жизнедеятельности на предприятии;

- Изучение языка описания оборудование VERILOG HDL;

- Создание прототипа модульной схемы коммутатора по технологии

Ethernet 802.3;

- Написать отчёт по практике.

4. Исходные данные для практики:

4.1Методические указания по производственной практике для студентов - Томск 2018;

4.2https://edu.tusur.ru/publications/6159;

4.3ОС ТУСУР 01-2013.

5. Технические требования к отчету по практике: структура отчета должна соответствовать Положению о практиках, оформление отчета должно соответствовать требованиям ОС ТУСУР 01-2013, объем отчета не менее 30 страниц А4.

Дата выдачи: «24» июня 2019 г.

Руководитель практики от университета

| Доцент, к.т.н.

| ___________________

(Подпись)

| Громов В.А.

|

Согласовано:

Руководитель практики от профильной организации

| Начальник отдела мультиплексорного оборудования департамента телекоммуникаций

|

___________________

(Подпись)

|

Филатов Д.С.

|

Задание принял к исполнению «24» июня 2019 г.

| Студент гр.1B7

| ___________________

(Подпись)

| Ковыляев А.Д.

|

Реферат

Отчет по производственной практике, 33 с., 9 рис., 7 источников.

ЦИФРОВОЕ ТЕЛЕВЕЩАНИЕ, DVB-T/T2, ОДНОЧАСТОТНАЯ СЕТЬ, СДК, CONTROLCAST.

Цель производственной практики – реализация коммутатора Ethernet 802.3 на ПЛИС на языке описания аппаратуры Verilog HDL.

В процессе разработки применялись программы WireShark, modelsim, Quartus

Cодержание

Реферат. 3

Введение. 4

1 Ход работы.. 6

1.1 Подготовительный этап. 7

1.2 Захват пакетов в программе WireShark. Исследование на соответствие формату кадров IEEE 802.3(3.1.1) 9

2 Разработка коммутатора. 12

2.1 Формат пакета Ethernet 802.3: 12

2.2 Понятие контрольной суммы, виды, алгоритмы. Cyclic redundancy check (crc). CRC-32-IEEE 802.3 (0x04C11DB7) 13

2.3 Однопортовая\двухпортовая память. 15

2.4 FIFO и LIFO, кольцевой буфер. 15

2.5 Память для MAC-адресов. 16

2.6 Разработка архитектуры коммутатора. 18

2.7 Выделение функциональных модулей и их описание. 22

2.8 Взаимодействия модулей между собой. 24

2.9 Описание модулей. 25

Заключение. 30

Список использованных источников. 31

Введение

В данное время существует тенденция стремительного роста сетевого трафика, который становится непосильной нагрузкой на сетевое оборудование. Для решения этой проблемы производители повышают быстродействие, надежность и качество работы своего сетевого оборудования, за счет расширения функциональных возможностей. В частности, повышение работы коммутирующего оборудования достигалось за счет возможностей следующих уровней модели OSI. Так, коммутаторы сетевого уровня способны существенно изменить характер работы сети, являясь универсальным средством решения многих проблем вычислительных сетей.

Коммутатор – это устройство, обеспечивающее соединение узлов компьютерной сети для организации единой системы доступа пользователей к программным, техническим и информационным ресурсам. Узлом сети считается любое устройство с IP-адресом способное совершать обмен данными.

Основой для разработки коммутаторов послужила технология сетевого моста, которая подразумевает последовательную передачу пакетов информации. Коммутаторы, как устройства следующего поколения, обеспечивают одновременную передачу пакетов данных для всех своих портов.

Принцип работы коммутатора основывается на заполнении логической матрицы MAC-адресами в контентно-адресуемой памяти устройства. Каждый из адресов соответствует определённому узлу сети и ему назначается отдельный порт коммутации. Для того чтобы заполнить матрицу MAC-адресами, при первом включении устройство отправляет входящие на один из портов фреймы (или их ещё называют "кадры") с данными на все остальные существующие порты. После анализа всех фреймов коммутатор заполняет таблицу MAC-адресами хостов сети и локализует трафик.

Канальный уровень – уровень сетевой модели OSI, предназначенный для обмена данными между узлами, находящимся в том же сегменте локальной сети, путем передачи специальных блоков данных, которые называются кадрами (frame). В процессе формирования кадров данные снабжаются служебной информацией (заголовком), необходимой для корректной доставки получателю, и, в соответствии с правилами доступа к среде передачи, отправляются на физический уровень. Таким образом канальный уровень обеспечивает создание, передачу и прием кадров данных.

Этот уровень обслуживает запросы сетевого уровня и использует сервис физического уровня для приема и передачи пакетов.

Рассмотрев всё выше перечисленное были сформулированы следующие цели:

1. Разработать архитектуру коммутатора Ethernet L2 на языке Verilog;

2. Реализовать интерфейс GMII на 4 порта со скоростью передачи 1Гб/с;

3. Написать и соединить необходимые модули.

Ход работы

Прежде всего возникла необходимость выбрать языка описания аппаратуры. В настоящее время основными HDL-языками являются: VHDL и Verilog/SystemVerilog. Язык VHDL – язык со строгой типизацией, похожий на Ada или Pascal. Verilog и его «расширенная версия» SystemVerilog имеют синтаксис схожий с языком C. Для реализации коммутатора использовался второй вариант (Verilog/SystemVerilog), что обусловлено использованием языка в компании.

Для удобной разработки было выбрано следующее ПО:

1. Altera Quartus II 9.1SP2 – Среда разработки для микросхем фирмы Альтера. Эта программа САПР позволяет проектировать логику работы микросхем на языках VHDL и Verilog, позволяет производить симуляцию проектов и программировать микросхемы. Также ПО имеет встроенный инструмент classic timing analyzer, который позволяет без реализации дополнительных модулей отслеживать временные задержки сигналов.

2. ModelSim – среда для симуляции и отладки программ на HDL языках. Данный пакет программных средств в настоящее время является одной из наиболее распространенных систем HDL-моделирования, имеет простой визуальный пользовательский интерфейс и подробная справочная система, что сокращает время освоения пакета моделирования.

3. WireShark – программа-анализатор трафика для компьютерных сетей. Wireshark работает с подавляющим большинством известных протоколов, в том числе с Ethernet, позволяет пользователю просматривать весь проходящий по сети трафик в режиме реального времени, имеет графический пользовательский интерфейс и широкие возможности по сортировке и фильтрации информации.

4. VS Code – редактор исходного кода, поддерживающий в том числе языки описания аппаратуры, обеспечивающий подсветку синтаксиса, форматирование кода, всплывающие подсказки, поддержку git и удобную навигацию по коду.

Для совместной работы использовалась система контроля версий git. В качестве веб-сервиса использовался GitHub, где был создан приватный репозиторий (виден только участникам команды).

Работа над проектом велась в два этапа: подготовительный и собственно разработка коммутатора. Каждый из этапов включал и