История создания датчика движения: Первый прибор для обнаружения движения был изобретен немецким физиком Генрихом Герцем...

Состав сооружений: решетки и песколовки: Решетки – это первое устройство в схеме очистных сооружений. Они представляют...

История создания датчика движения: Первый прибор для обнаружения движения был изобретен немецким физиком Генрихом Герцем...

Состав сооружений: решетки и песколовки: Решетки – это первое устройство в схеме очистных сооружений. Они представляют...

Топ:

История развития методов оптимизации: теорема Куна-Таккера, метод Лагранжа, роль выпуклости в оптимизации...

Проблема типологии научных революций: Глобальные научные революции и типы научной рациональности...

Техника безопасности при работе на пароконвектомате: К обслуживанию пароконвектомата допускаются лица, прошедшие технический минимум по эксплуатации оборудования...

Интересное:

Влияние предпринимательской среды на эффективное функционирование предприятия: Предпринимательская среда – это совокупность внешних и внутренних факторов, оказывающих влияние на функционирование фирмы...

Отражение на счетах бухгалтерского учета процесса приобретения: Процесс заготовления представляет систему экономических событий, включающих приобретение организацией у поставщиков сырья...

Берегоукрепление оползневых склонов: На прибрежных склонах основной причиной развития оползневых процессов является подмыв водами рек естественных склонов...

Дисциплины:

|

из

5.00

|

Заказать работу |

|

|

|

|

В МП Pentium 4 реализована архитектура IA-32, общая для всех 32 разрядных микропроцессоров Intel. В процессе развития IA-32 производилось расширение возможности обработки данных представленных в различных форматах. Процессоры i386 выполняли обработку только целочисленных операндов. Для обработки чисел с плавающей запятой использовался внешний сопроцессор i387, подключаемый к МП. В состав процессоров i486 и последующих моделей Pentium введен специальный блок FPU, выполняющий операции над числами с плавающей точкой.

В процессорах Pentium MMX была впервые реализована групповая обработка нескольких целочисленных операндов разрядностью 1, 2, 4, 8 байт с помощью 1 команды. Это обеспечивалось введением дополнительного блока MMX (мультимедийное расширение). Название блока отражает его направленность на обработку видео и аудиоданных, когда одновременное выполнение одной операции над несколькими операндами позволяет существенно повысить скорость обработки изображений и звуковых сигналов.

Начиная с модели Pentium III, в процессоры был введен блок SSE для групповой обработки чисел с плавающей точкой. Расширен и набор регистров, используемый для промежуточного хранения данных. Кроме 32 разрядных регистров для хранения целочисленных операндов процессор содержал 80 разрядный регистр, который обслуживал блоки FPU и MMX.

При работе FPU регистры SU0 – SI7 образуют кольцевой стек, в котором хранятся числа с плавающей запятой, представленные в формате с расширенной точностью (80 разрядов). При реализации MMX операций они используются 64 разрядные регистры, где могут храниться несколько операндов: восемь – 8 разрядных, четыре – 16 разрядных, два – 32 разрядных или один – 64 разрядный. Блок SSE2 введенный в состав процессора значительно расширяет возможности обработки нескольких операндов по сравнению с блоком SSE из Pentium III. Блок SSE2 реализует 144 новые команды, обеспечивающие одновременное выполнение операций над несколькими операндами, которые располагаются в памяти. Операции SSE2 позволяют повысить эффективность процессора при реализации трехмерной графики, Интернет приложений, обеспечивая сжатие кодирование аудио и видеоданных. Введение этой группы команд является основной особенностью реализации Pentium 4. Базовый набор команд используемые способы адресации полностью совпадают с предыдущими моделями.

|

|

Микроархитектура МП P4 получила название Net Burst (пакетно-сетевая). Внутренняя структура реализуется путем разделения потоков команд и данных, поступающих из системной шины через блок внешнего интерфейса и размещенную на кристалле процессора, общую КЭШ-память L2 уровня, емкостью 256 Кб. Это позволило сократить время выборки команды данных по сравнению с Pentium III, где КЭШ-память располагалась на отдельном кристалле, смонтированном в общем корпусе с процессором.

Блок внешнего интерфейса реализует обмен процессора с системной памятью, контроллерами ввода-вывода и другими устройствами системы (рис 4). Системная шина имеет 64 разрядную двунаправленную шину данных и 41 разрядную шину адреса, обеспечивая адресацию до 64 гигабайт внешней памяти. Дешифратор команд работает вместе с памятью микропрограмм, формируя последовательность микрокоманд, поступивших из оперативной памяти.

Декодированные команды загружаются в КЭШ-память микрокоманд, где могут храниться до 12000 микрокоманд, после ее заполнения практически любая команда находится в декодированном виде. Поэтому при поступлении очередной команды блок трассировки выбирает из этой КЭШ-памяти микрокоманды на выполнение. Если попадается команда условного ветвления, то включается механизм предсказания ветвления, который формирует адрес следующей выбираемой команды до того, как будет определено условие перехода.

|

|

После формирования потоков микрокоманд производится выделение регистров, необходимых для их выполнения. Эта процедура реализуется блоком распределения регистров, который выделяет для каждого указанного в команде логического регистра один из 128 физических регистров, входящих в блок регистров замещения (БРЗ) – эта процедура позволяет выполнить команды, использующие одни и те же логические регистры одновременно или с изменением их последовательности.

Микрокоманды размещаются в очереди микрокоманд, в ней содержатся 126 декодированных команд, которые направляются затем в исполнительное устройство, например, в Pentium III в очереди находятся микрокоманды для только 40 поступивших команд. Увеличение числа команд, стоящих в очереди позволяет организовать поток их исполнения, с изменением последовательности выделяя при этом команды, которые могут выполняться параллельно. Это реализуется как распределение микрокоманд.

Суперскалярная архитектура реализуется путем организации исполнительного ядра в виде ряда параллельно работающих блоков. АЛУ – производят обработку целочисленных операндов, которые поступают из заданных регистров блока регистров замещения (БРЗ). В эти же регистры заносится и результат операций.

Рис.4 Структура микропроцессора Pentium 4

Исполнительное ядро работает с повышенной скоростью выполнения, например, микрокоманда сложения целочисленных операндов на частоте процессора 1,5 ГГц выполняется за 0,36 нСек.

Адреса операндов, выбираемых из памяти, вычисляются блоком формирования адреса (БФА), который реализует интерфейс с КЭШ-памятью данных L1 уровня емкостью 8 кбайт.

БФА может формировать 48 адресов для разгрузки операндов из памяти регистра БРЗ и 24 адреса для записи из регистра в память (в Pentium III формируются соответственно 16 и 12). При этом БФА формирует адреса операндов для команд, которые еще не поступили на выполнение. При обращении к памяти БФА одновременно выдает адреса двух операндов: 1 –для загрузки операндов в заданный регистр БРЗ, 2 – для пересылки результата из БРЗ в память. Таким образом, реализуется процедура предварительного чтения данных для последовательной их обработки в исполнительных блоках, которые называются спекулятивной выборкой. Аналогично организуется работа блоков SSE, FPU, MMX, которые имеют отдельный набор регистров и блок формирования адресов операндов.

|

|

При выборке операнда из памяти производится обращение КЭШ-памяти данных L1 уровня, который имеет отдельные порты для чтения и записи.

За 1 такт производится выборка операндов для 2 команд. Время обращения к КЭШ-памяти составляет 1,42 нCек. при тактовой частоте 1,5 ГГц, что в 2 раза меньше в аналогичном случае у Pentium III, но на частоте 1 ГГц. В Pentium 4 используется гиперконвейерная технология, при которой число ступеней конвейера достигает 20. Дополнительно используется усовершенствованный блок предсказания ветвлений, обеспечивающий 90% вероятность правильного предсказания.

|

|

|

Своеобразие русской архитектуры: Основной материал – дерево – быстрота постройки, но недолговечность и необходимость деления...

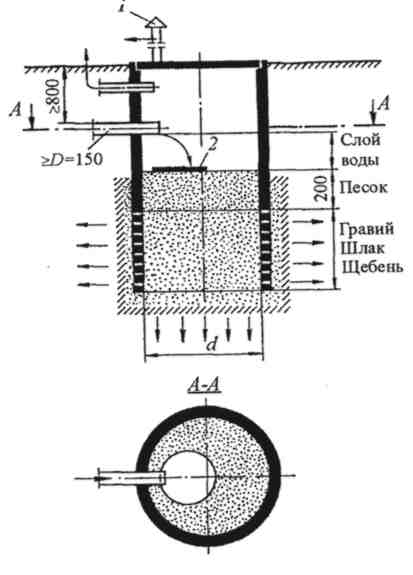

Индивидуальные очистные сооружения: К классу индивидуальных очистных сооружений относят сооружения, пропускная способность которых...

Папиллярные узоры пальцев рук - маркер спортивных способностей: дерматоглифические признаки формируются на 3-5 месяце беременности, не изменяются в течение жизни...

Семя – орган полового размножения и расселения растений: наружи у семян имеется плотный покров – кожура...

© cyberpedia.su 2017-2024 - Не является автором материалов. Исключительное право сохранено за автором текста.

Если вы не хотите, чтобы данный материал был у нас на сайте, перейдите по ссылке: Нарушение авторских прав. Мы поможем в написании вашей работы!