ISBN 978-985-488-895-8.

Практикум содержит краткие теоретические сведения, методические указания к выполнению лабораторных занятий.Пособие разработано для магистрантов специальности 1-59 81 01 «Управление безопасностью производственных процесов», а также будет полезно для магистрантов других специальностей. Практические задания предназначены для магистрантов и преподавателей, владеющих теоретическим материалом по темам предлагаемых лабораторных работ.

УДК 331.45(076.5)

ББК 65. 247я73

ISBN 978-985-48-8.© Силков Н.И., Черемисинов Д.И., Мельникова Е.М., 2014

© УО «Белорусский государственный

университет информатики и радиоэлектроники», 2014

СОДЕРЖАНИЕ

Введение………………………………………………………………………3

Тема 1. Исследование синхронных и асинхронных триггеров............…...4

Тема 2. Исследование двоичных счетчиков с К=2n и К≠2n.......……….. 13

Тема 3. Исследование дешифраторов, мультиплексоров,

демультиплексоров, двоичных компараторов.............................................21

Тема 4. Исследование логических схем на основе мультиплексоров........28

Тема 5. Исследование двоичных полных и неполных сумматоров …......32

Тема 6. Исследование линейных схем на операционных

усилителях (ОУ)..............................................................................................40

Тема 7. Исследование активных фильтров......................................……....50

Тема 8. Исследование нелинейных преобразователей сигналов

на основе операционных усилителей...................…………………...……61

Введение

В промышленности используется достаточно большая номенклатура производственных процессов и технологического оборудования, отличающихся функциональной сложностью, способом использования изготовления, методами обеспечения безопасности труда и др. показателями. Процесс управления безопасностью производственных процессов не может быть выполнен без знаний инновационных технологий, современных компьютерных технологий, функционирования узлов и электронных блоков систем безопасности.

В пособии представлена тематика занятий, нацеленная на выполнение работы по изучению электронных схем, предназначенных для решения исследовательских и практических задач создания систем безопасности. Пособие поможет магистрантам в практическом освоении методики расчётов основных вариантов аналоговых и дискретных схем, алгоритмов, и элементной базы, обеспечивающих функционирование информационных систем безопасности, приобретения практических навыков использования операционных усилителей для выполнения математических операций, связанных с применением и разработкой систем безопасности. Разработка может быть использована для проверки уровня знаний при самостоятельной подготовке к занятиям. По дисциплине «Электронные системы безопасности» в пособии предусмотрено 8 тем для лабораторных занятий. К каждой лабораторной работе разработано несколько вариантов ее практической реализации.

RS-триггер

RS-триггер – ячейка хранения информации, триггер с установочным запуском - это логическое устройство с двумя устойчивыми состояниями, имеющее два информационных входа R и S, такие, что при S=1 и R=0 триггер принимает состояние 1 (Q=1), а при R=1, S=0 триггер принимает состояние 0 (Q=0).

Рисунок 1.1- RS-триггер на элементах И-НЕ и временные диаграммы его работы.

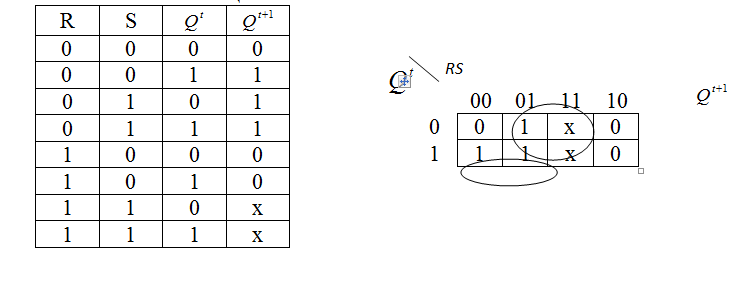

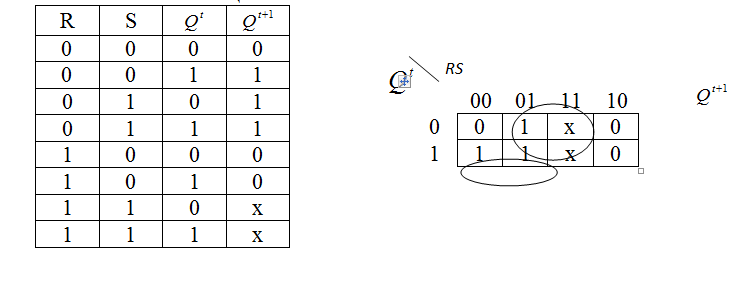

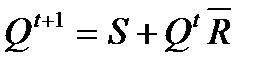

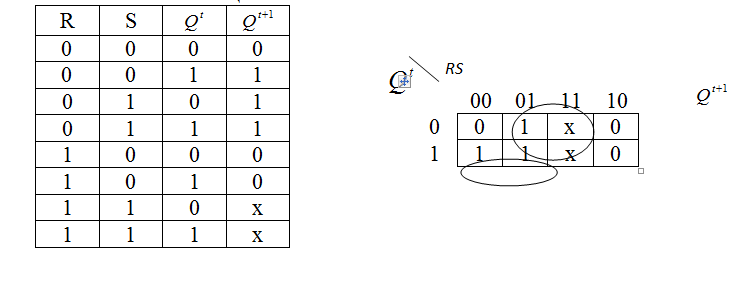

Полная таблица состояний RS-триггера представлена в табл.1.1. Методом карт Карно-Вейча выполним минимизацию переключательной функции для выхода  .

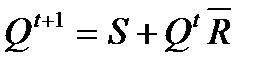

.

Таблица 1.1

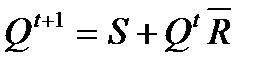

При доопределении неопределенных значений (х) переключательной функции единицами получим:

(1.1)

(1.1)

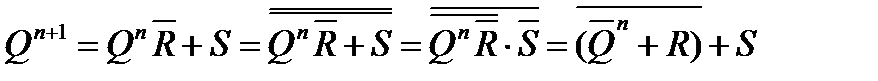

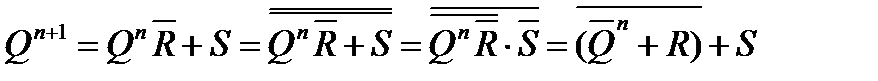

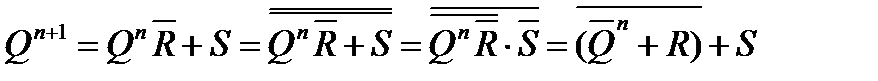

В базисах И-НЕ и ИЛИ-НЕ, функция выхода RS триггера имеет вид:

(1.2)

(1.2)

Рисунок 1.2 – RS -триггер на злементах ИЛИ-НЕ и его функциональное обозначение

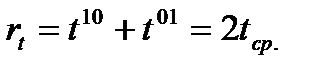

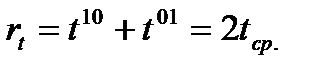

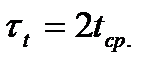

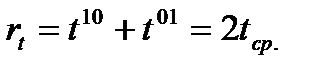

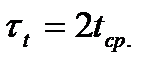

Задержка переключения асинхронных RS -триггеров составит сумму задержек переключения двух логических элементов, на которых выполнены триггеры, т.е.

(1.3)

(1.3)

Действительно для любой схемы при записи информации, например, по входу S (триггер находится в состоянии 0) новое устойчивое состояние триггера Q=1 сформируется через интервал времени  , отсчитываемый от момента поступления сигнала на вход S.

, отсчитываемый от момента поступления сигнала на вход S.

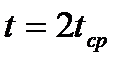

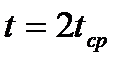

Для устойчивого функционирования триггера длительность сигнала действующего на его входах R и S, должна быть не меньше суммарной задержки переключения логических элементов обоих плеч триггера для полного установления новых значений выходных уровней. Для вышеприведенных схем длительность входного сигнала должна быть не меньше  , т.е.

, т.е.

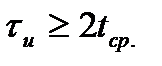

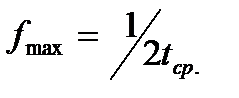

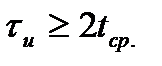

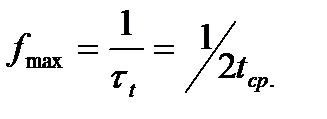

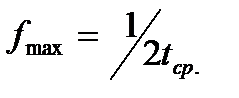

Максимальная частота переключения триггера  определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S.

определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S.

(1.4)

(1.4)

Следующая maxчастота чередования сигналов на входах определяется интервалом времени  , т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при

, т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при  длительность сигналов на выходах

длительность сигналов на выходах  и

и  не будет превышать

не будет превышать

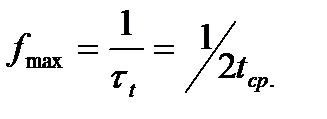

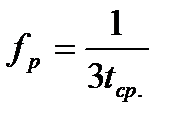

Поскольку сигналы длительностью  являются недостаточными для надежной передачи информации в логической цепи, то временной интервал между сигналами, действующими поочередно на входах триггера, приходится увеличивать, в результате чего

являются недостаточными для надежной передачи информации в логической цепи, то временной интервал между сигналами, действующими поочередно на входах триггера, приходится увеличивать, в результате чего  переключения триггера снижается. Предельная рабочая частота переключения

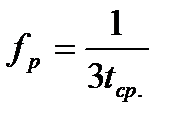

переключения триггера снижается. Предельная рабочая частота переключения  асинхронного RS -триггера при длительности информационного сигнала на каждом плече триггера не менее

асинхронного RS -триггера при длительности информационного сигнала на каждом плече триггера не менее  определяется из выражением

определяется из выражением

(1.5)

(1.5)

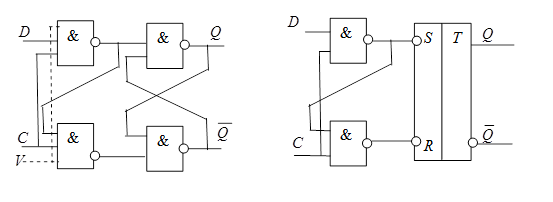

В качестве самостоятельных устройств асинхронные RS -триггеры находят ограниченное применение, но являются базовыми схемами всех более сложных триггерных устройств. В устройствах цифровой обработки информации в основном применяются синхронизируемые (тактируемые) триггеры.

В отличие от асинхронных, синхронные RS-триггеры имеют на входе каждого плеча дополнительные схемы совпадения, первые входы которых объединены и являются входом синхронизирующего импульса (СИ), а вторые входы схем совпадения являются информационными записи 1 (S) и 0 (R). Таким образом, информация, поступающая на входы R и S, может быть передана на собственно триггер только при поступлении СИ.

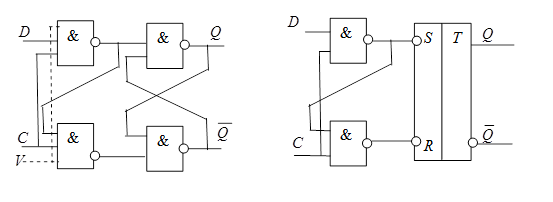

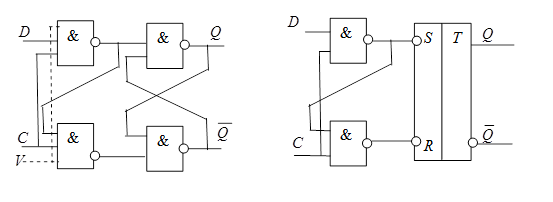

Рисунок 1.3 – Варианты схем синхронных RS-триггеров

Использование синхронизации определяет момент приема триггером входной информации и не допускает одновременного действия сигнала, переключающего триггер, и сигнала съема информации с триггера, обеспечивая, тем самым, правильную работу логических каскадов.

Поскольку в потенциальной системе элементов отсутствуют специальные элементы задержки сигналов, для выполнения условий надежной работы логических каскадов на каждый двоичный разряд, хранящий 1 бит информации, использовать 2 триггера, которые управляются двумя сдвинутыми во времени СИ. Таким образом удается информацию, снимаемую с выхода триггера, использовать для управления сигналами на его входах, что необходимо для построения более сложных схем.

Двойное Т в обозначении триггера означает, что он выполнен по двухступенчатой схеме.

Схема управляется либо от двух СИ, либо, как показано на рис. 1.4, от одного. В составе ИМС RS -триггеры маркируются буквами TP.

Рисунок 1.4– Двухступенчатый RS-триггер и его функциональное обозначение

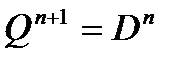

Триггер D-типа, DV-типа

Триггер D-типа, DV-типа – это логическое устройство с двумя устойчивыми состояниями и одним информационным входом D (от delay – задержка, замедление).

Простейшим видом такого триггера является асинхронный D-триггер.

Таблица 1.2

(1.6)

(1.6)

Уравнение 1.6 показывает, что состояние D -триггера в момент времени  совпадает с кодом входного сигнала в момент времени

совпадает с кодом входного сигнала в момент времени  , т.е. осуществляется задержка входного сигнала.

, т.е. осуществляется задержка входного сигнала.

Рисунок 1.5 – Функциональная схема D-триггера на элементах И-НЕ и инверторах

Схема на инверторах не имеет практического применения, так как функцию D -триггера выполняет схема, состоящая из двух последовательно включенных инверторов. Наибольший интерес представляют синхронные триггеры, нашедшие широкое распространение в ИС.

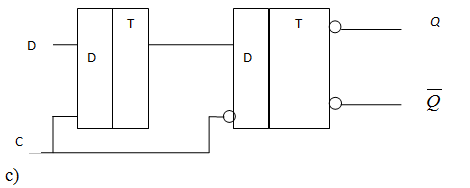

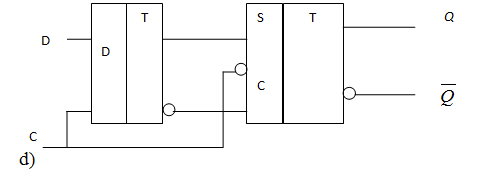

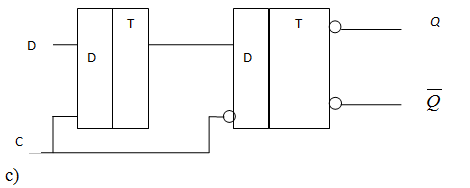

Рисунок 1.6 – D-триггер двухступенчатого типа

По формальной классификации D -триггеры маркируются буквами TM.

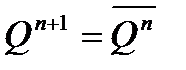

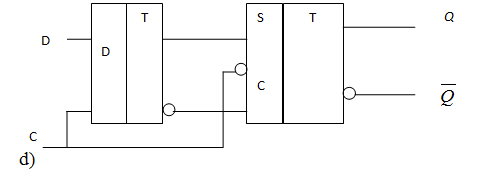

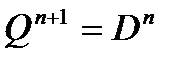

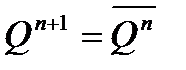

Триггеры Т-типа

Триггером Т -типа (счетный триггер) называют логическое устройство с двумя устойчивыми состояниями и одним входом Т, изменяющее свое состояние на противоположное всякий раз, когда на вход Т поступает управляющий сигнал. Триггер типа Т можно синтезировать как из отдельных логических элементов, так и используя триггер типа D (рисунок 1.8).

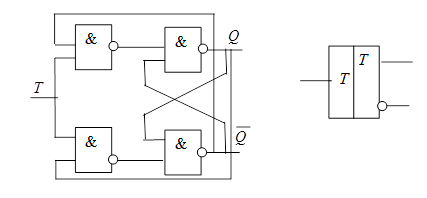

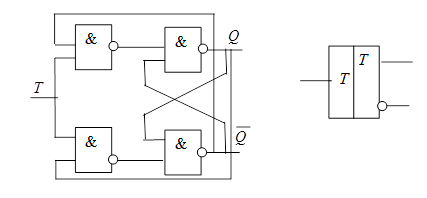

Рисунок 1.7 – Т -триггер на основе RS -триггера.

Рисунок 1.8 – Т -триггер на основе D -триггера и его обозначение.

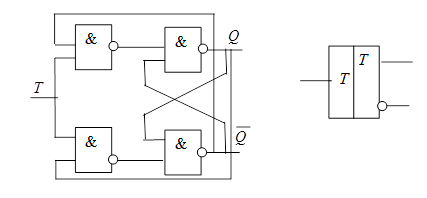

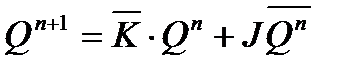

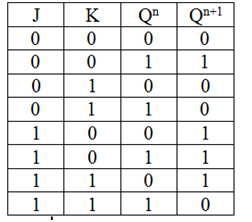

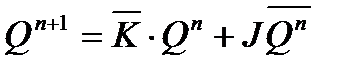

JK-триггер

Триггером JK -типа называется устройство с двумя устойчивыми состояниями и двумя входами J и K, которое при условии  осуществляет инверсию предыдущего состояния (т.е. при

осуществляет инверсию предыдущего состояния (т.е. при

), а в остальных случаях функционирует в соответствии с таблицей истинности RS -триггера, при этом вход J эквивалентен входу S, а вход К – входу R.

), а в остальных случаях функционирует в соответствии с таблицей истинности RS -триггера, при этом вход J эквивалентен входу S, а вход К – входу R.

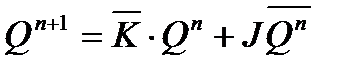

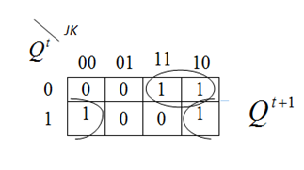

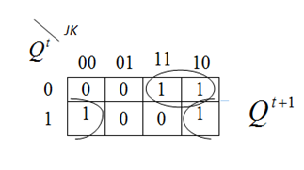

Логическое уравнение триггера, полученное на основе таблицы 1.3 имеет вид:

(1.7)

(1.7)

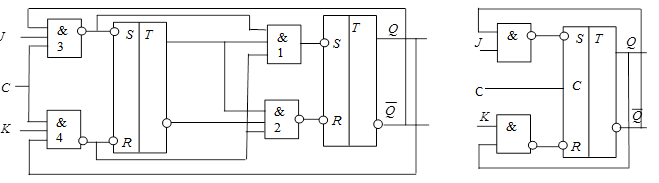

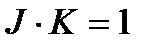

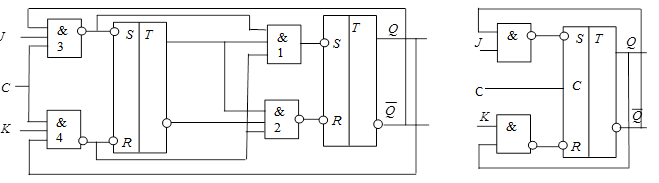

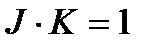

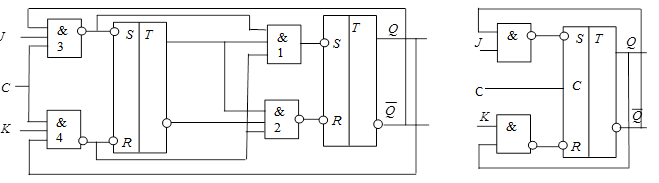

Рисунок 1.9 –JK-триггер, выполненный по варианту MS с запрещающими связями с элементов 3,4 на 1 и 2.

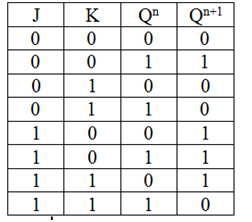

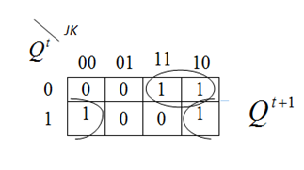

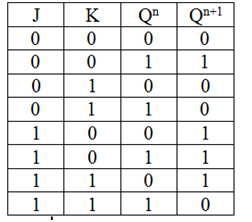

Таблица 1.3 – Полная таблица переключений JK-триггера и его карта Карно-

Вейча

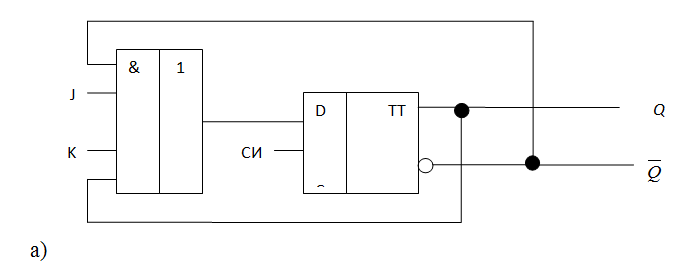

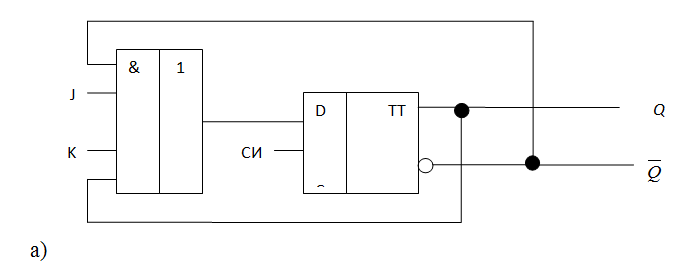

Рисунок 1.10 – JK- триггер системы ТТЛ

В серии ТТЛ JK-триггер имеет маркировку TB.

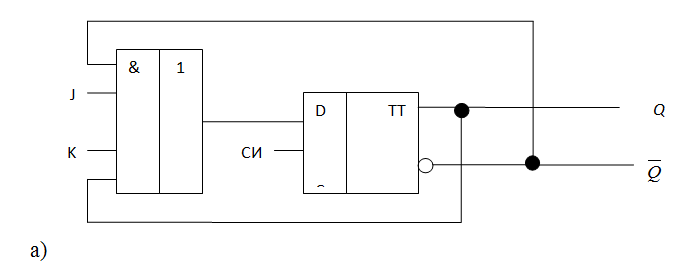

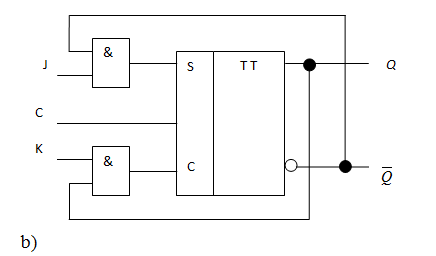

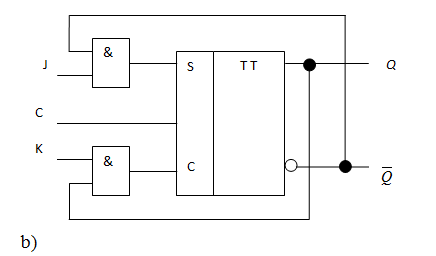

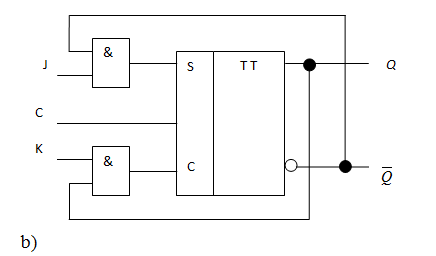

Рисунок 1.11 – Варианты построения триггерных схем на JK – триггере.

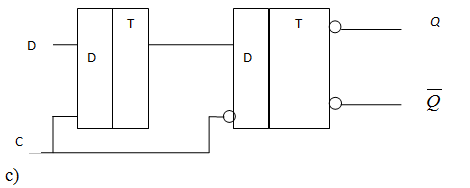

Схемные варианты триггеров

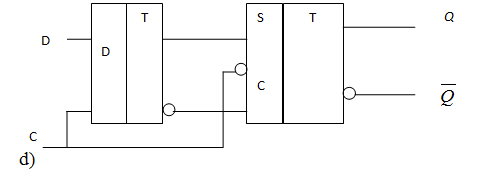

Рисунок 1.12 – Схемные варианты триггеров

Применение универсальных триггеров типа JK и DV, реализованных в одной микросхеме, в пересчетных схемах, регистрах сдвига и т.д. приводит к существенной экономии оборудования.

Естественно, что при построении системы элементов схема триггера может дополняться входной логикой, мощными выходными элементами и т.п. и применяться в нескольких модификациях. Выбор конкретной схемы во многом определяется уровнем разбиения на функциональные узлы.

Задание на самостоятельную работу

С использованием набора логических элементов выполнить схемы:

- выполнить логический анализ и записать переключательную функцию RS и JK триггеров,

-синхронного и асинхронного RS-триггера на элементной базе, указанной преподавателем,

- однотактного и двухтактного D-триггера,

- собрать один из вариантов схем триггеров рис.1.12 (по указанию преподавателя).

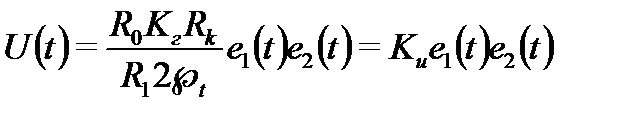

Перемножители напряжения.

Ряд типовых функциональных зависимостей может быть воспроизведен с помощью перемножителей напряжения. По способу выполнения математической операции перемножители подразделяются на два класса:

1. Перемножители прямого действия.

2. Перемножители косвенного действия.

В устройствах перемножения напряжений первого класса математическая операция выполняется на основе физических процессов, протекающих в электрических цепях; в перемножителях второго класса используются, как правило, различные математические соотношения, результатом которых является перемножение заданных напряжений. Рассмотрим особенности построения схем перемножителей напряжения прямого действия, наиболее часто применяемых в современных аналоговых ЭВМ.

Схемы на основе изменения крутизны характеристики управляемого элемента составляют основу полупроводниковых микроэлектронных устройств перемножения напряжений.

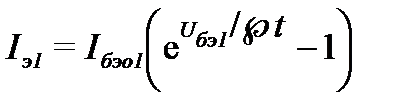

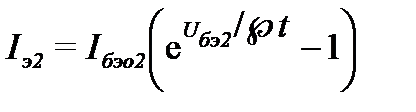

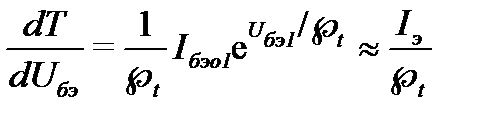

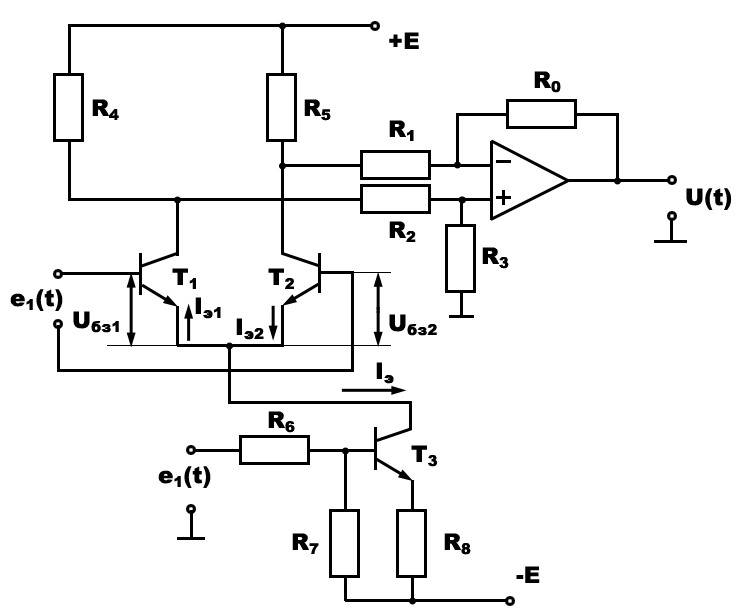

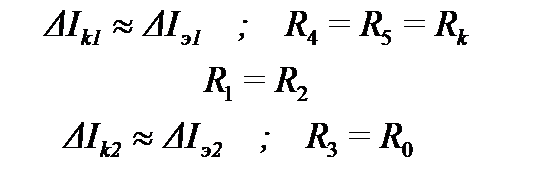

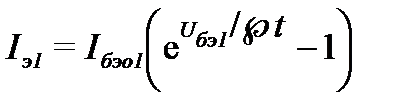

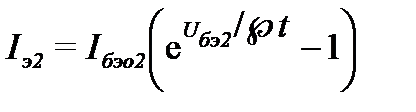

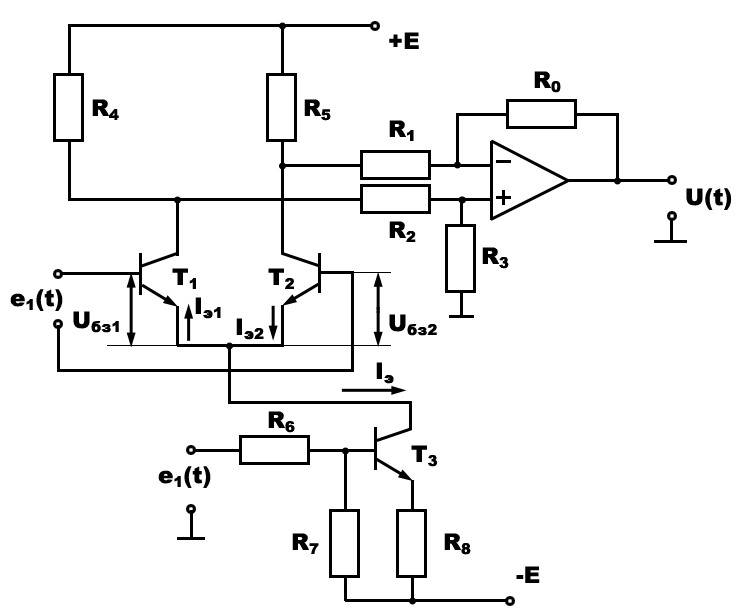

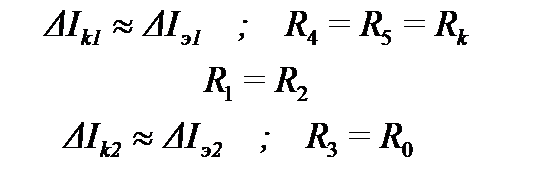

Рассмотрим простейшую схему (рис. 8.7), выполняющую операцию умножения. Эмиттерные токи транзисторов:

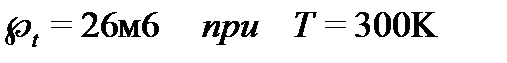

где  - начальный ток эмиттерного перехода;

- начальный ток эмиттерного перехода;

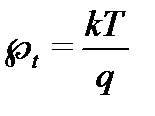

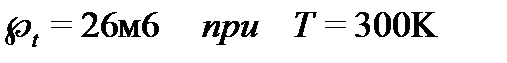

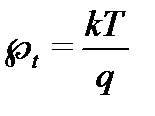

- температурный потенциал;

- температурный потенциал;

q – заряд электрона (й = 1.6 * 10-19 Кл);

k – постоянная Больцмана (k = 1.38 * 10-23 Дж/к);

T – абсолютная температура;

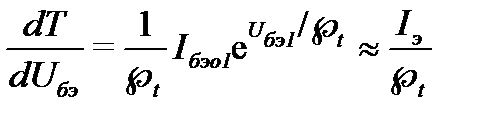

Если диапазон изменения UБЭ выбрать так, чтобы  , то крутизна эммитерного тока

, то крутизна эммитерного тока

При e1(t) = 0 и идеальном согласовании параметров транзисторов эмиттерные токи равны, т.е.

Рисунок 8.7 – Схема умножителя.

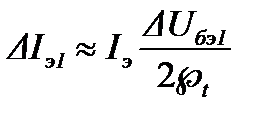

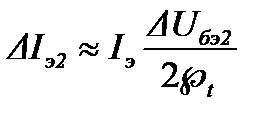

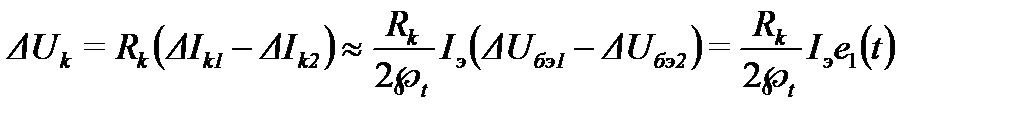

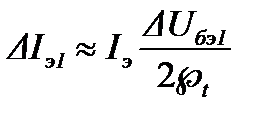

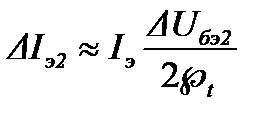

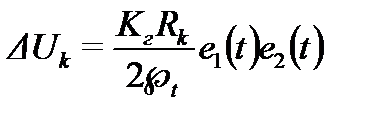

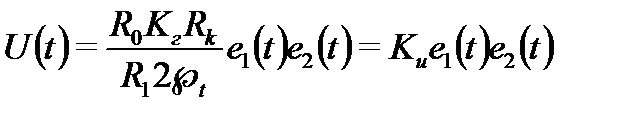

Перейдя от дифференциалов к конечным приращениям, получим

Выходным параметром дифференциального каскада является разность приращений коллекторных напряжений транзисторов. Полагаем, что

имеем

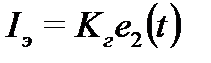

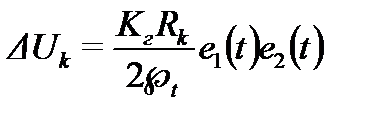

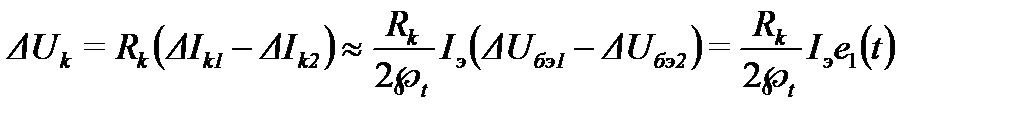

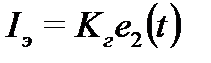

Эмиттерный ток Iэ задается генератором тока на транзисторе ТЗ и зависит от напряжения e2(t) (рис. 174). Поэтому

и, следовательно,

Это напряжение поступает на ОУ с коэффициентом передачи, равным R0/Ri, поэтому

где Ки - масштабный коэффициент.

Схема рассмотренного перемножителя отличается простотой, высоким быстродействием.

Задание на самостоятельную работу:

1. Назвать основные характеристики операционных усилителей.

2. Как изменяется выходное напряжение при подключении емкости в цепь обратной связи?

3. Как изменяется выходное напряжение при подключении емкости во входную цепь ОУ цепь?

4. Выполнить схему реализации функции ограничения.

5. Выполнить схему перемножителя.

ЛИТЕРАТУРА

1. Таненбаум, Э. Компьютерные сети / Э. Таненбаум. – 4-е изд. – СПб.: Питер, 2008.

2. Таненбаум, Э. Современные операционные системы / Э. Таненбаум. – 2-е изд. – СПб.: Питер, 2007.

3. Таненбаум, Э. Архитектура компьютера / Э. Таненбаум. – 5-е изд. – СПб.: Питер, 2007.

4. Хорстман, К. Г. Java 2. Основы. Т. 1–2 / К. Хорстман, С. Корнелл. – 7-е изд. – СПб.: Питер, 2007.

5. Бони, Дж. Руководство по Cisco IOS / Дж. Бони. – СПб.: Питер, 2008.

6. Олифер, В. Г. Компьютерные сети. Принципы, технологии, протоколы / В. Г. Олифер, Н. А. Олифер. – СПб.: Питер, 2001.

7. Цилькер, Б. Я. Организация ЭВМ и систем: учебник для вузов / Б. Я. Цилькер, С. А. Орлов. – СПб.: Питер, 2004.

8. Бройдо, В. Л. Вычислительные системы, сети и телекоммуникации / В. Л. Бройдо. – СПб.: Питер, 2003.

9. Курняван, Б. Создание Web-приложений на языке Java / Б. Курняван. –

М.:Лори, 2012.

ISBN 978-985-488-895-8.

Практикум содержит краткие теоретические сведения, методические указания к выполнению лабораторных занятий.Пособие разработано для магистрантов специальности 1-59 81 01 «Управление безопасностью производственных процесов», а также будет полезно для магистрантов других специальностей. Практические задания предназначены для магистрантов и преподавателей, владеющих теоретическим материалом по темам предлагаемых лабораторных работ.

УДК 331.45(076.5)

ББК 65. 247я73

ISBN 978-985-48-8.© Силков Н.И., Черемисинов Д.И., Мельникова Е.М., 2014

© УО «Белорусский государственный

университет информатики и радиоэлектроники», 2014

СОДЕРЖАНИЕ

Введение………………………………………………………………………3

Тема 1. Исследование синхронных и асинхронных триггеров............…...4

Тема 2. Исследование двоичных счетчиков с К=2n и К≠2n.......……….. 13

Тема 3. Исследование дешифраторов, мультиплексоров,

демультиплексоров, двоичных компараторов.............................................21

Тема 4. Исследование логических схем на основе мультиплексоров........28

Тема 5. Исследование двоичных полных и неполных сумматоров …......32

Тема 6. Исследование линейных схем на операционных

усилителях (ОУ)..............................................................................................40

Тема 7. Исследование активных фильтров......................................……....50

Тема 8. Исследование нелинейных преобразователей сигналов

на основе операционных усилителей...................…………………...……61

Введение

В промышленности используется достаточно большая номенклатура производственных процессов и технологического оборудования, отличающихся функциональной сложностью, способом использования изготовления, методами обеспечения безопасности труда и др. показателями. Процесс управления безопасностью производственных процессов не может быть выполнен без знаний инновационных технологий, современных компьютерных технологий, функционирования узлов и электронных блоков систем безопасности.

В пособии представлена тематика занятий, нацеленная на выполнение работы по изучению электронных схем, предназначенных для решения исследовательских и практических задач создания систем безопасности. Пособие поможет магистрантам в практическом освоении методики расчётов основных вариантов аналоговых и дискретных схем, алгоритмов, и элементной базы, обеспечивающих функционирование информационных систем безопасности, приобретения практических навыков использования операционных усилителей для выполнения математических операций, связанных с применением и разработкой систем безопасности. Разработка может быть использована для проверки уровня знаний при самостоятельной подготовке к занятиям. По дисциплине «Электронные системы безопасности» в пособии предусмотрено 8 тем для лабораторных занятий. К каждой лабораторной работе разработано несколько вариантов ее практической реализации.

Тема 1. Исследование синхронных и асинхронных триггерных схем

Цель работы: Приобретение и освоение знаний по практическому использованию триггерных схем.

Теория и примеры выполнения задания

В ЦВМ в процессе обработки информации необходимо ее промежуточное хранение. Для этого используют триггеры – элементы с двумя устойчивыми состояниями, имеющие соответствующие входы для сигналов управления. Основу триггеров – элементарных цифровых автоматов с двумя устойчивыми состояниями, составляет простейшие запоминающие ячейки, которые получают соединением двух потенциальных элементов И-НЕ (ИЛИ-НЕ). Независимо от того, какую функцию выполняет логический элемент И-НЕ или ИЛИ-НЕ, ячейки могут находится в двух устойчивых состояниях 1 и 0. Состоянию 1 соответствует единичный сигнал на выходе Q, состоянию 0 – нулевой сигнал на выходе Q, единичный сигнал на выходе  . Таким образом информация может одновременно сниматься с запоминающей ячейки (триггера) в прямом и инверсном виде.

. Таким образом информация может одновременно сниматься с запоминающей ячейки (триггера) в прямом и инверсном виде.

1. По способу записи информации триггеры разделяются на:

- асинхронные, запись информации в которых осуществляется непосредственно с поступлением информационного сигнала на его вход;

- синхронные, имеющие специальный синхронизирующий вход С, сигнал которого разрешает триггеру принять новую информацию (этот сигнал называется также тактирующим, исполнительным или командным).

Синхронные триггеры в зависимости от того, какая часть синхроимпульса (СИ) оказывает влияние на изменение выходов, делятся на три основные группы:

- триггеры, управляемые уровнем синхроимпульса, когда он равен 1 или 0. Это базовые синхронные триггеры, имеющие дополнительный вход для СИ.

- триггеры, управляемые обоими фронтами СИ. Это триггеры с главной и вспомогательной памятью (JKMS).

- триггеры, управляемые одним фронтом СИ (например, D) синхронные триггеры могут быть одно- или многотактными.

2. По числу ступеней:

- одноступенчатые и

- двухступенчатые.

Двухступенчатость позволяет получить эффект задержки информации. Двухступенчатые триггеры называются также триггерами MS, поскольку одна из ступеней – slave [sleіv] (раб, невольник) повторяет состояние другой ступени – master [‘ma:ste] (хозяин, владелец, господин).

3. По способу организации логических связей, определяющих

особенности функционирования, различают триггеры RS, T, D, JK и других типов.

Основными параметрами триггеров являются: максимальная длительность входного сигнала, время задержки переключения триггера, разрешающее время триггера.

Рассмотрим свойства лишь наиболее распространенных типов триггеров, используемых при построении сложных логических схем, например таких, как счетчики и регистры.

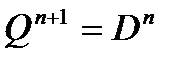

В таблице переходов, отражающей закон функционирования триггера, будем также обозначать последовательные моменты времени. Момент времени t соответствует состоянию триггера до прихода управляющих сигналов. Момент времени t+1 наступает тогда, когда сигналы на выходе триггера под воздействием сигналов на входах принимают значения, соответствующие последующему состоянию. Состояние триггера, соответствующее моменту времени t, будем обозначать  , а состояние, которое он принимает в результате воздействия входных сигналов в момент времени (t+1), -

, а состояние, которое он принимает в результате воздействия входных сигналов в момент времени (t+1), -  .

.

Знак неопределенности «x» в таблице переходов означает, что такая комбинация входных сигналов считается запрещенной, а следовательно, значение функции таких наборов произвольно.

RS-триггер

RS-триггер – ячейка хранения информации, триггер с установочным запуском - это логическое устройство с двумя устойчивыми состояниями, имеющее два информационных входа R и S, такие, что при S=1 и R=0 триггер принимает состояние 1 (Q=1), а при R=1, S=0 триггер принимает состояние 0 (Q=0).

Рисунок 1.1- RS-триггер на элементах И-НЕ и временные диаграммы его работы.

Полная таблица состояний RS-триггера представлена в табл.1.1. Методом карт Карно-Вейча выполним минимизацию переключательной функции для выхода  .

.

Таблица 1.1

При доопределении неопределенных значений (х) переключательной функции единицами получим:

(1.1)

(1.1)

В базисах И-НЕ и ИЛИ-НЕ, функция выхода RS триггера имеет вид:

(1.2)

(1.2)

Рисунок 1.2 – RS -триггер на злементах ИЛИ-НЕ и его функциональное обозначение

Задержка переключения асинхронных RS -триггеров составит сумму задержек переключения двух логических элементов, на которых выполнены триггеры, т.е.

(1.3)

(1.3)

Действительно для любой схемы при записи информации, например, по входу S (триггер находится в состоянии 0) новое устойчивое состояние триггера Q=1 сформируется через интервал времени  , отсчитываемый от момента поступления сигнала на вход S.

, отсчитываемый от момента поступления сигнала на вход S.

Для устойчивого функционирования триггера длительность сигнала действующего на его входах R и S, должна быть не меньше суммарной задержки переключения логических элементов обоих плеч триггера для полного установления новых значений выходных уровней. Для вышеприведенных схем длительность входного сигнала должна быть не меньше  , т.е.

, т.е.

Максимальная частота переключения триггера  определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S.

определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S.

(1.4)

(1.4)

Следующая maxчастота чередования сигналов на входах определяется интервалом времени  , т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при

, т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при  длительность сигналов на выходах

длительность сигналов на выходах  и

и  не будет превышать

не будет превышать

Поскольку сигналы длительностью  являются недостаточными для надежной передачи информации в логической цепи, то временной интервал между сигналами, действующими поочередно на входах триггера, приходится увеличивать, в результате чего

являются недостаточными для надежной передачи информации в логической цепи, то временной интервал между сигналами, действующими поочередно на входах триггера, приходится увеличивать, в результате чего  переключения триггера снижается. Предельная рабочая частота переключения

переключения триггера снижается. Предельная рабочая частота переключения  асинхронного RS -триггера при длительности информационного сигнала на каждом плече триггера не менее

асинхронного RS -триггера при длительности информационного сигнала на каждом плече триггера не менее  определяется из выражением

определяется из выражением

(1.5)

(1.5)

В качестве самостоятельных устройств асинхронные RS -триггеры находят ограниченное применение, но являются базовыми схемами всех более сложных триггерных устройств. В устройствах цифровой обработки информации в основном применяются синхронизируемые (тактируемые) триггеры.

В отличие от асинхронных, синхронные RS-триггеры имеют на входе каждого плеча дополнительные схемы совпадения, первые входы которых объединены и являются входом синхронизирующего импульса (СИ), а вторые входы схем совпадения являются информационными записи 1 (S) и 0 (R). Таким образом, информация, поступающая на входы R и S, может быть передана на собственно триггер только при поступлении СИ.

Рисунок 1.3 – Варианты схем синхронных RS-триггеров

Использование синхронизации определяет момент приема триггером входной информации и не допускает одновременного действия сигнала, переключающего триггер, и сигнала съема информации с триггера, обеспечивая, тем самым, правильную работу логических каскадов.

Поскольку в потенциальной системе элементов отсутствуют специальные элементы задержки сигналов, для выполнения условий надежной работы логических каскадов на каждый двоичный разряд, хранящий 1 бит информации, использовать 2 триггера, которые управляются двумя сдвинутыми во времени СИ. Таким образом удается информацию, снимаемую с выхода триггера, использовать для управления сигналами на его входах, что необходимо для построения более сложных схем.

Двойное Т в обозначении триггера означает, что он выполнен по двухступенчатой схеме.

Схема управляется либо от двух СИ, либо, как показано на рис. 1.4, от одного. В составе ИМС RS -триггеры маркируются буквами TP.

Рисунок 1.4– Двухступенчатый RS-триггер и его функциональное обозначение

Триггер D-типа, DV-типа

Триггер D-типа, DV-типа – это логическое устройство с двумя устойчивыми состояниями и одним информационным входом D (от delay – задержка, замедление).

Простейшим видом такого триггера является асинхронный D-триггер.

Таблица 1.2

(1.6)

(1.6)

Уравнение 1.6 показывает, что состояние D -триггера в момент времени  совпадает с кодом входного сигнала в момент времени

совпадает с кодом входного сигнала в момент времени  , т.е. осуществляется задержка входного сигнала.

, т.е. осуществляется задержка входного сигнала.

Рисунок 1.5 – Функциональная схема D-триггера на элементах И-НЕ и инверторах

Схема на инверторах не имеет практического применения, так как функцию D -триггера выполняет схема, состоящая из двух последовательно включенных инверторов. Наибольший интерес представляют синхронные триггеры, нашедшие широкое распространение в ИС.

Рисунок 1.6 – D-триггер двухступенчатого типа

По формальной классификации D -триггеры маркируются буквами TM.

Триггеры Т-типа

Триггером Т -типа (счетный триггер) называют логическое устройство с двумя устойчивыми состояниями и одним входом Т, изменяющее свое состояние на противоположное всякий раз, когда на вход Т поступает управляющий сигнал. Триггер типа Т можно синтезировать как из отдельных логических элементов, так и используя триггер типа D (рисунок 1.8).

Рисунок 1.7 – Т -триггер на основе RS -триггера.

Рисунок 1.8 – Т -триггер на основе D -триггера и его обозначение.

JK-триггер

Триггером JK -типа называется устройство с двумя устойчивыми состояниями и двумя входами J и K, которое при условии  осуществляет инверсию предыдущего состояния (т.е. при

осуществляет инверсию предыдущего состояния (т.е. при

), а в остальных случаях функционирует в соответствии с таблицей истинности RS -триггера, при этом вход J эквивалентен входу S, а вход К – входу R.

), а в остальных случаях функционирует в соответствии с таблицей истинности RS -триггера, при этом вход J эквивалентен входу S, а вход К – входу R.

Логическое уравнение триггера, полученное на основе таблицы 1.3 имеет вид:

(1.7)

(1.7)

Рисунок 1.9 –JK-триггер, выполненный по варианту MS с запрещающими связями с элементов 3,4 на 1 и 2.

Таблица 1.3 – Полная таблица переключений JK-триггера и его карта Карно-

Вейча

Рисунок 1.10 – JK- триггер системы ТТЛ

В серии ТТЛ JK-триггер имеет маркировку TB.

Рисунок 1.11 – Варианты построения триггерных схем на JK – триггере.

Схемные варианты триггеров

Рисунок 1.12 – Схемные варианты триггеров

Применение универсальных триггеров типа JK и DV, реализованных в одной микросхеме, в пересчетных схемах, регистрах сдвига и т.д. приводит к существенной экономии оборудования.

Естественно, что при построении системы элементов схема триггера может дополняться входной логикой, мощными выходными элементами и т.п. и применяться в нескольких модификациях. Выбор конкретной схемы во многом определяется уровнем разбиения на функциональные узлы.

Задание на самостоятельную работу

С использованием набора логических элементов выполнить схемы:

- выполнить логический анализ и записать переключательную функцию RS и JK триггеров,

-синхронного и асинхронного RS-триггера на элементной базе, указанной преподавателем,

- однотактного и двухтактного D-триггера,

- собрать один из вариантов схем триггеров рис.1.12 (по указанию преподавателя).

.

.

(1.1)

(1.1) (1.2)

(1.2) (1.3)

(1.3) , отсчитываемый от момента поступления сигнала на вход S.

, отсчитываемый от момента поступления сигнала на вход S. , т.е.

, т.е.

определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S.

определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S. (1.4)

(1.4) , т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при

, т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при  длительность сигналов на выходах

длительность сигналов на выходах  и

и  не будет превышать

не будет превышать

переключения триггера снижается. Предельная рабочая частота переключения

переключения триггера снижается. Предельная рабочая частота переключения  асинхронного RS -триггера при длительности информационного сигнала на каждом плече триггера не менее

асинхронного RS -триггера при длительности информационного сигнала на каждом плече триггера не менее  определяется из выражением

определяется из выражением (1.5)

(1.5)

(1.6)

(1.6) совпадает с кодом входного сигнала в момент времени

совпадает с кодом входного сигнала в момент времени  , т.е. осуществляется задержка входного сигнала.

, т.е. осуществляется задержка входного сигнала.

осуществляет инверсию предыдущего состояния (т.е. при

осуществляет инверсию предыдущего состояния (т.е. при

), а в остальных случаях функционирует в соответствии с таблицей истинности RS -триггера, при этом вход J эквивалентен входу S, а вход К – входу R.

), а в остальных случаях функционирует в соответствии с таблицей истинности RS -триггера, при этом вход J эквивалентен входу S, а вход К – входу R. (1.7)

(1.7)

- температурный потенциал;

- температурный потенциал;

. Таким образом информация может одновременно сниматься с запоминающей ячейки (триггера) в прямом и инверсном виде.

. Таким образом информация может одновременно сниматься с запоминающей ячейки (триггера) в прямом и инверсном виде. , а состояние, которое он принимает в результате воздействия входных сигналов в момент времени (t+1), -

, а состояние, которое он принимает в результате воздействия входных сигналов в момент времени (t+1), -  .

.