Логические элементы. Таблицы соответствия, переключательные функции.

Таблица соответствия- таблица, в которой приводится все возможные сочетания аргумента функции и соответств. им значение логической функции.

Конъюнкция – логическое умножение

Дизъюнкция – логическое сложение

Элемент Шеффера, И-НЕ

,

Элемент Пирса, ИЛИ-НЕ

,

Элемент неравнозначности

,

,

Элемент И-ИЛИ-НЕ

Теорема Де Моргана:

КНФ и ДНФ переход от одной формы к другой

ДНФ - дизъюнкция элементарных конъюнкций.

Правило. Если переменная в данном объединении имеет значение, равное «1», то она записывается в прямом виде.

Если переменная в данном объединении равна «0», то она записывается в инверсном виде.

Если переменная равна и «0» и «1», в данном объединении, то она из него исключается.

Fднфmin=

КНФ - конъюнктивная нормальная форма- конъюнкция элементарных дизъюнкций.

(a+b)*(b+  *(

*( +c)

+c)

Составляется по «0» карт Карно.

Если переменная в данном объединении имеет значение «0», то она записывается в элементарную дизъюнкцию в прямом виде.

Если переменная в данном объединении имеет значение «1», то она записывается в обратном виде.

Если переменная в данном объединении имеет значение и «0» и «1», то она исключается.

3) СКНФ и СДНФ переход от одной формы к другой

Карты Карно

Таблица:

а: 0 0 0 0 1 1 1 1

b: 0 0 1 1 0 0 1 1

c: 0 1 0 1 0 1 0 1

f: 1 1 0 0 1 1 0 1

Карта Карно минимизируется по 0 – ям и 1 – ам. Если карта Карно оптимизируется по 0 – ям, то переменные включаются в элементарные дизъюнкции соединенные между собой знаками конъюнкции.

В элементарные дизъюнкции включаются те переменные значение которых равно либо 0-ю либо 1-е.

Для оптимизации карт Карно по 1 – ам, переменные включаются в элементарные конъюнкции соединенные между собой знаками дизъюнкции.

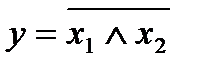

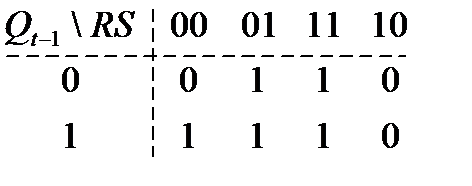

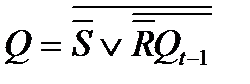

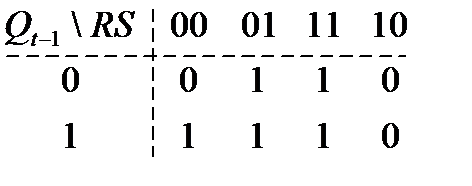

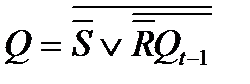

RS триггер на элементах И-НЕ

Триггер - это элементарная ячейка памяти, которая может хранить 2 состояния: либо «0» либо «1». Переход из одного состояния в другое осуществляется скачком. Уровень сигнала на прямом выходе триггера определяется его составляющими в конкретный момент времени.

Для построения RS – триггера на элементах И-НЕ неопределенные состояния заменим 1-ми:

Для построения RS – триггера на элементах И-НЕ преобразуют переключательную функцию по т. Де Моргана:

Управление в данной схеме ведется нулевым уровнем сигнала. Для RS – триггера построенного на И-НЕ элементах реализуется обратная логика, т.е. нулевой уровень сигнала на входе S переводит триггер в единичное состояние. Сочетание R=0 и S=0, является запрещенным для данного триггера. R=1 и S=1 приводит к хранению предыдущего состояния триггера

Временная диаграмма:

Т – триггер

Триггер- это элементарная ячейка памяти, которая может хранить 2 состояния: либо «0» либо «1». Переход из одного состояния в другое осуществляется скачком. Уровень сигнала на прямом выходе триггера определяется его составляющими в конкретный момент времени.

Данный вид триггеров реализует функцию сложения по модулю 2-а, а также на каждые 2-а входных сигнала на счетном входе «T» получаем один выходной сигнал.

Схема асинхронного, двухтактного T – триггера:

Предположим, что предыдущее состояние триггера было нулевое, соответственно ан прямом выходе Q=0, а на инверсном  . В этом случае единичный уровень сигнала поступает на вход «S», нулевой на «R», если при этом T=1, то происходит запись 1-цы в первую ступень триггера (т.е. 1,2,3,4).

. В этом случае единичный уровень сигнала поступает на вход «S», нулевой на «R», если при этом T=1, то происходит запись 1-цы в первую ступень триггера (т.е. 1,2,3,4).

При перемене сигнала на счетном входе «T», т.е. T=0, происходит смена сигнала на выходе второй ступени (т.е. 5,6,7,8), и на прямом выходе T –триггера появляется 1-а.

Управление ведется по заднему фронту.

Д- триггер

Триггер- это элементарная ячейка памяти, которая может хранить 2 состояния: либо «0» либо «1». Переход из одного состояния в другое осуществляется скачком. Уровень сигнала на прямом выходе триггера определяется его составляющими в конкретный момент времени.

!!!D – триггер (триггер с задержкой по времени)

Асинхронные D –триггеры являются повторительными, поэтому для практической реализации функции с задержкой времени используются однотактные и двухтактные D –триггеры.

Управление ведется по переднему фронту единичного сигнала входа синхронизации. Максимальная задержка сигнала однотактного D – триггера на выходе  сигнала на входе.

сигнала на входе.

Двухтактный синхронный D – триггер отличается от однотактного тем, что задержка по времени на Т.

JK – триггер

Триггер- это элементарная ячейка памяти, которая может хранить 2 состояния: либо «0» либо «1». Переход из одного состояния в другое осуществляется скачком. Уровень сигнала на прямом выходе триггера определяется его составляющими в конкретный момент времени.

Может реализовывать все функции предыдущих триггеров.

Главное отличие JK – триггера: не имеет запрещенных состояний.

1 – хранение 0-я;

2 – подтверждение 0-я;

3 – установка 1-цы;

4 – переход в противоположное состояние;

5 – хранение 1-цы;

6 – переход в 0-ое состояние;

7 – подтверждение 1-цы;

8 – переход в противоположное состояние;

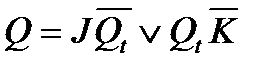

Карта Карно для JK – триггера:

Сигнал на выходе триггера в последующий момент времени изменяется на противоположный, если J=1, или равен предыдущему если K=0, если J=K=1, то триггер работает в режиме счетного триггера, если размыкается обратная связь, то триггер работает в режиме синхронного RS – триггера, если на J и K одновременно подавать противоположные сигналы, то триггер работает в режиме D – триггера.

Незадействованные входы элементов & являются свободными для наращивания схемы.

11)Регистры последовательный и параллельный

Регистр – этот узел ЭВМ предназначенный для хранения кода слова, и выполнения над хранимым словом ряда операций.

Регистры строятся на триггерах.

Количество разрядов регистров равно количеству триггеров, входящих в его состав.

ü Параллельный регистр – предназначен для хранения кода слова, и передача слова в другой регистр;

ü Последовательный регистр – предназначен для последовательного сдвига слова влево или вправо;

Трехразрядный параллельный регистр на базе однотактных D – триггеров.

Q=x0*V

Q1=x1*V

Q2=x2*V

Информационный вход V- запись кода слова

Установка «0»- подача «1» на данный вход обнуляет все разряды.

Данный регистр носит название однофазного регистра, т.к. запись слова происходит по одному информационному входу «V».

Время срабатывания данного регистра определяется как сумма времени срабатывания триггера и времени срабатывания элемента «И».

Т

р=Т

тр+Т

&

Ттр – время срабатывания триггера

Т& – время срабатывания элемента &

Для увеличения быстродействия регистров, используются регистры с парафазным входом, где каждому разряду соотв. 2 информационных входа, которые являются взаимно инверсными, что приводит к однозначности при установке всех разрядов регистра.

Трехразрядный последовательный сдвигающий регистр построенный на синхронных D – триггерах

R – установка триггеров в 0-ое состояние

ОС – обратная связь.

С – номер такта, Q0,Q1,Q2 – входы регистра.

При каждом тактовом импульсе происходит сдвиг кода слова вправо.

Для сохранения информации в регистре при ее передачи в другой регистр вводится обратная связь, и вместе с записью информации в следующий регистр происходит восстановление информации в исходный регистр.

Сдвигающие регистры могут быть реверсивными, т.е. осуществлять сдвиг информации как влево так и вправо в зависимости от сигнала в цепи управления.

Универсальный регистр

Регистр – этот узел ЭВМ предназначенный для хранения кода слова, и выполнения над хранимым словом ряда операций.

Регистры строятся на триггерах.

Количество разрядов регистров равно количеству триггеров, входящих в его состав.

Универсальный последовательный параллельный регистр (5 элементов 2-И-ИЛИ, 4 синхронных D – триггера)

При последовательном режиме работы регистра вход V=1, и код слова последовательно через вход D поступает в триггеры.

Входные сигналы b0…b3 являются информационными входными сигналами для триггеров и зависят от выхода триггера предыдущего разряда (предыдущего триггера).

Если V=0, осуществляется параллельный режим работы регистра, срабатывают информационные входы х0…х1, и входные сигналы триггеров b0…b3 определяются параллельным кодом слова.

Кольцевой счетчик

Счетчик – это узел ЭВМ предназначенный для счета входных сигналов, и хранения кода подсчитанных сигналов

Используется для выдачи циклического хода. При разрыве обратной связи счетчики могут быть использованы как суммирующие счетчики с последовательным переносом.

Функциональная схема трехразрядного кольцевого счетчика на JK – триггерах.

Входы S – независимые входы предварительной установки счетчика.

R – исходная установка счетчика в нулевое состояние.

t1 – начальный момент времени.

Т – входной счетный сигнал.

Q – выходы.

После установки всех разрядов в 0-ое состояние, по входам х1…х3 можно установить любой двоичный код счета.

S – установка счетчика либо в нулевое либо в единичное состояние.

Х1…Х4 – установка кода.

С – вход синхронизации.

+1,-1 – счетные входы, соответственно для суммирующего и

вычитающего режима.

0…3 – информационные выходы.

Р – выход переноса.

Дешифраторы

!!!Дешифратор(кодер)- узел ЭВМ, который имеет n-входов и 2n выходов. Определенные комбинации входных сигналов соответственно единичный сигнал на одной из выходных шин. Дешифраторы бывают: матричные(базовые)-2 входа 4 выхода, пирамидальные(3 входа-8 выходов) и прямоугольные-(4 входа- 16 выходов).

Д. могут быть построены на элементах И. и могут перейти на элементы ИЛИ-НЕ.

| X0

| X1

| X2

|  y y

|

|

|

|

| y0

|

|

|

|

| y1

|

|

|

|

| y2

|

|

|

|

| y3

|

|

|

|

| y4

|

|

|

|

| y4

|

|

|

|

| y6

|

|

|

|

| y7

|

Прямоугольный дешифратор.

(4 входа, 16 выходов)

Дешифратор(кодер)- узел ЭВМ, который имеет n-входов и 2n выходов.

В прямоугольных - осуществляется ступенчатая дешифрация. Входное слово разбивается на группы разрядов и каждая из групп обрабатывается матричным дешифратором. На второй ступени дешифрации (конечной или промежуточной) образуется произведение сигналов, поступающих из первой ступени. Пример прямоугольного дешифратора представлен на рис. 2.

Рис. 2 Прямоугольный дешифратор на 4 входа

Особенностью пирамидальных дешифраторов является легкость наращивания количества входов, недостатком – аппаратная избыточность.

Кроме того, известны дешифраторы, переводящие код 1248 в код семи сегментного индикатора, обеспечивающего свечение соответствующих сегментов на поле индикатора. На индикаторе при этом появляется десятичное число от 0 до 9.

Каскадный дешифратор.

Дешифраторы - Это комбинационные схемы с несколькими входами и выходами, преобразующие код, подаваемый на входы в сигнал на одном из выходов. На выходе дешифратора появляется логическая единица, на остальных — логические нули, когда на входных шинах устанавливается двоичный код определённого числа или символа, то есть дешифратор расшифровывает число в двоичном, троичном или k-ичном коде, представляя его логической единицей на определённом выходе. Число входов дешифратора равно количеству разрядов поступающих двоичных, троичных или k-ичных чисел. Число выходов равно полному количеству различных двоичных, троичных или k-ичных чисел этой разрядности.

Для n-разрядов на входе, на выходе 2n, 3n или kn. Чтобы вычислить, является ли поступившее на вход двоичное, троичное или k-ичное число известным ожидаемым, инвертируются пути в определённых разрядах этого числа. Затем выполняется конъюнкция всех разрядов преобразованного таким образом числа. Если результатом конъюнкции является логическая единица, значит на вход поступило известное ожидаемое число.

Из логических элементов являющихся дешифраторами можно строить дешифраторы на большое число входов. Каскадное подключение таких схем позволит наращивать число дифференцируемых переменных.

Шифраторы

Шифратор (кодер) преобразует единичный сигнал на одном из входов в n-разрядный двоичный код. Наибольшее применение он находит в устройствах ввода информации (пультах управления) для преобразования десятичных чисел в двоичную систему счисления. Предположим, на пульте десять клавиш с гравировкой от 0 до 9. При нажатии любой из них на вход шифратора подается единичный сигнал (Х0,..., Х9). На выходе шифратора должен появиться двоичный код (Y0,..., Y9) этого десятичного числа. Как видно из таблицы истинности (таблица В), в этом случае нужен преобразователь с десятью входами и четырьмя выходами.

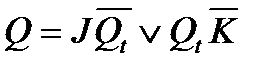

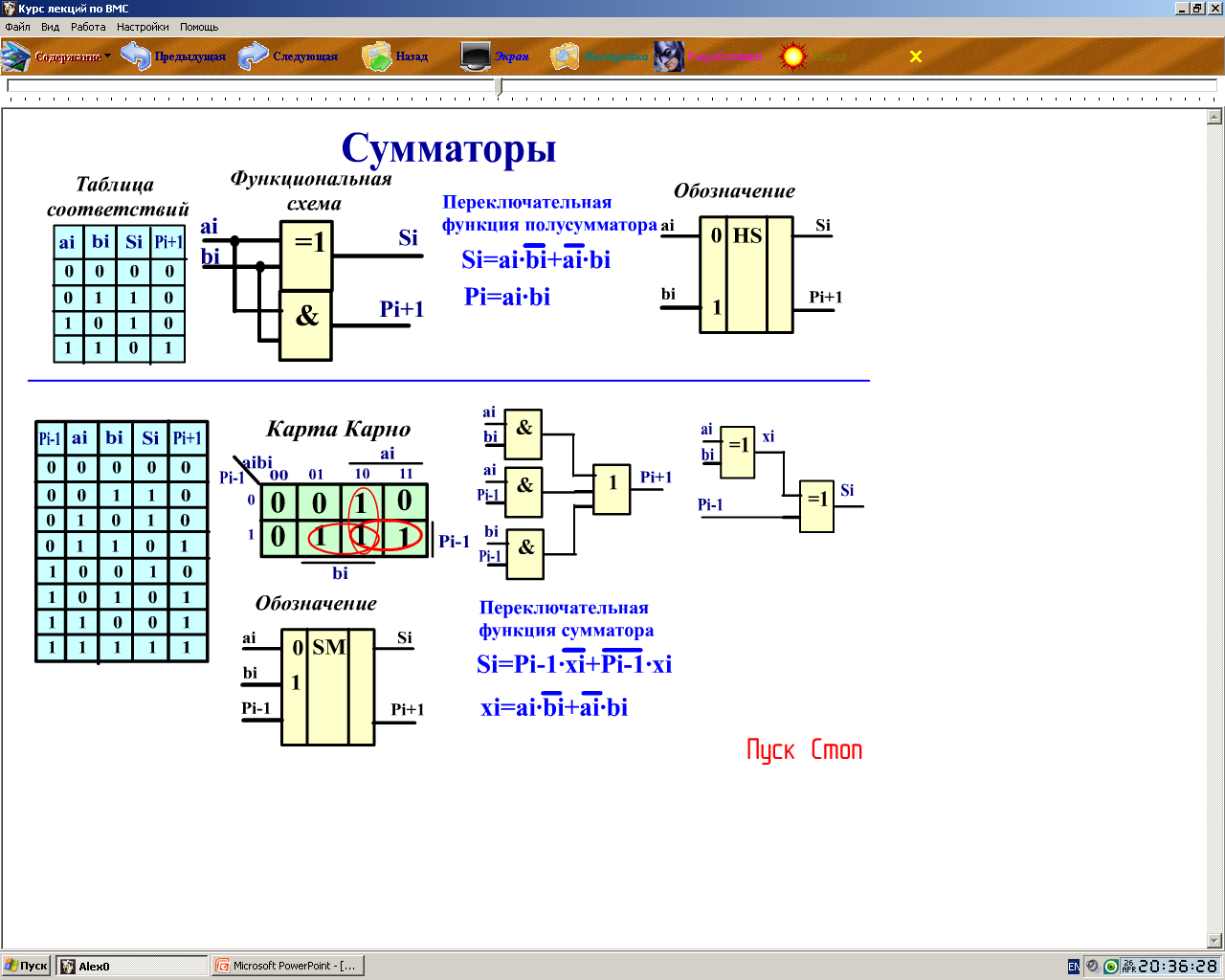

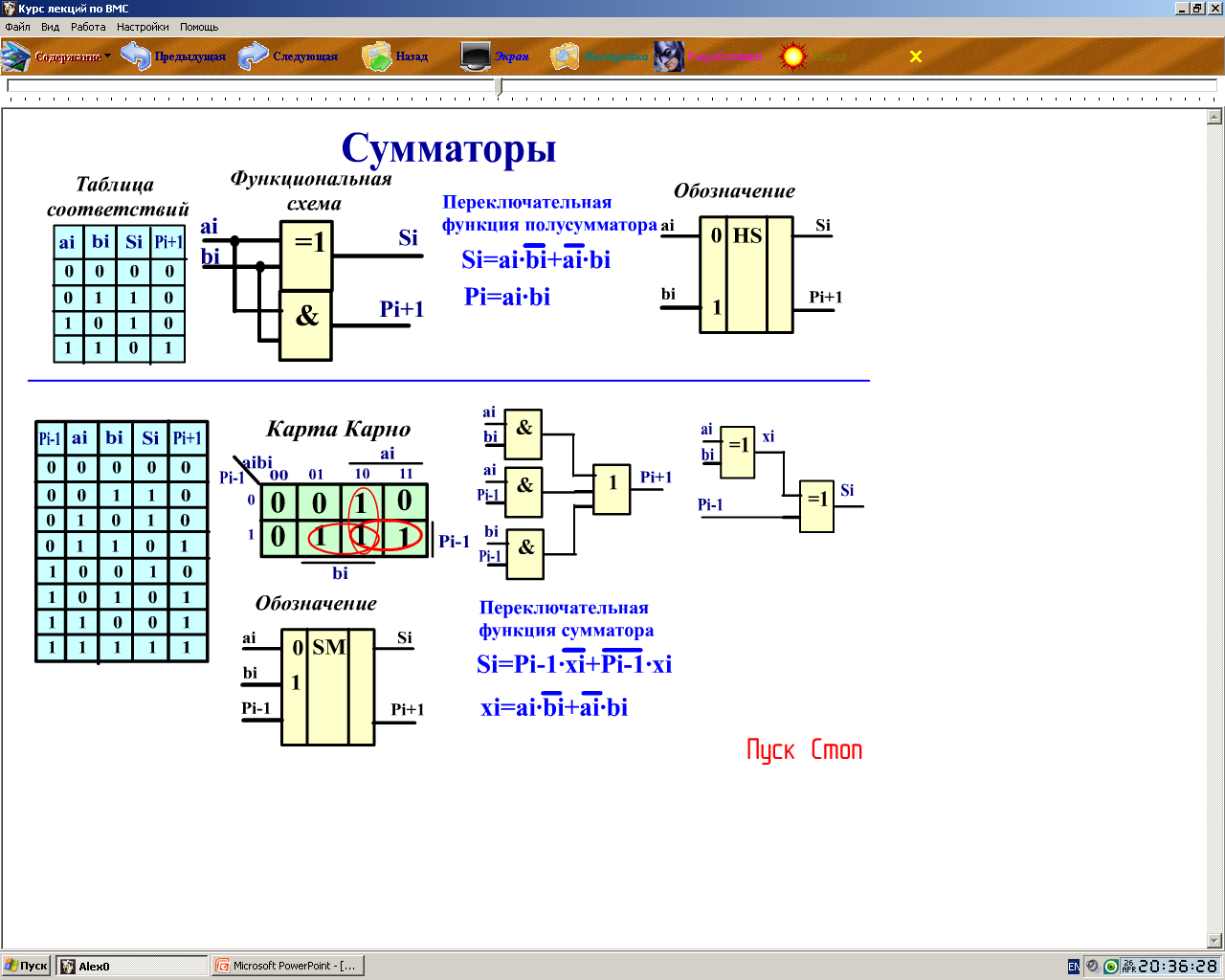

Сумматоры

!!!Сумматор — логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. Указанные операции выполняются в арифметическо-логических устройствах (АЛУ) или процессорных элементах, ядром которых являются сумматоры.

Существуют два типа сумматоров: комбинационные (не содержат элементов в памяти) и накапливающие (содержат элементы памяти). Комбинационные делятся на параллельные и последовательные. В последовательных сумматорах цифра переноса формируется последовательно от разряда к разряду. В параллельных цифра переноса одновременно подаются на все разряды.

Полусумматор

!!!Полусумматор - это устройство, которое содержит 2 входа и 2 выхода.

Ai и Bi –входы для передачи цифр, которые обрабатываются в полусумматоре.

Выход Si-это выход, на котором формируется цифра и результат операции данного конкретного разряда.

Pi+1 – выход, на котором формируется цифра переноса в старший разряд.

Мультиплесоры

!!!Мультиплексор - комбинационное цифровое устройство, которое обеспечивает передачу на единственный выход F одного из нескольких входных сигналов Dj в соответствии с поступающим адресным кодом Ai. При наличии n адресных входов можно реализовать M=2n комбинаций адресных сигналов, каждая из которых обеспечивает выбор одного из M входов. Чаще всего используются мультиплексоры «из 4 в 1» (n=2, M=4), «из 8 в 1» (n=3, M=8), «из 16 в 1» (n=4, M=16). Правило работы мультиплексора «из 4 в 1» можно задать таблицей истинности:

| Входы

| Выход

|

| A1

| A0

| F

|

|

|

| D0

|

|

|

| D1

|

|

|

| D2

|

|

|

| D3

|

.

.

Демультиплексоры

!!!Демультиплексор выполняет функцию, обратную мультиплексору, т.е. в соответствии с принятой адресацией Ai направляет информацию с единственного входа D на один из M выходов Fj. При этом на остальных выходах будут логические нули (единицы). Принцип работы демультиплексора «из 1 в 4» иллюстрируется таблицей истинности:

Ассоциативное ЗУ

Данные устройства используются для КЭШ памяти 2-го уровня.

Поиск и запись информации ведется по ассоциативному признаку сразу по всем ячейкам запоминающего массива, что увеличивает скорость поиска информации.

Помимо хранения информации данное ЗУ дает информации о количестве хранимой информации.

РгАП – регистр ассоциативного признака

РгМ – регистр маски. В нем маскируется та информация которая не используется, что ускоряет поиск.

ЗМ – запоминающий массив (N – число регистров)

РгИ – регистр информации

КС – комбинационная схема. В нее поступают все значения служебного разряда n.

РгП – регистр признака или результата

ФС – формирователь сигнала, который передает результаты поиска информации.

ШД – шина Данных

a0=1, если в запоминающем массиве не найдена искомая информация.

a1=1, если искомая информация найдена только в одной строке.

a2=1, если искомая информация найдена в более чем одной строке.

Вспомогательные устройства КС, РгП, ФС расширяют память ЗУ.

РгАП содержит в себе признак информации которую необходимо искать.

В РгМ в 0-ль устанавливаются те разряды в которых поиск информации не ведется.

РгИ при операции чтения, служит для хранения информации поступающей с запоминающего массива, которая затем передается на ШД. При записи информации данный регистр служит ячейкой для передачи информации с ШД в запоминающий массив.

Разряды РгАП, РгМ, и ЗМ не несут в себе информацию о состоянии данного устройства, и являются служебными разрядами.

КС не имеет памяти при этом анализирует состояние служебных разрядов и выставляет в соответствующие положения определенные разряды регистра признака, по состоянию которого ПС выдает соответствующие сигналы, по которым без считывания информации можно судить о состоянии ЗМ.

Накапливающее АЛУ

Рассмотрим структурную схему оп1 и оп2 подаются последовательно и запоминаются в аккумуляторе (АК), затем данные операнды поступают в блок логических операций (БЛОП), где производится сложение и вычитание данных операндов. Затем результат поступает в буферный регистр (БР) либо обратно в АК. После обработки информации результат поступает на выходную шину.

В данных АЛУ могут выполняться операции * и /, т.к. буферный регистр является ячейкой памяти. АК в данной схеме служит для хранения сомножителя или делителя.

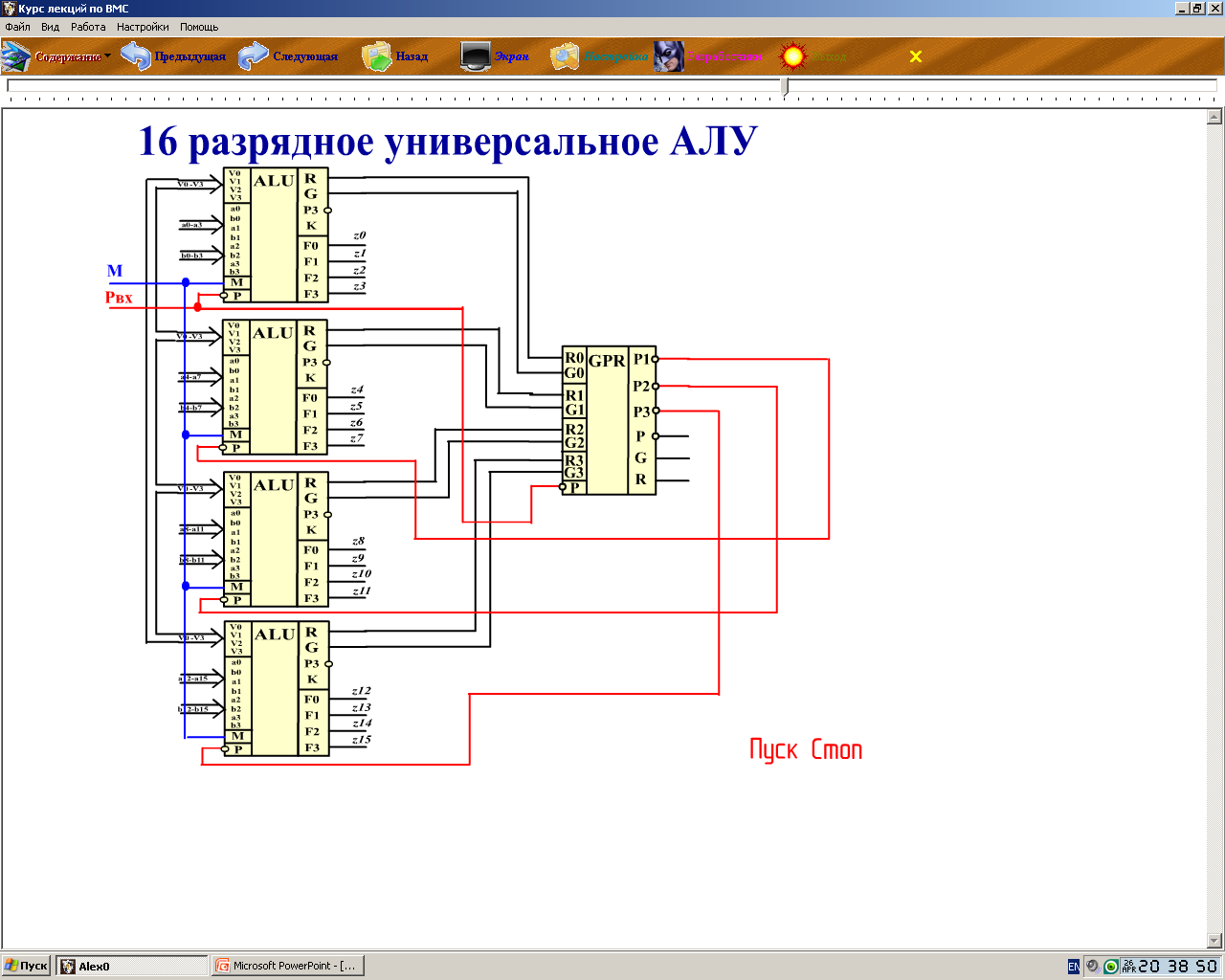

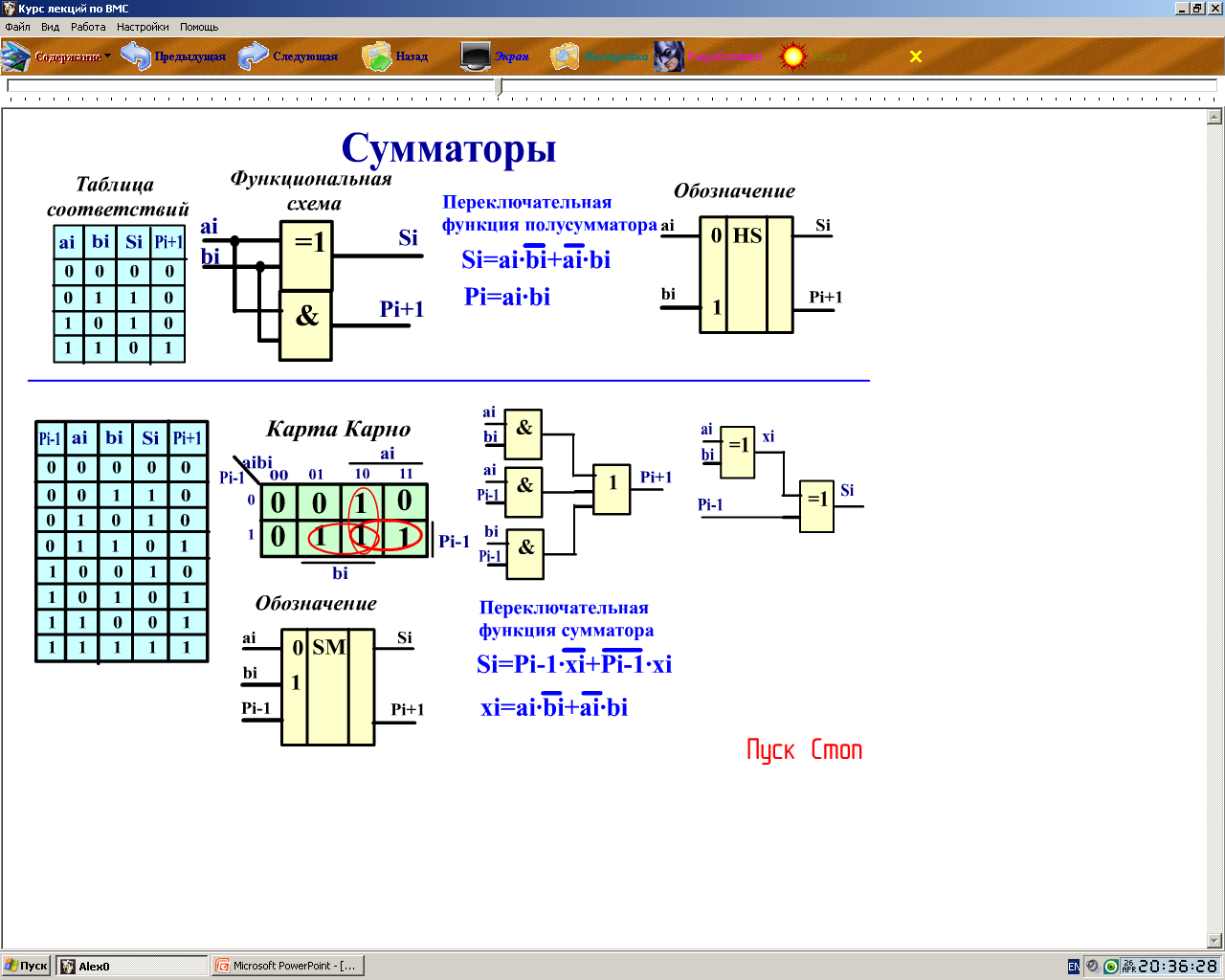

Разрядное универсальное АЛУ

Входы:

V0 – V3 – управляющие диоды;

а0 – а3 – информационный вход 1-го слагаемого;

b0 – b3 – информационный вход 2-го слагаемого;

М – режим работы АЛУ, если М=1 выполняется логическая операция, если М≠0 – а-л операция.

Выходы:

R – сигнал распространения переноса;

G – выход генерации переноса;

PЗ – выход переноса старший разряд;

K – результат сравнения кодов чисел;

F0 – F3 – результат операций.

Блок прерываний процессора

В состав блока прерывания входит регистр запроса прерывания, который строится на базе однотактных RS – триггеров также входит в регистр маски запросов прерывания.

1-ый блок триггеров – регистр запроса прерывания;

2-ой блок триггеров – SZ – регистр маски запроса прерывания;

3-ий блок триггеров – сигнал выработки запроса прерывания;

ДС – дешифратор; СД – шифратор; РгК – регистр команд.

На входы «S» регистра запроса прерывания подается запрос прерывания α1-αn

на вход S регистра маски подается программно - формируемая маска прерывания (Z1,...,Zn)

Логические элементы. Таблицы соответствия, переключательные функции.

Таблица соответствия- таблица, в которой приводится все возможные сочетания аргумента функции и соответств. им значение логической функции.

Конъюнкция – логическое умножение

Дизъюнкция – логическое сложение

Элемент Шеффера, И-НЕ

,

Элемент Пирса, ИЛИ-НЕ

,

Элемент неравнозначности

,

,

Элемент И-ИЛИ-НЕ

Теорема Де Моргана:

,

,

,

,

,

,  ,

,

*(

*( +c)

+c)

. В этом случае единичный уровень сигнала поступает на вход «S», нулевой на «R», если при этом T=1, то происходит запись 1-цы в первую ступень триггера (т.е. 1,2,3,4).

. В этом случае единичный уровень сигнала поступает на вход «S», нулевой на «R», если при этом T=1, то происходит запись 1-цы в первую ступень триггера (т.е. 1,2,3,4).

сигнала на входе.

сигнала на входе.

y

y

.

.