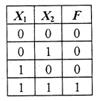

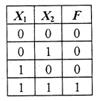

Логика работы ЛЭ ИЛИ представлена в табл.

Логика работы ЛЭ ИЛИ представлена в табл.

Выражение для выходной булевой функции:  .

.

Высокий уровень напряжение  на выходе диодного элемента ИЛИ устанавливается при подаче на один или оба входа высоких уровней напряжения

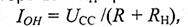

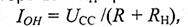

на выходе диодного элемента ИЛИ устанавливается при подаче на один или оба входа высоких уровней напряжения  , при которых открываются соответствующие диоды VD1 или VD2, либо оба вместе. В резистор нагрузки RH втекает выходной ток IOH, определяемый по формуле:

, при которых открываются соответствующие диоды VD1 или VD2, либо оба вместе. В резистор нагрузки RH втекает выходной ток IOH, определяемый по формуле:  .

.

Значение выходного высокого уровня  зависит от входных напряжений:

зависит от входных напряжений:

, где U* =0,8 В – прямое падение напряжения на кремниевом диоде.

, где U* =0,8 В – прямое падение напряжения на кремниевом диоде.

Для  = 5 В, RH = 1 кОМ, получим:

= 5 В, RH = 1 кОМ, получим:

При подаче одновременно на оба входа низких уровней напряжения UIL ≤ 0.4 В, диоды закрыты, ток в цепи нагрузки не протекает и выходное напряжение почти равно нулю.

На выходе элемента обычно имеется паразитная емкость СП =25…100 пФ, вследствие чего длительность фронта tLH очень мала (емкость быстро заряжается от источника входных сигналов через малое прямое сопротивление открытого диода), а длительность спада tHL велика (диоды закрыты и емкость разряжается через резистор RH). Поэтому для диодных схем ИЛИ выполняется неравенство tLH << tHL.

Логика работы ЛЭ И на два входа представлена в табл., на основе которой получают выражение для выходной булевой функции:

Логика работы ЛЭ И на два входа представлена в табл., на основе которой получают выражение для выходной булевой функции:  .

.

Высокий уровень напряжения  на входе диодного элемента И устанавливается только при одновременной подаче на оба входа высоких уровней напряжения

на входе диодного элемента И устанавливается только при одновременной подаче на оба входа высоких уровней напряжения  , при которых закрываются диоды VD1 и VD2. При этом от источника питания UCC через резисторы R и R H протекает ток нагрузки:

, при которых закрываются диоды VD1 и VD2. При этом от источника питания UCC через резисторы R и R H протекает ток нагрузки:

который определяет значение высокого уровня выходного напряжения

Как правило, используют значения R=1…2 кОм и R H> R. Длительность фронта выходного сигнала tLH определяется временем заряда паразитной емкости CП через большое сопротивление резистора R. Если на один из входов, например, X1 подан низкий уровень напряжения  , то диод VD1 открывается. При этом от источника питания UCC по цепи: резистор R, открытый диод VD1 и источник входного сигнала X1 – протекает ток, значение которого определяется из выражения:

, то диод VD1 открывается. При этом от источника питания UCC по цепи: резистор R, открытый диод VD1 и источник входного сигнала X1 – протекает ток, значение которого определяется из выражения:

Оптоэлектроника – раздел науки и техники, изучающий как оптические, так и электронные явления в веществах, их взаимные связи и преобразования, а также приборы, схемы и системы, созданные на этих явлений.

Оптоэлектронные ИС изготавливают, в основном, по гибридной полупроводниковой технологии.

Схема может находиться в 2-х состояниях. Если через СИД (светоизлучающий диод) протекает номинальный прямой ток, СИД излучает и вызывает фототок в фотодиоде оптрона. Ток фотодиода одновременно является отпирающим базовым током транзистора VT1, который открывается.

При открытом VT1 закрывается VT2 и открывается VT3. На выходе 0.

Когда входной ток равен нулю, через фотодиод оптрона протекает лишь темновой ток и транзистор VT1 заперт, открывается VT2, закрывается VT3 и на выходе напряжение источника питания (5 В минус падение напряжения в цепи R4 – VT2 – диод).

3. Базовый элемент транзисторно-транзисторной логики (ТТЛ: принципиальная схема, работа элемента). Понятие нагрузочной способности элемента ИС ТТЛ, как она определяется?

Основная особенность ИС ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерным транзистор. От обычных биполярных транзисторов он отличается тем, что имеет несколько эмиттеров (2, 3, 4, 8), объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому многоэмиттерный транзистор можно рассматривать как совокупность нескольких транзисторов с объединенным коллекторами и базами.

Принципиальная схема базового элемента ТТЛ 155 серии выглядит так.

Схема содержит три каскада: входной R1, VT1, VD1 – VD4, фазорасщипительный R2, VT2, R3, R4, VT3, выходной VT4, VT5, VD5, R5.

Диоды VD1 – VD4 носят название антизвонных и при нормальном использовании ИС смещены в обратном направлении, имеют очень большое сопротивление (по меркам ТТЛ схем), и не влияют на работу схемы.

При подаче на все входы высоких уровней напряжения ток базы VT1 переключается на базу транзистора VT2, открывая и насыщая его. Приращение напряжений на эмиттере и коллекторе VT2 находится в противофазе. В этой ситуации напряжение на эмиттере увеличится, на коллекторе – уменьшится. На выходе напряжение, равное падению напряжения на VT5 от втекающих токов подключенных входов.

Когда хотя бы на одном из входов напряжение низкого уровня, ток базы транзистора VT1 течет через эмиттер. Поэтому VT2 закрыт. При закрытом VT2 закрыт VT5, открыт VT4.

Подключенный резистор увеличивает входное напряжение, но снижает быстродействие и нагрузку.

Переключение сопровождается бросками тока в выходной цепи (VT4 еще не закрылся, а VT5 уже открылся). Ставят керамический конденсатор на корпусе и электролитический на плате.

Нагрузочная способность определяется током, который может быть отдан данным ЛЭ во внешние цепи (нагрузку) или принят от нее. В случае однородных нагрузок, создаваемых входами идентичных ЛЭ, нагрузочная способность оценивается коэффициентом разветвления, т.е. числом входов последующих ЛЭ, которые могут быть подключены к выходу данного. Коэффициент разветвления определяется с учетом быстродействия нагруженного элемента. Для некоторых типов схемотехники задержка элемента практически пропорциональна емкостной нагрузке. При этом каждый вход, подключенный к данному выходу, увеличивает емкостную нагрузку. Для обеспечения задержки, не превосходящей заданную, может оказаться необходимым ограничить коэффициент разветвления значением, которое намного меньше допустимого по условиям работы элемента в статике. Нагрузочная способность элемента ТТЛ определяется низким уровнем на выходе (0 на выходе), так как в таком случае через открытые транзисторы потекут токи, а нижний транзистор выходного каскада открыт.

4. Базовый элемент ИС диодно-транзисторных схем на диодах и транзисторах Шотки (принципиальная схема 530/531, 533/555, отличия от классических ТТЛ). Почему в выходном каскаде ТТЛ ИС возникают броски тока и как с ними бороться?

5. Схемы базовых элементов серий 1531, 1533.Отличие серий 1531, 1533 от 531 и 533.

6. Логические элементы ИС ТТЛ с тремя состояниями выхода. Подключение неиспользуемых логических элементов и входов ИС ТТЛ?

7. Логические элементы ИС ТТЛ с открытым коллектором. Получение монтажного «И» на элементах с открытым коллектором. Схемы подключения индикации и формулы расчёта RН.

8. Цифровые ИС на n -MOП структурах (принципиальная схема инвертора, работа; принципиальная схема базового элемента, его работа). Сформулировать отличия n -МОП от p -МОП структур.

9. Цифровые ИС на КМОП-стуктурах (принципиальная схема инвертора и его работа; принципиальная схема элемента ИЛИ-НЕ и его работа). Особенности применения ИС КМОП.

10. Достоинства и недостатки ИС КМОП. Согласование ИС ТТЛ-уровней с ИС КМОП, ИС КМОП с ИС ТТЛ-уровней.

11. Кроссбар-архитектуры.

12. Общие сведения об оптоэлектронных приборах, используемых в вычислительной технике. Обобщенная структурная схема оптрона. Оптопары (виды оптопар, некоторые параметры оптопар).

13. Изолирующие ИС на основе iCoupler.

14. Классификация триггеров. Асинхронный RS-триггер (схемы на элементах И-НЕ, ИЛИ-НЕ, таблицы функционирования и временные диаграммы, время задержки).

15. Синхронный (статический) одноступенчатый и двухступенчатый RS-триггеры (функциональная схема на элементах И-НЕ, ИЛИ-НЕ, работа, время задержки).

16. Синхронный (динамический) RS-триггер (функциональная схема на элементах И-НЕ, работа, время задержки). Построение D-, Т-, JK-триггеров на основе синхронных (одноступенчатых, двухступенчатых, динамических) RS-триггеров.

Логика работы ЛЭ ИЛИ представлена в табл.

Логика работы ЛЭ ИЛИ представлена в табл. .

. на выходе диодного элемента ИЛИ устанавливается при подаче на один или оба входа высоких уровней напряжения

на выходе диодного элемента ИЛИ устанавливается при подаче на один или оба входа высоких уровней напряжения  , при которых открываются соответствующие диоды VD1 или VD2, либо оба вместе. В резистор нагрузки RH втекает выходной ток IOH, определяемый по формуле:

, при которых открываются соответствующие диоды VD1 или VD2, либо оба вместе. В резистор нагрузки RH втекает выходной ток IOH, определяемый по формуле:  .

. , где U* =0,8 В – прямое падение напряжения на кремниевом диоде.

, где U* =0,8 В – прямое падение напряжения на кремниевом диоде.

Логика работы ЛЭ И на два входа представлена в табл., на основе которой получают выражение для выходной булевой функции:

Логика работы ЛЭ И на два входа представлена в табл., на основе которой получают выражение для выходной булевой функции:  .

.

, то диод VD1 открывается. При этом от источника питания UCC по цепи: резистор R, открытый диод VD1 и источник входного сигнала X1 – протекает ток, значение которого определяется из выражения:

, то диод VD1 открывается. При этом от источника питания UCC по цепи: резистор R, открытый диод VD1 и источник входного сигнала X1 – протекает ток, значение которого определяется из выражения: