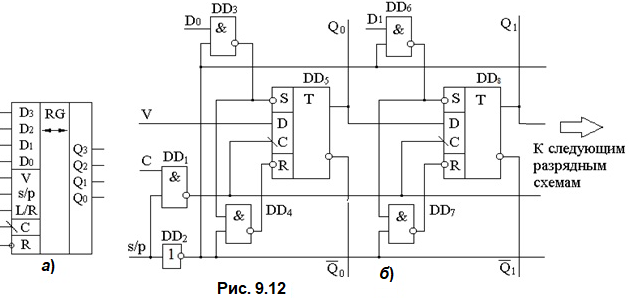

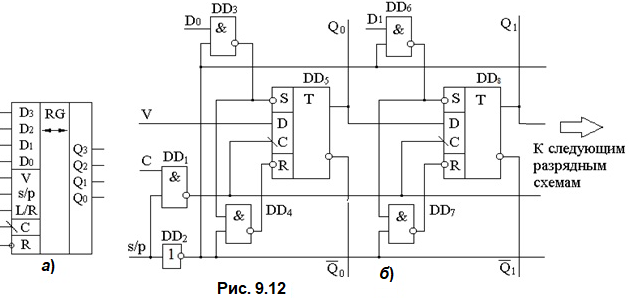

9.5.2. Последовательный регистр. На рис. 9.12 приведено условное обозначение (а) (стрелки указывают направление сдвигов информации) и фрагмент схемы (б) многоразрядного последовательного регистра.

Выбор режима его работы осуществляется посредством сигнала s / p. Если s / p = 1, то элемент DD1 превращается в инвертор, формируя на внутренней шине регистра инверсию от последовательности импульсов синхронизации. По фронту импульса синхронизации информация с входа последовательного приема информации V записывается в триггер DD5. Одновременно информация, хранившаяся в триггере DD5, переписывается в триггер DD8 и т.д., т.е. происходит последовательная запись информации с одновременным ее сдвигом из младших разрядов в старшие (сдвиг влево).

Элементы DD6, … и DD4, DD7, …, формируя на всех входах асинхронной установки триггеров регистра пассивные логические сигналы, препятствуют параллельной записи информации.

Если s / p = 0, то сигнал синхронизации блокируется, а входы параллельной записи информации подключаются к внешним входам Di, причем на входы R и S всегда приходят инверсные сигналы, т.е. исключается подача запрещенной для входов R и S комбинации информационных сигналов.

9.5.3. Реверсивный и параллельный регистры. Если связь между триггерами регистра сделать настраиваемой, то можно управлять направлением сдвига информации. Фрагмент схемы реверсивного регистра, реализующий данный принцип, показан на рис. 9.13.

Для изменения направления передачи информации в схеме использован элемент сложной логики DD2, DD4,..., фактически выполняющий функцию мультиплексора, управляемого одноразрядным адресным словом. Если сигнал L / R = 1, нижние элементы И в DD2, DD4, … формируют на входах элементов ИЛИ сигналы 0. Поэтому выходной сигнал DD2 равен V, выходной сигнал DD4 равен Q 0 и т.д. Реализуется режим последовательной записи информации в младший разряд с одновременным сдвигом влево (из младших разрядов в старшие).

При L / R = 0 на выходах верхних элементов И в DD2, DD4, … формируется сигнал 0 и на выходе DD2 формируется сигнал Q 1, на выходе DD4 – сигнал Q 2 и т.д., т.е. происходит сдвиг информации вправо (из старших разрядов в младшие).

Параллельный регистр выполняет микрооперации только над кодовыми словами, представленными в параллельной форме (сброс, запись, хранение и выдача информации). Поэтому его разрядные схемы связаны между собой только общими сигналами управления и не могут обмениваться хранящейся в них информацией. Разрядные схемы этих регистров наиболее часто выполняются с использованием D -триггеров.

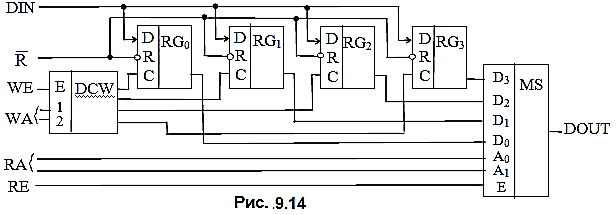

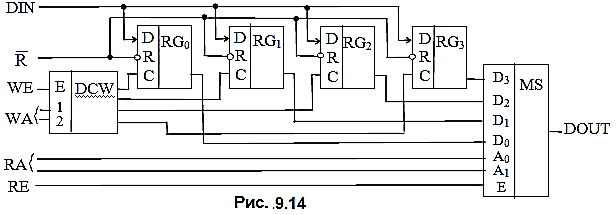

9.5.4. Регистровая память. Объединивв одной микросхеме несколько регистрови добавив на входе дешифраторDCW, а на выходе мультиплексор MS, получают регистровую (сверхоперативную) память (рис. 9.14). Входы Di четырёх или восьми регистров, как правило, 4-разрядных, подключают к общей входной шине данных DIN. Вход загрузки требуемого регистра определяется дешифратором записи DCW в соответствии с поступившим на его вход адресом записи WA, т.е. кода номера загружаемого регистра. Запись данных, присутствующих на шине DIN, происходит в момент поступления сигнала разрешения записи WE. Выходырегистров с помощью мультиплексора MS подключаются к выходной шине DOUT.

Номер регистра, с которого происходит чтение, определяется посредством кода адреса чтения RA. Разрешение выдачи данных в шину DOUT происходит по сигналу RE. Поскольку дешифрация адреса записи и адреса чтения производится двумя независимыми узлами, имеющими автономные адресные входы WA и RA, в регистровую память можно одновременно записывать бинарное число в один из регистров и считывать число из другого. Описанная структура использована в кристаллах отечественных микросхем К155РП1, ИР11 и ИР12 серий К561 и К564.

Микросхемы регистровой памяти легко наращиваются по разрядности и допускают наращивание по числу регистров. Они разработаны для построения блоков регистров общего назначения (РОН), предназначенных для временного хранения исходных данных и промежуточных результатов вычислений сложения и умножения в микропроцессорах.

КОНТРОЛЬНЫЕ ВОПРОСЫ ПО ТЕМЕ 8