По типу используемых входов различают RS -, D -, T - и JK -триггеры, имеющие следующие обозначения управляющих входов:

R (Reset) – раздельный вход сброса RS -, D - и T -триггеров (Q = 0),

S (Set) – раздельный вход установки RS -, D - и T -триггеров (Q = 1),

K (Kill) – вход сброса JK -триггера (Q = 0),

J (Jump) – вход установки JK -триггера (Q = 1),

T (Toggle -переключать) – счетный вход Т -триггера,

D (Delay) – информационный вход переключения D -триггера в состояние, соответствующее логическому уровню на этом входес задержкой на время, определенное моментом появления сигнала С,

C (Clock) – управляющий или синхронизирующий вход триггеров.

По реакции на входной сигнал триггеры подразделяют на асинхронные и синхронные. Асинхронный триггер изменяет свое состояние непосредственно в момент изменения сигнала на его информационных входах, т.е. его реакция на изменение входного сигнала подобна реакции комбинационного элемента. Синхронный триггер изменяет свое состояние лишь в строго определенные (тактовые) моменты времени, соответствующие действию активного сигнала С на его входе синхронизации.

По виду активного логического сигнала, действующего на информационных входах, триггеры разделяют на статические – управляемые уровнем, и динамические – управляемые перепадом входного прямоугольного сигнала.Обычно в качестве динамического входа выступает вход С синхронизации триггера (при срабатывании по фронту сигнала, обозначаемое на рисунке условного изображения триггера, символомили наклоннойчертой, а при срабатывании по срезу – символом

По виду активного логического сигнала, действующего на информационных входах, триггеры разделяют на статические – управляемые уровнем, и динамические – управляемые перепадом входного прямоугольного сигнала.Обычно в качестве динамического входа выступает вход С синхронизации триггера (при срабатывании по фронту сигнала, обозначаемое на рисунке условного изображения триггера, символомили наклоннойчертой, а при срабатывании по срезу – символом

или наклонной чертой.

или наклонной чертой.

При этом сами входы могут быть прямыми или инверсными. Для переключения триггера необходиилимо подать на его активныйпрямой вход сигнал Х, а на активныйинверсный вход – сигнал Х.

9.3. RS -, D -, T -и JK -ТРИГГЕРЫ

9.3.1. RS -триггеры. Простейшим триггером является асинхронный RS -триггер (рис. 9.4 а). Принцип функционирования триггера, построенного на базисных логических элементах И-НЕ (рис. 9.4 б), поясняется таблицей истинности (табл. 9.3).

На рис. 9.4 в приведена временная диаграмма, иллюстрирующая его работу. В момент, когда устанавливается S = 1, триггер переходит в состояние Q = 1. При отсутствии входных сигналов состояние триггера не изменяется, а в момент установления R = 1 триггер переключается в состояние Q = 0, в котором пребывает до поступления нового сигнала 1 на S -вход.

Логическое выражение функционирования асинхронного RS -триггера c прямыми информационными входами:

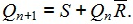

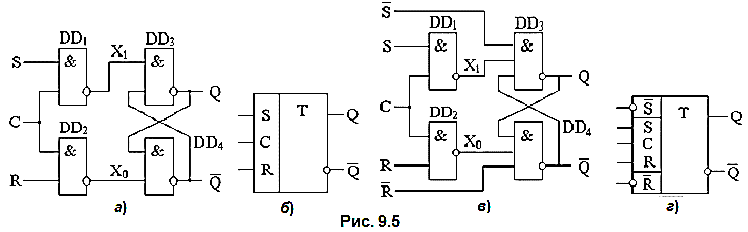

Асинхронный RS -триггер можно преобразовать в синхронный, дополнив его комбинационной схемой (рис. 9.5 а и б), разрешающей формирование активных уровней сигналов S и R ячейки памяти только при наличии дополнительного управляющего сигнала – сигнала синхронизации C, т.е. сигналы R и S должны быть связаны с сигналом C операцией И.

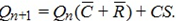

Вход С обеспечивает функционирование RS -триггера согласно выражению:

В момент подачисигнала С переключение синхронного RS -триггера в состояние Q = 1 происходит при S = 1, а при R = 1 - в состояние Q = 0. При С = 0 информация с S - и R -входов на триггер не передается.

Синхронный RS -триггер может быть дополнен асинхронными установочными входами S̅ и R̅, сигналы которых подаются непосредственно на его элемент памяти (рис. 9.5 в и г), и поэтому обладают более высоким приоритетом, чем сигналы синхронных входов. В схеме триггера синхронные и асинхронные входы управляются различными активными логическими уровнями: для синхронных входов активным является сигнал 1, для асинхронных – сигнал 0.

9.3.2. D -триггеры. Согласно определению, сигнал с информационного входа D должен переписыватьсяна выход триггера (Q = D) только по сигналу синхронизации С, поэтому D -триггер может быть только синхронным. Отсюда название входа D от слова delay– задержка сигнала D, определяемая моментом появления сигнала С.

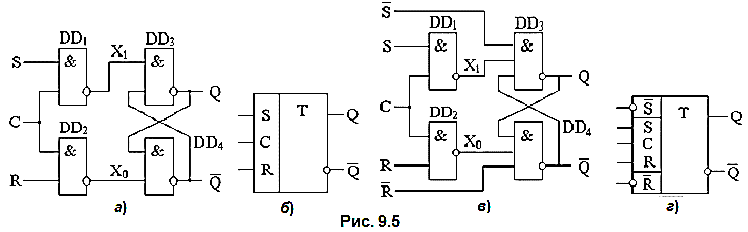

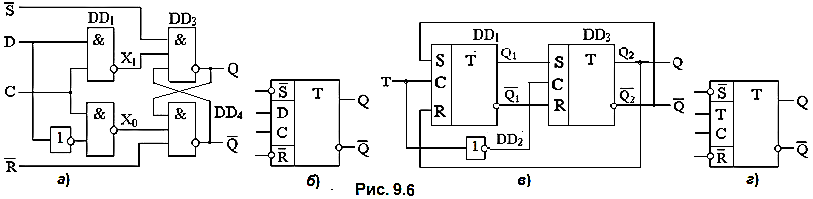

На рис. 9.6 а приведена логическая схема, а на рис.9.6 б условное графическое обозначение D -триггера.

Обычно синхронные триггеры снабжаются дополнительными асинхронными установочными входами S̅ и R̅, позволяющими воздействовать непосредственно на элемент памяти. Эти входы, как правило, инверсные по отношению к основным входам триггера и позволяют изменять состояние его элемента памяти в произвольные моменты времени.

9.3.3. Т -триггер. Т -триггер (toggle – переключать) – счетный триггер, который изменяет значение выходного сигнала при каждом появлении сигнала активного логического уровня на его информационном входе Т. Такую структуру можно получить из RS -триггера, если после каждого переключения инвертировать его сигналы на входах R и S. Однако использовать для этой цели выходные сигналы триггера невозможно, так как при этом нарушается основной принцип, позволяющий получить двузначность передаточной характеристики устройства.

Соединение входа S с выходом Q̅, а входа R с выходом Q фактически означает ввод в устройство цепи ООС. Поэтому при построении счетных триггеров широко применяется так называемая схема двухступенчатого (flip-flop или MS-master-slave) MS -триггера (рис. 9.6 в).

Допустим, что триггер установлен (Q = 1). При активном логическом уровне на входе Т (Т = 1) первый триггер DD1 сбрасывается (так как S = 0 и R = 1), формируя на своих выводах Q 1 = 0 и Q̅ = 1. Эти сигналы поступают на информационные входы второго триггера DD3. Однако, так как его сигнал T̅ пассивен, выходные сигналы не изменяются (триггер DD 3 по-прежнему установлен и Q 2 = Q = 1).

Изменение уровня сигнала на информационном входе Т (Т = 0)под воздействием выходных сигналов триггера DD1 вызывает переключение триггера DD3. На выходе Т - триггера установятся сигналы Q 2 = Q = 0 и Q̅ 2 = Q̅ = 1. Эти сигналы подаются на информационные входы первого DD1 триггера (S = 1 и R = 0), готовя его к следующему переключению.

Т -триггер может быть как асинхронным, так и синхронным. Условное графическое обозначение синхронного Т -триггера, снабженного дополнительными асинхронными установочными входами, показано на рис. 9.6 г.

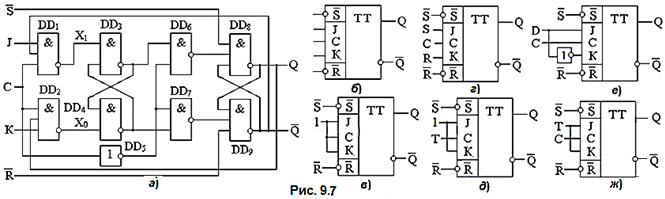

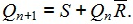

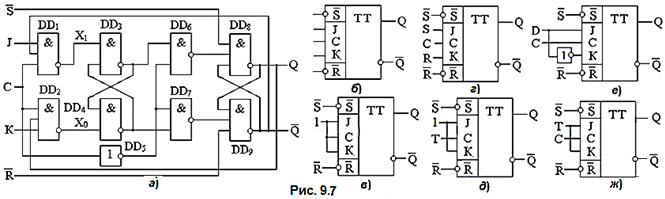

9.3.4. JK - триггер. Универсальный JK -триггер (рис. 9.7 а и рис. 9.7 б) как правило строится на основе двухступенчатой структуры.

От T -триггера его отличает наличие двух дополнительных входов J и K, управляющих элементами И-НЕ комбинационной схемы триггера первой ступени (DD1 и DD2, рис. 9.7 а).

В отличие от RS -триггера одновременная подача на входы J и K сигналов с активными логическими уровнями не является для JK -триггера запретной комбинацией: например, при J = K = 1, которые пассивны для элементов И-НЕ, триггерфункционирует в счетном режиме, т.е. переключается каждым тактовым импульсом на С -входе. Если J = 1, то независимо от значения К и предыдущего состояния триггера он установится (Q = 1). При К = 1 вне зависимости от сигнала на входе J и предыдущего состояния триггера, он сбросится (Q = 0).

Заметим, что для расширения функциональных возможностей у реальных JK - триггеров может быть по несколько входов J и К, объединенных операцией И.

Универсальность JK -триггера подтверждаетсятем, что с его помощью можно реализовать алгоритмы работы триггеров всех рассмотренных типов. Сказанное иллюстрируется рис. 9.7, на котором изображены: б – синхронный JK -триггер, в – асинхронный RS - триггер, г – синхронный RS -триггер, д –асинхронный Т -триггер, е – D -триггер, ж – синхронный Т -триггер.

СЧЕТЧИКИ

9.4.1. Классификация счетчиков. Счетчик – последовательностное логическое устройство, предназначенное для счета поступающих на его вход импульсов, в интервале между которыми он должен хранить информацию об их количестве в некотором двоичном коде. Счетчики строятся на основе нескольких однотипных связанных между собой разрядных схем, каждая из которых, в общем случае, состоит из триггера обычно D - или JK -типа и некоторой комбинационной схемы, предназначенной для формирования информационных сигналов триггеров.

В цифровых схемах счетчики могут выполнять следующие микрооперации над кодовыми словами:

· установка в исходное состояние (запись нулевого кода),

· запись входной информации в параллельной форме,

· хранение и выдача информации,

· инкремент – увеличение хранящегося кодового слова на единицу,

· декремент – уменьшение хранящегося кодового слова на единицу.

Счетчики принято классифицировать по модулю счета М (М – максимальное число импульсов, после прихода которых счетчик устанавливается в исходное состояние), по направлению счета и методу организации межразрядныхсвязей.

По модулю счета различают двоичные (М = 2 n, где n – число разрядов счетчика), и двоично-кодированные (М < 2 n) счетчики (например, десятичные с коэффициентом K сч = 10 или делители частоты с коэффициентом деления K сч ≠ 2 п).

Максимальное число N, которое может быть записано в счётчике, равно 2 п – 1.

По виду активного логического сигнала, действующего на информационных входах, триггеры разделяют на статические – управляемые уровнем, и динамические – управляемые перепадом входного прямоугольного сигнала.Обычно в качестве динамического входа выступает вход С синхронизации триггера (при срабатывании по фронту сигнала, обозначаемое на рисунке условного изображения триггера, символомили наклоннойчертой, а при срабатывании по срезу – символом

По виду активного логического сигнала, действующего на информационных входах, триггеры разделяют на статические – управляемые уровнем, и динамические – управляемые перепадом входного прямоугольного сигнала.Обычно в качестве динамического входа выступает вход С синхронизации триггера (при срабатывании по фронту сигнала, обозначаемое на рисунке условного изображения триггера, символомили наклоннойчертой, а при срабатывании по срезу – символом или наклонной чертой.

или наклонной чертой.