Мультиплексор – коммутатор цифровых сигналов. Мультиплексором (MS) называется комбинационное устройство, предназначенное для коммутации в желаемом порядке сигналов с нескольких входных шин на одну выходную.

Входы мультиплексора делятся на информационные, адресные и разрешающие (рис. 7.6). На первые подается информация, подлежащая передаче на выход Y. Адресные входы A1– А3 определяют активный информационный вход D n. На разрешающий вход E подается сигнал, разрешающий передачу информации с активного входа на выход. Наличие разрешающего входа Е позволяет синхронизировать работу мультиплексора с работой других устройств, а также наращивать его разрядность. Если число адресных входов равно n, то мультиплексор может коммутировать на выход 2 n входных сигналов.

Рис. 7.6

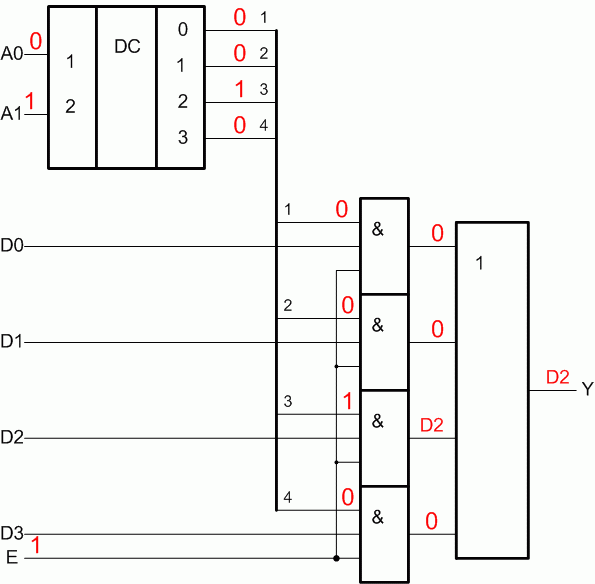

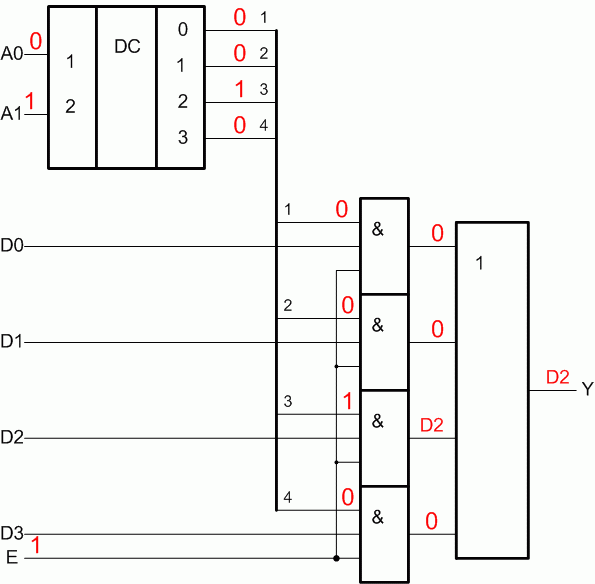

Пример структуры мультиплексора с четырьмя информационными входами (4x1) приведен ниже на рис. 7.7. Мультиплексор состоит из дешифратора (2х4), 4 схем совпадения 3И, каждая из которых имеет один адресный, один информационный и один стробирующий вход, а также одной схемы ИЛИ с 4 входами. Ее выход является выходом Y мультиплексора.

Рис. 7.7

Шифратором (кодером) называется комбинационное устройство, выполняющее функцию, обратную функции дешифраторов, т. е. преобразующее унитарный код, подаваемый на входные шины, в соответствующий код на выходах. Классический шифратор имеет m входов и n выходов, и при подаче сигналов на один из входов (обязательно на один и не более) на выходе шифратора появляется двоичный код номера возбужденного выхода. Число входов и выходов такого шифратора связано соотношением m = 2 n.

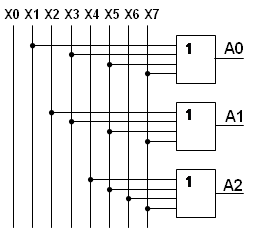

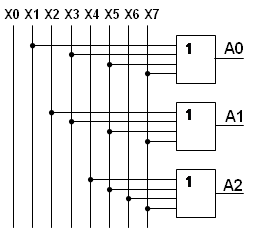

Рассмотрим структуру такого шифратора рис. 7.8. Для построения шифратора можно использовать схемы ИЛИ – по одной на каждый выход. При этом схема разбивается на n простых фрагментов. К входу элементов ИЛИ каждого выходного разряда должны быть подключены те входы шифратора, в двоичном представлении номера которых есть единица в данном разряде. Например, ко входам А0 надо подключить все нечетные входы (1, 3, 5, 7).

Рис. 7.8

Есть также различные шифраторы, преобразующие один вид кода в другой: декадный, двоично-десятичный, преобразователи для кода Грея, кода Айкена, коды для различных типов индикаторов и т.д.

Например, декадный шифратор имеет 10 входов и 4 выхода. Шифратор предназначен для преобразования десятичных чисел от 0 до 9 в двоичный код. Декадный шифратор является неполным, так как 2 n ≠ m.

Приоритетный шифратор формирует в двоичном коде номер самого старшего из всех, возбужденных одновременно входов. Приоритетный шифратор отличается от шифратора наличием дополнительной логической схемы выделения активного уровня старшего возбужденного входа. Уровни сигналов на остальных входах схемой игнорируются. Он является основным элементом параллельного АЦП и устройств сбора информации.

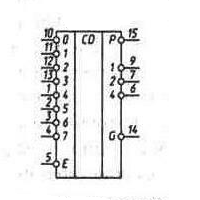

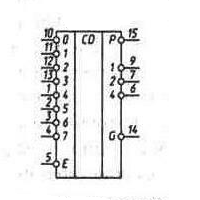

На рис. 7.9 приведено условное графическое изображение (УГО) приоритетного шифратора – микросхемы ИВ3. Она имеет восемь информационных входов 0–7 и вход разрешения Е. Выходов у ИВ3пять: три для выходного кода (1, 2, 4); G – признака наличия входного сигнала и Р – выход переноса-расширения. Входы и выходы – инверсные, т.е. активный сигнал «0».

Если на всех информационных входах микросхемы «1», на выходах 1,2,4, G – «1», на выходе Р – «0». При подаче «0» на любой из информационных входов 0–7 на выходах 1, 2, 4 появится инверсный код, соответствующий номеру входа, на который подан «0», на выходе G – «0», что является признаком наличия входного сигнала, на выходе Р – «1», которая запрещает работу других микросхем ИВ3 при их каскадном соединении. Если «0» будет подан на несколько информационных входов микросхемы, выходной код будет соответствовать входу с большим номером.

Так работает микросхема при подаче на вход Е «0». Если же на вход Е подать «1» (запрет работы), на всех шести выходах микросхемы будет «1». Микросхемы ИВ3 можно последовательно соединять для получения большего числа входов.

Рис. 7. 9

Последовательностные схемы,