Кормораздатчик мобильный электрифицированный: схема и процесс работы устройства...

Организация стока поверхностных вод: Наибольшее количество влаги на земном шаре испаряется с поверхности морей и океанов (88‰)...

Кормораздатчик мобильный электрифицированный: схема и процесс работы устройства...

Организация стока поверхностных вод: Наибольшее количество влаги на земном шаре испаряется с поверхности морей и океанов (88‰)...

Топ:

Марксистская теория происхождения государства: По мнению Маркса и Энгельса, в основе развития общества, происходящих в нем изменений лежит...

Когда производится ограждение поезда, остановившегося на перегоне: Во всех случаях немедленно должно быть ограждено место препятствия для движения поездов на смежном пути двухпутного...

Определение места расположения распределительного центра: Фирма реализует продукцию на рынках сбыта и имеет постоянных поставщиков в разных регионах. Увеличение объема продаж...

Интересное:

Как мы говорим и как мы слушаем: общение можно сравнить с огромным зонтиком, под которым скрыто все...

Финансовый рынок и его значение в управлении денежными потоками на современном этапе: любому предприятию для расширения производства и увеличения прибыли нужны...

Берегоукрепление оползневых склонов: На прибрежных склонах основной причиной развития оползневых процессов является подмыв водами рек естественных склонов...

Дисциплины:

|

из

5.00

|

Заказать работу |

|

|

|

|

Цифровые сигналы, логические функции и элементы

Цифровые устройства (ЦУ) являются составной частью современных радиоэлектронных систем и предназначены для обработки, хранения и передачи дискретной (цифровой) информации.

В отличие от аналоговых электронных устройств, в цифровых устройствах входные и выходные сигналы могут принимать ограниченное количество состояний. В цифровых устройствах входные и выходные сигналы могут принимать два состояния: «логическая 1» и «логический 0». Теоретической основой проектирования ЦУ является алгебра логики или булева алгебра, оперирующая логическими переменными. Логические функции (ЛФ) логических переменных (ЛП) также могут иметь только два значения: «логическая 1» и «логический 0»".

В соответствии с логическим соглашением (ГОСТ 2.743-82), более положительному значению физической величины, "H" - уровень, соответствует состояние "логическая 1", а менее положительному значению,"L - уровень" - "логический 0". Такое соглашение называется положительной логикой. Обратное соотношение называется отрицательной логикой.

Для n логических переменных существует 2n их комбинаций или двоичных наборов. На каждом таком наборе может быть определено значение функции "логический 0". или "логическая 1", Общее число ЛФ от n аргументов равно:

Для n=1, N=4, а для n=2, N=16. При n=3, N=256 и далее очень быстро растет. Практическое значение имеют: функция НЕ от 1-й переменной и несколько функций от 2-х переменных, т.к. любое сложное выражение можно рассматривать как композицию из простейших. Набор простейших ЛФ, позволяющих реализовать любую другую функцию называется логическим базисом (ЛБ). Базис образуют функции И, ИЛИ, НЕ; минимальным ЛБ является каждая из функций ИЛИ-НЕ или И-НЕ.

|

|

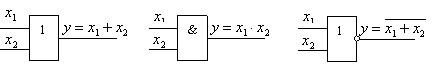

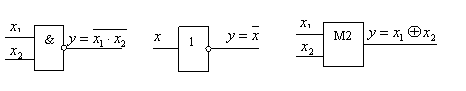

ЛФ могут иметь различные формы представления: 1) словесное, 2) алгебраическое, 3) табличное, 4) на алгоритмическом языке (HDL) и 5) схемное. Табличное представление значений ЛФ для всех наборов входных переменных называется таблицей истинности. Ниже представлены основные ЛФ в алгебраической и табличной формах и их обозначение на схемах (рис. 7.1).

Основные ЛФ в алгебраической форме:

Функция НЕ: Y = X; Y = NOT X.

Функция И: Y = X1 Ù X2; Y = X1& X2,;Y = X1×X2; Y = X1 AND X2.

Функция ИЛИ: Y = X1Ú X2; Y = X1+ X2; Y = X1 OR X2.

Функция исключающее ИЛИ: Y = X1Å X2; Y = X1 XOR X2.

Функция И-НЕ: Y = (X1 Ù X2)|; Y = X1 | X2Y = X1 NAND X2.

Функция ИЛИ-НЕ: Y = ((X1Ú X2); Y = X1↓ X2; Y = X1 NOR X2.

Основные ЛФ в табличной форме:

| X1 | X2 | NOT X1 | X1 AND X2 | X1 OR X2 | X1 XOR X2 | X1 NAND X2 | X1 NOR X2 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 |

ИЛИ И ИЛИ-НЕ

И-НЕ НЕ Исключающее ИЛИ

Рис. 7.1

Последовательностные схемы,

Регистры

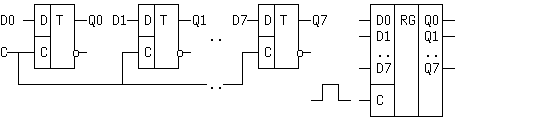

Регистры – это устройства, предназначенные для хранения и преобразования многоразрядных двоичных чисел. Запоминающими элементами регистра являются триггеры, число которых равно разрядности хранимых чисел. Различают параллельные регистры (регистры памяти), последовательные регистры (регистры сдвига), параллельно-последовательные регистры, преобразующие код из параллельного в последовательный и наоборот (например, ввод в параллельном коде, вывод – в последовательном).

В регистрах памяти число вводится (выводится) за один такт, а в регистрах сдвига – за n тактов, где n – разрядность регистра. В регистрах памяти могут использоваться триггеры как со статическим, так и с динамическим управлением. На рис. 7.27 приведена схема 8-разрядного регистра памяти с общим входом управления записью информацией и УГО этого регистра. Высокий уровень на входе C разрешает передачу информации с входов данных на выходы (Qi = Di), а низкий уровень на входе C защелкивает данные.

|

|

Рис. 7.27

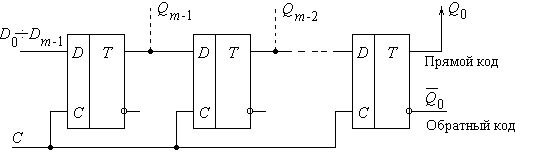

Регистры сдвига применяются для преобразования последовательного кода в параллельный (и обратно), для умножения и деления многоразрядных чисел и т.д. Сдвиговые регистры обычно реализуются на динамических D-триггерах. В регистре с последовательным вводом производится последовательный сдвиг поступающей на вход информации на один разряд вправо в каждом такте синхросигналов (рис. 7.28).

Рис. 7.28

После поступления m синхроимпульсов весь регистр оказывается заполненным разрядами числа D, и первый разряд числа (D0) появляется на выходе Q0 регистра. В течение последующих m синхроимпульсов производится последовательный поразрядный вывод из регистра записанного числа, после чего регистр оказывается полностью очищенным.

Для построения реверсивного сдвигового регистра необходимо между его триггерами включать устройства управления направлением сдвига (мультиплексоры), аналогично реверсивному счетчику. Эти устройства в зависимости от направления сдвига должны подключать входы каждого триггера регистра к выходам предыдущего или к выходам последующего триггеров.

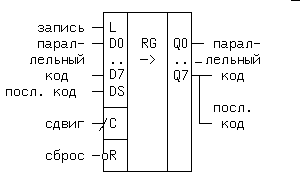

Универсальный сдвиговый регистр с последовательно-параллельным вводом и параллельным выводом информации имеет следующие входы и выходы (рис. 7.29):

· входы параллельной записи Di,

· общий вход разрешения записи L,

· тактовый вход С,

· общий асинхронный вход сброса ~R всех триггеров,

· выходы параллельного кода Qi,

· выход последовательного кода Q7.

Рис. 7.29

Регистр сдвига с параллельной загрузкой кода это основной узел всех последовательных интерфейсов. Работа такого интерфейса заключается в преобразовании параллельного кода в последовательный, передаче этого кода по однопроводной линии связи и обратном преобразовании последовательного кода в параллельный.

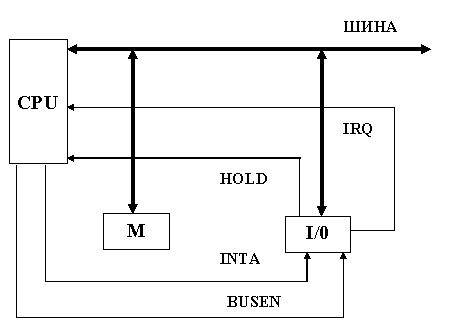

Работа МПС и сигналы шины

Существует три основных типа обмена между модулями, которые различаются инициатором обмена, временной привязкой к исполнению основной программы и устройством, управляющим шиной (рис. 33):

1. программный обмен по инициативе МП,

2. обмен по прерыванию,

3. внепроцессорный обмен между памятью и внешним устройством.

Программный обмен является основным в любой МПС. Все операции (циклы) обмена информацией в данном случае инициируются только процессором, все они выполняются строго в порядке, предписанном исполняемой программой.

|

|

Процессор читает (выбирает) из памяти коды команд и исполняет их, читая данные из памяти или из устройстваввода/вывода, обрабатывая их, записывая данные в память или передавая их в устройство ввода/вывода. Все сигналы на магистрали в данном случае контролируются процессором.

Обмен по прерываниям используется тогда, когда необходима быстрая реакция микропроцессорнойсистемы на приход внешнего сигнала. Процессор прерывает основную (фоновую) программу при поступлении в случайный момент времени сигнала (запроса – IRQ) от внешнего устройства, определяет источник прерывания и выполняет обработку прерывания (исполняет подпрограмму, предназначенную для обслуживания именно этого события). Закончив обработку прерывания, МП продолжает исполнение к прерванной программы с той точки, где его прервали. Если одновременно прерывание запрашивают несколько устройств, то только одному МП посылает сигнал разрешения INTA.

Кроме сигналов запроса прерывания, здесь также все сигналы на магистрали выставляются МП, то есть он, полностью контролирует магистраль.

Прямой доступ к памяти (DMA) используется для быстрой пересылки массива информации из устройства ввода/вывода в память или из памяти в устройство ввода/вывода. Процессор в обмене не участвует, а контроль над системной магистралью осуществляет дополнительное устройство (контроллер DMA).

Аналогично запросу на прерывание внешнее устройство подает процессору сигнал HOLD – запрос режима DMA. В ответ на это МП заканчивает выполнение текущей команды, отключается от всех шин и посылает сигнал BUSEN запросившему устройству, что можно начинать работу в режиме DMA. Когда пересылка информации будет закончена, процессор вновь возвращается к прерванной программе, продолжая ее с той точки, где его прервали.

Рис. 7.32

Каждая команда МП состоит из одного или более типовых циклов обращения (пересылок) к системной магистрали. За один машинный цикл между CPU, памятью и подсистемой I/O передается одно слово, или байт. Существует несколько типовых машинных циклов: чтение памяти, запись в память, чтение порта I/O, запись в порт I/O,. цикл обслуживания прерывания, цикл DMA и т.д.

|

|

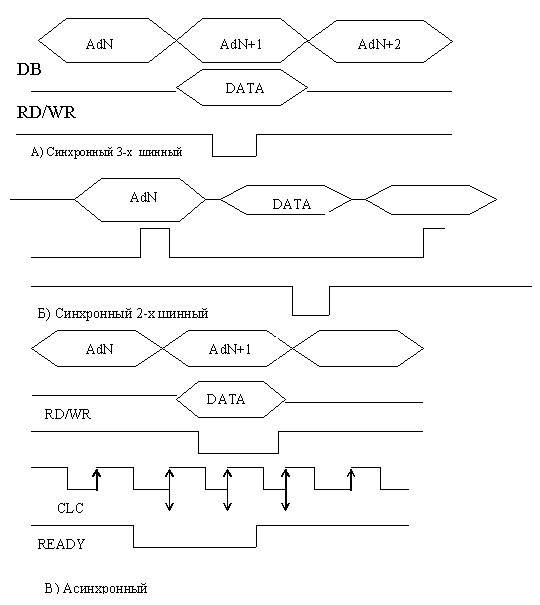

В свою очередь каждый машинный цикл (МЦ) состоит из нескольких машинный тактов (T1, T2, и т.д.), и каждый сигнал управления привязан к определенному такту.

На рис. 7.33 приведены диаграммы, иллюстрирующие работу МПС при различных режимах обмена.

| В) Асинхронный |

| A) Синхронный 3-х шинный |

| Б) Синхронный 2-х шинный |

Рис. 7.33

Для обеспечения типовых МЦ в состав шины управления должен входить минимальный набор сигналов:

сигналы чтения и записи в память – RD и WR,

сигналы чтения и записи в порт – IOR и IOW,

сигналы системы прерывания – IRQ, INTA,

сигналы прямого доступа к памяти – HOLD, HLDA,

сигналы для асинхронного обмена и сброса –.READY и RST.

Структура и параметры

Аналого-цифровые преобразователи (АЦП) предназначены для преобразования аналоговых (непрерывных) сигналов в цифровую форму. АЦП могут быть периферийными устройствами, которые подключаются к МПС либо через порты, либо через стандартные интерфейсы, также АЦП могут быть встроенными узлами микроконтроллеров. Преобразование аналогового сигнала в цифровой происходит в определенные моменты времени, которые называются точками отсчета. Количество отсчетов в единицу времени называется частотой дискретизации (преобразования) FD, которая, в свою очередь, определяется быстродействием и условиями использования АЦП.

Основные параметры АЦП

Разрядность n выходного кода для АЦП характеризует количество разрядов для отображения аналоговой преобразуемой величины. Эта характеристика определяет количество квантованных уровней (Nmax=2n).

Разрешающая способность (чувствительность) – значение минимального изменения входного сигнала АЦП, которое вызывает изменение цифрового кода на единицу. Эта характеристика определяется величиной кванта h и называется еще величиной младшего разряда (LSB в англоязычной терминологии).

Диапазон входного напряжения АЦП Umax зависит от величины опорногоUref(Umax = Uref–h).

Время преобразования tСдля АЦП характеризует временной интервал с момента подачи управляющего сигнала «начало преобразования» и до момента получения на выходе адекватного цифрового кода. Изменение входного аналогового сигнала в период времени tС нежелательно, поскольку это изменение вносит неопределенность в генерируемый выходной код.

Максимальная частота преобразования FDMAX определяет максимальное значение числа отсчетов входного сигнала, выполняемых преобразователем в единицу времени. В соответствии с теоремой Котельникова–Шеннона точное восстановление сигнала возможно, только если частота дискретизации выше, чем удвоенная максимальная частота в спектре сигнала.

|

|

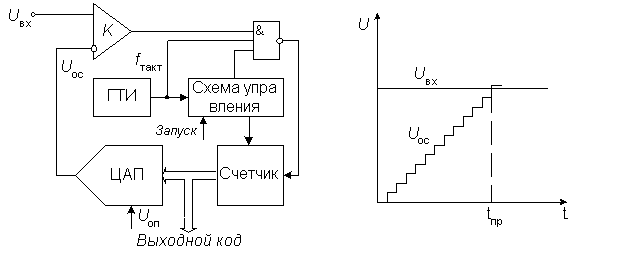

АЦП последовательного счета. Этот преобразователь является типичным примером последовательного АЦП с единичными приближениями и состоит из компаратора, счетчика и ЦАП. На один вход компаратора поступает входной сигнал, а на другой – сигнал обратной связи с ЦАП (рис. 7.39).

Рис. 7.39

Работа преобразователя начинается с прихода импульса запуска, который включает счетчик, суммирующий число импульсов, поступающих от генератора тактовых импульсов ГТИ. Выходной код счетчика подается на ЦАП, осуществляющий его преобразование в напряжение обратной связи Uос. Процесс преобразования продолжается до тех пор, пока напряжение обратной связи не сравняется с входным напряжением и не переключится компаратор, который запретит поступление тактовых импульсов на счетчик. Переключение компаратора из «1» в «0» в момент времени tпр означает завершение процесса преобразования. После этого с выхода счетчика можно считать выходной код АЦП, который будет пропорционален входному напряжению во время преобразования.

Время преобразования АЦП этого типа tпр является переменным и зависит от величины входного напряжения. Его максимальное значение соответствует максимальному входному напряжению и при разрядности двоичного счетчика N и частоте тактовых импульсов fт равно:

t пр.макс = (2N – 1)/ f т ~ 2N /f т.

Особенностью АЦП данного класса является небольшая частота дискретизации, достигающая нескольких килогерц, сравнительная простота построения и дешевизна.

Цифровые сигналы, логические функции и элементы

Цифровые устройства (ЦУ) являются составной частью современных радиоэлектронных систем и предназначены для обработки, хранения и передачи дискретной (цифровой) информации.

В отличие от аналоговых электронных устройств, в цифровых устройствах входные и выходные сигналы могут принимать ограниченное количество состояний. В цифровых устройствах входные и выходные сигналы могут принимать два состояния: «логическая 1» и «логический 0». Теоретической основой проектирования ЦУ является алгебра логики или булева алгебра, оперирующая логическими переменными. Логические функции (ЛФ) логических переменных (ЛП) также могут иметь только два значения: «логическая 1» и «логический 0»".

В соответствии с логическим соглашением (ГОСТ 2.743-82), более положительному значению физической величины, "H" - уровень, соответствует состояние "логическая 1", а менее положительному значению,"L - уровень" - "логический 0". Такое соглашение называется положительной логикой. Обратное соотношение называется отрицательной логикой.

Для n логических переменных существует 2n их комбинаций или двоичных наборов. На каждом таком наборе может быть определено значение функции "логический 0". или "логическая 1", Общее число ЛФ от n аргументов равно:

Для n=1, N=4, а для n=2, N=16. При n=3, N=256 и далее очень быстро растет. Практическое значение имеют: функция НЕ от 1-й переменной и несколько функций от 2-х переменных, т.к. любое сложное выражение можно рассматривать как композицию из простейших. Набор простейших ЛФ, позволяющих реализовать любую другую функцию называется логическим базисом (ЛБ). Базис образуют функции И, ИЛИ, НЕ; минимальным ЛБ является каждая из функций ИЛИ-НЕ или И-НЕ.

ЛФ могут иметь различные формы представления: 1) словесное, 2) алгебраическое, 3) табличное, 4) на алгоритмическом языке (HDL) и 5) схемное. Табличное представление значений ЛФ для всех наборов входных переменных называется таблицей истинности. Ниже представлены основные ЛФ в алгебраической и табличной формах и их обозначение на схемах (рис. 7.1).

|

|

|

Историки об Елизавете Петровне: Елизавета попала между двумя встречными культурными течениями, воспитывалась среди новых европейских веяний и преданий...

Индивидуальные и групповые автопоилки: для животных. Схемы и конструкции...

Двойное оплодотворение у цветковых растений: Оплодотворение - это процесс слияния мужской и женской половых клеток с образованием зиготы...

Наброски и зарисовки растений, плодов, цветов: Освоить конструктивное построение структуры дерева через зарисовки отдельных деревьев, группы деревьев...

© cyberpedia.su 2017-2024 - Не является автором материалов. Исключительное право сохранено за автором текста.

Если вы не хотите, чтобы данный материал был у нас на сайте, перейдите по ссылке: Нарушение авторских прав. Мы поможем в написании вашей работы!