Кормораздатчик мобильный электрифицированный: схема и процесс работы устройства...

Автоматическое растормаживание колес: Тормозные устройства колес предназначены для уменьшения длины пробега и улучшения маневрирования ВС при...

Кормораздатчик мобильный электрифицированный: схема и процесс работы устройства...

Автоматическое растормаживание колес: Тормозные устройства колес предназначены для уменьшения длины пробега и улучшения маневрирования ВС при...

Топ:

Эволюция кровеносной системы позвоночных животных: Биологическая эволюция – необратимый процесс исторического развития живой природы...

Установка замедленного коксования: Чем выше температура и ниже давление, тем место разрыва углеродной цепи всё больше смещается к её концу и значительно возрастает...

Интересное:

Подходы к решению темы фильма: Существует три основных типа исторического фильма, имеющих между собой много общего...

Уполаживание и террасирование склонов: Если глубина оврага более 5 м необходимо устройство берм. Варианты использования оврагов для градостроительных целей...

Мероприятия для защиты от морозного пучения грунтов: Инженерная защита от морозного (криогенного) пучения грунтов необходима для легких малоэтажных зданий и других сооружений...

Дисциплины:

|

из

5.00

|

Заказать работу |

Архитектура микропроцессора - это его логическая организация, рассматриваемая с точки зрения пользователя; она определяет возможности микропроцессора по аппаратной и программной реализации функций, необходимых для построения микропроцессорной системы. Понятие архитектуры микропроцессора отражает:

- его структуру, т.е. совокупность компонентов, составляющих микропроцессор, и связей между ними; для пользователя достаточно ограничиться регистровой моделью микропроцессора;

- способы представления и форматы данных;

- способы обращения ко всем программно-доступным для пользователя элементам структуры (адресация к регистрам, ячейкам постоянной и оперативной памяти, внешним устройствам);

- набор операций, выполняемых микропроцессором;

- характеристики управляющих слов и сигналов, вырабатываемых микропроцессором и поступающих в него извне;

- реакцию на внешние сигналы (система обработки прерываний и т.п.).

По способу организации пространства памяти микропроцессорной системы различают два основных типа архитектур.

Организация, при которой для хранения программ и данных используется одно пространство памяти, называется фон Неймановской архитектурой (по имени математика, предложившего кодирование программ в формате, соответствующем формату данных). Программы и данные хранятся в едином пространстве, и нет никаких признаков, указывающих на тип информации в ячейке памяти. Преимуществами такой архитектуры являются более простая внутренняя структура микропроцессора и меньшее количество управляющих сигналов.

Организация, при которой для хранения программ и данных используется одно пространство памяти, называется фон Неймановской архитектурой (по имени математика, предложившего кодирование программ в формате, соответствующем формату данных). Программы и данные хранятся в едином пространстве, и нет никаких признаков, указывающих на тип информации в ячейке памяти. Преимуществами такой архитектуры являются более простая внутренняя структура микропроцессора и меньшее количество управляющих сигналов.

Организация, при которой память программ CSEG (Code Segment) и память данных DSEG (Data Segment) разделены и имеют свои собственные адресные пространства и способы доступа к ним, называется Гарвардской архитектурой (по имени лаборатории Гарвардского Университета, предложившей ее). Такая архитектура является более сложной и требует дополнительных управляющих сигналов. Однако, она позволяет осуществлять более гибкие манипуляции информации, реализовывать компактно кодируемый набор машинных команд и, в ряде случаев, ускорять работу микропроцессора. Представителями такой архитектуры являются микроконтроллеры семейства MCS-51 фирмы Intel.

В настоящее время выпускаются микропроцессоры со смешанной архитектурой, в которых CSEG и DSEG имеют единое адресное пространство, однако различные механизмы доступа к ним. Конкретным примером являются микропроцессоры семейства 80х86 фирмы Intel.

МП-системы с трехшинной и двухшинной системной магистралью. Примеры реализации.

На физическом уровне микропроцессор взаимодействует с памятью и системой ввода-вывода через единый набор системных шин - внутрисистемную магистраль. Она, в общем случае состоит из:

- шины данных DB (Data Bus), по которой производится обмен данными между ЦП, памятью и системой ВВ;

- шины адреса AB (Address Bus), используемой для передачи адресов ячеек памяти и портов ВВ, к которым осуществляется обращение;

- шины управления CB (Control Bus), по которой передаются управляющие сигналы, реализующие циклы обмена информацией и управляющие работой системы.

- шины управления CB (Control Bus), по которой передаются управляющие сигналы, реализующие циклы обмена информацией и управляющие работой системы.

Этот же набор шин применяется для организации канала ПДП. Магистраль такого типа носит название демультиплексной или трехшинной с раздельными шинами адреса и данных.

Этот же набор шин применяется для организации канала ПДП. Магистраль такого типа носит название демультиплексной или трехшинной с раздельными шинами адреса и данных.

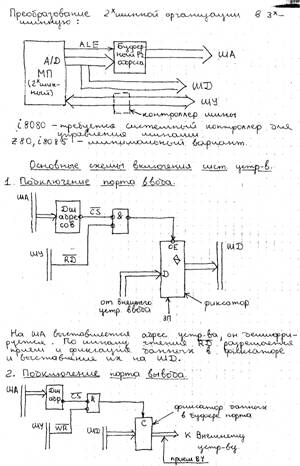

В некоторых микропроцессорах с целью сокращения ширины физической магистрали вводят совмещенную шину адреса-данных AD (Address/Data Bus), по которой передаются как адреса так и данные. Этап передачи адресной информации отделен по времени от этапа передачи данных и стробируется специальным сигналом ALE (Address Latch Enable), который включен в состав CB. Данную магистраль обычно называют мультиплексной или двухшинной с совмещенными шинами адреса и данных.

Физический обмен данными через магистраль выполняется словами или байтами в виде следующих друг за другом обращений к каналу. За один цикл обращения к магистрали между ЦП, памятью и системой ВВ передается одно слово или байт.

5.

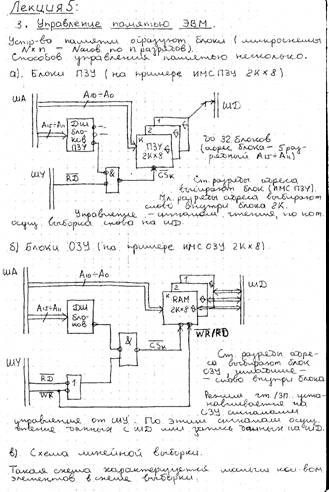

Основные способы построения схем выборки устройств микропроцессорной системы.

Основные способы построения схем выборки устройств микропроцессорной системы.

История развития пистолетов-пулеметов: Предпосылкой для возникновения пистолетов-пулеметов послужила давняя тенденция тяготения винтовок...

Организация стока поверхностных вод: Наибольшее количество влаги на земном шаре испаряется с поверхности морей и океанов (88‰)...

Наброски и зарисовки растений, плодов, цветов: Освоить конструктивное построение структуры дерева через зарисовки отдельных деревьев, группы деревьев...

Эмиссия газов от очистных сооружений канализации: В последние годы внимание мирового сообщества сосредоточено на экологических проблемах...

© cyberpedia.su 2017-2024 - Не является автором материалов. Исключительное право сохранено за автором текста.

Если вы не хотите, чтобы данный материал был у нас на сайте, перейдите по ссылке: Нарушение авторских прав. Мы поможем в написании вашей работы!