Элемент – простейшая часть компьютера, выполняет операции над двоичными цифрами (битами). Основные элементы – это ЛЭ, элементы памяти и вспомогательные элементы.

Логические элементы выполняют бинарные операции И, ИЛИ, НЕ, И-НЕ и др., на основе которых производятся практически все преобразования информации в ПК.

Элементы памяти – это триггеры различных типов: RS, JK, D илиT, служат для хранения данных.

Вспомогательные элементы – это усилители и формирователи различных сигналов.

Узел(блок) – состоит из элементов и выполняет операции над байтами и словами. Типовые узлы: регистры, счётчики, сумматоры, дешифраторы, селекторы, мультиплексоры и др. несколько узлов могут объединяться в блоки, напр., сумматор = сумматор + его регистр.

Устройство - строится из элементов и узлов для выполнения однотипных операций.к ним относятся: ЗУ, АЛУ, центральное УУ (ЦУУ), УВВ. Устройства могут объединяться в один конструктивный блок, напр., системный блок = УУ + АЛУ + ЗУ.

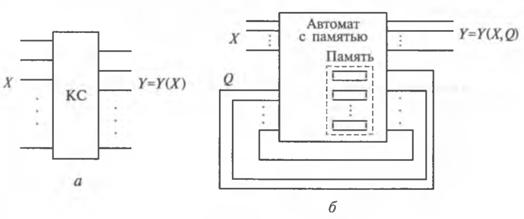

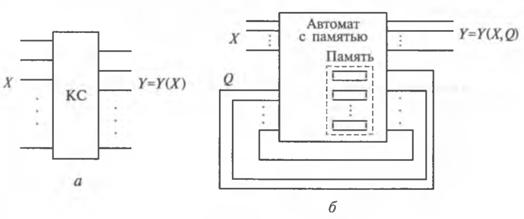

Рассмотрим более подробно узлы. Узлы м.б. комбинационного типа – состоят из комбинационных схем (КС) и накапливающего типа – автоматы с памятью, последовательные схемы.

Узлы комбинационного типа (рис. 1а) состоят из ЛЭ, они не сохраняют данные, выходной сигнал Y зависит только от комбинации входных сигналов Х в данный момент. КС выполняет перекодировку входных сигналов в выходные.

!!Все основные преобразования в компьютере выполняются с помощью КС!!

Рисунок 1 а- комбинационная схема, б -автомат с памятью

Автоматы с памятью состоят из ЛЭ и элементов памяти – рис. 1б. Информация, записанная в памяти автомата, называется состоянием автомата (Q). Выходной сигнал зависит от входного Х и состояния Q, поэтому он может быть различным при одинаковых Х. Кроме того, в памяти автомата накапливается информация о всех входных сигналах, поэтому автомат может выполнять не только отдельные операции, но и их последовательности, т.е. алгоритмы операций. Сам ПК – это сложный автомат с памятью большой ёмкости.

Элементы памяти м.б. статическими (хранят информацию постоянно), используются в схемах процессора, и динамическими (требуют периодической регенерации данных), используются в ЗУ.

Статические элементы строятся на триггерах.

Триггером называется электронная схема, которая может находиться в одном из двух устойчивых состояний - логического “0” или логической “1”. Наименование триггера происходит от английского слова “trigger” - защёлка, в цифровой технике по-английски он называется “flip-flop”.

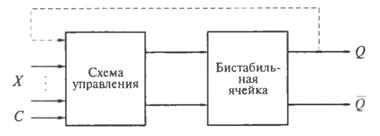

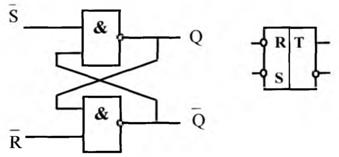

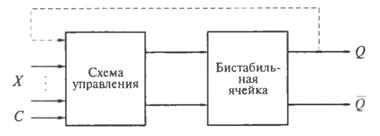

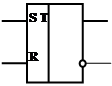

Триггер состоит из бистабильной ячейки и схемы управления - рис. 2

Рисунок 2 – Общая структура триггера

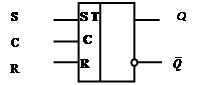

Бистабильная ячейка выполняется на ЛЭ типа И-НЕ или ИЛИ-НЕ (рис. 3).

Рисунок 3 – Бистабильная ячейка:

а – на элемента ИЛИ-НЕ,

б – на элементах И-НЕ

Принцип действия: Если на верхнем выходе (ЛЭ1) была "1", а на оба входа подать "0", то "1" с выхода ЛЭ1 поступает на вход ЛЭ2, комбинация "0" и "1"на входе ЛЭ2 формирует на его выходе сигнал "0". Он поступает на вход ЛЭ1 и комбинация "0" и "0"на входе ЛЭ2 формирует на его выходе сигнал "1".

Таблица состояний для триггеров называется таблицей переходов.

Схема управления – это КС, при помощи которой производится запись данных в триггер, зависит от типа триггера - RS,JK,Dили Т.

Триггеры бывают:

· асинхронными – состояние триггера не зависит от синхронизирующих сигналов, в них используются только информационные входы КС, т.е. подача сигналов на их входы не зависит от времени (не синхронизирована) и

· синхронными – переключение триггера возможно только при наличии разрешающего сигнала ("1") на синхровходе С. Если он отсутствует (равен "0"), то состояние триггера не изменится при любых сочетаниях сигналов на информационных входах.

Рисунок 4 Синхронный триггер

!!Триггеры являются одноразрядными элементами памяти!!

2.1Асинхронный RS - триггер с прямыми входами

Простейшим видом триггера является RS - триггер, который собирается из двух логических элементов ИЛИ-НЕ с перекрёстными обратными связями (рис. 5):

| S

S

| R

| Q

|

| Примечание

|

| 0

| 0

| Qt

| Qt

| Хранение

|

| 1

| 0

| 1

| 0

| Установка 1

|

| 0

| 1

| 0

| 1

| Установка 0

|

| 1

| 1

| 1

| 1

| Запрещено

|

Рисунок 5 – Устройство, схемное обозначение и таблица переходов RS - триггера

В таблице состояний Qt означает значение выхода Qв момент времени t, т.е. предыдущее состояние, до подачи сигналов на вход триггера.

При подаче логического “0” на оба входа S и R состояние триггера не изменяется, он сохраняет предыдущие уровни напряжений на обоих выходах, этот режим используется для хранения записанной информации

Принцип действия RS – триггера: основан на логике работы логического элемента 2ИЛИ-НЕ:

· при подаче логической “1” на вход S и логического “0” на вход R триггер устанавливается в единичное состояние по выходу Q независимо от его предыдущего состояния, т.е. в триггер записывается “1”.

· при подаче “0” на вход S и “1” на вход R триггер сбрасывается, т.е. на выходе Q появляется логический “0” - в него записывается “0” независимо от предыдущего состояния.

· при подаче логической “1” на оба входа,S и R триггер оказывается в неопределённом состоянии, т.к. его работа нарушается, поэтому это сочетание запрещено и в более сложных схемах, которые строятся на RS- триггерах (JK-триггеры) эта комбинация исключается.

· при подаче логического “0” на оба входа S и R состояние триггера не изменяется, онсохраняет предыдущие уровни напряжений на обоих выходах, этот режим используется для хранения записанной информации

Триггер реализует минимальную булеву функцию

Qt+1= St + Rt∙Qt

где - Qt+1состояние триггера после подачи входного сигнала (новое установившееся значение).

Из выражения видно, что RS-триггер устанавливается в 1 при подаче на вход St = 1 или остаётся в состоянии 1, если Rt = 1 и триггер был в состоянии Qt = 1.

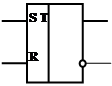

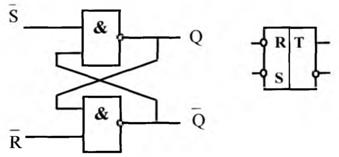

2.2 Асинхронный RS - триггер с инверсными входами

В цифровой технике чаще используется асинхронный RS - триггер с инверсными входами, схема которого аналогична схеме, приведённой на рис. 5, но вместо элементов 2ИЛИ-НЕ в ней используются элементы 2И- НЕ (рис. 6). Вследствие этого таблица состояний инверсного RS-триггера изменяется, активным входным сигналом является уровень “0”, а пассивным - уровень “1”. Это означает, что триггер устанавливается в состояние “1” при подаче “0” на вход S и сбрасывается при подаче “0” на вход R:

Рисунок 6 Устройство, схемное обозначение и таблица

переходов инверсного RS– триггера

2.3 Синхронный RS - триггер

Синхронный RS - триггер отличается от асинхронного наличием С- входа, на который поступают тактовые (синхронизирующие) импульсы.

Он состоит из асинхронного RS-триггера на элементах И-НЕ и комбинационного цифрового устройства (КЦУ) со входом С, принимающего сигналы от тактового генератора.

При С=0 входы триггера S и R заблокированы, КЦУ подаёт на них логическую “1”, т.е. триггер сохраняет записанную информацию. При С=1 КЦУ расблокировывает входы S и R и триггер работает по правилам асинхронного инверсного триггера.

Схемное обозначение синхронного триггера (рис. 6):

Рисунок 6 Схема синхронного триггера

Для выполнения различных функций используются различные виды триггеров: JK, D, Т - триггеры,двухступенчатые триггеры master-slave триггеры, которые запускаются передним или задним фронтом тактовых импульсов (это обеспечивается введением в RS-триггер дополнительных инверторов НЕ), триггеры, запускаемые импульсами и др. Основным строительным элементом для них является рассмотренный RS-триггер, который по этой причине называют универсальным.

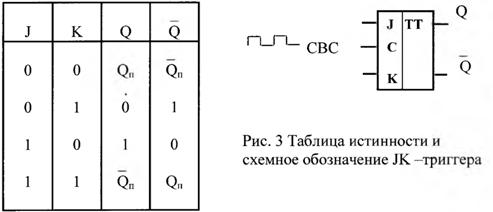

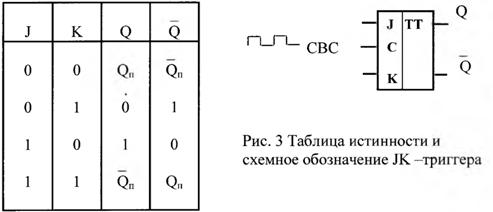

2.4 Универсальный JK - триггер

JK - триггер является тактируемым триггером, имеющим три входа - J (установка), К (сброс), тактовый вход С и два выхода О и не-Q. Кроме JKС-входов, триггер также может иметь асинхронные (не зависящие от С) входы S и R.

Тактируемый триггер - это триггер, который сохраняет своё состояние на выходе до прихода следующего активного фронта тактового импульса (переднего или заднего) или до появления всего импульса (если он не прямоугольный).

Таблица переходов и схемное обозначение JK -триггера показаны на рис. 7, где СВС - синхронизирующий входной сигнал, а символ Qп обозначает прежнее состояние, т.е. состояние выхода Q непосредственно перед приходом активного логического уровня сигнала на тактовом входе С.

Сигналы на синхронизирующий вход С подаются от тактового генератора, который формирует тактовые импульсы с высокостабильной частотой.

Сигналы на входах J и К проходят через триггер только тогда, когдаесть сигнал на синхровходе С, поэтому JK-триггер называется триггером ссинхронными входами. Входы R и S являются асинхронными, т.е. не зависят от тактового сигнала на входе С.

2.5 D-триггер

D-триггер или триггер задержки (от англ. delay - задержка) является тактируемым триггером, имеет вход С и один информационным вход D(рис. 8). Его назначение - задержка входного сигнала. Схема D–триггераполучена из JK-триггера соединением входа J с входом К через инверторНЕ.

Под действием синхросигнала данные, поступающие на вход D, записываются в триггер, но только при наличии тактового импульса на входе

С, т.е. на выходе Q сигналы появляются с задержкой на время прихода

тактового импульса. Таким образом, на выходе Q текущее состояние его

входа (“1” или ”0”) воспроизводится только в момент смены логического

состояния тактового сигнала СВС.

Рисунок 8 Схема, обозначение, временная диаграмма и

таблица переходовD-триггера

Т- триггер

Т-триггер называется триггером со счётным входом, т.к. переключается в противоположное состояние только при поступлении на информационный вход сигнала “1” (т.е. считает логические “1”).

Т-триггер является тактируемым триггером, информационным входомкоторого является вход С. Выход Т-триггера переключается при каждомпоступлении синхронизирующего сигнала СВС. Частота сигнала на выходе в два раза меньше, чем входная. Т-триггер строится на основе JK-триггера, на входах J и К которого поддерживается логический уровеньединицы (рис. 9).

Рисунок9 Таблица переходов, схема и обозначение Т-триггера

Помимо рассмотренных в ПК применяются двухтактные RS–триггеры (состоят из двух RS-триггеров, в которых для надёжности записи новой информации используются две серии синхроимпульсов, сдвинутых на полпериода. По первому синхроимпульсу данные записываются в первый RS-триггер, по второму – переписывается во второй.