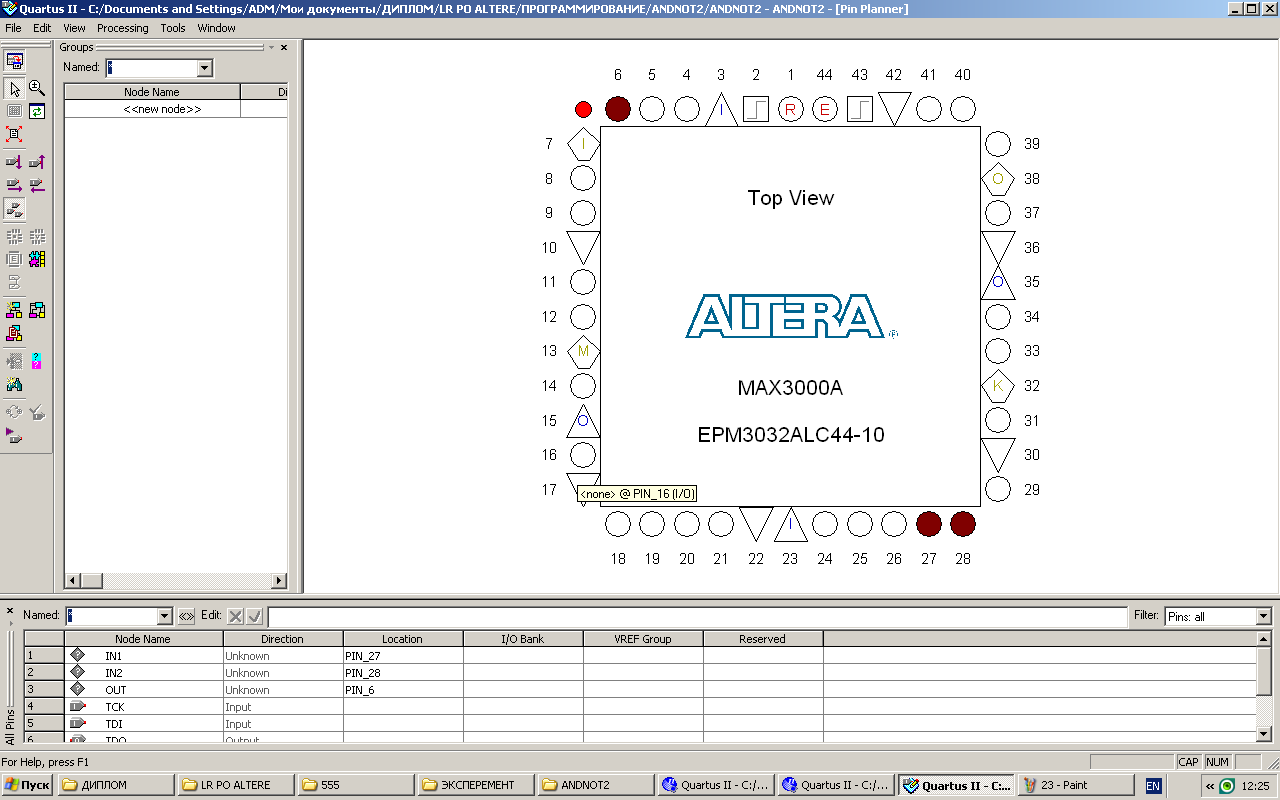

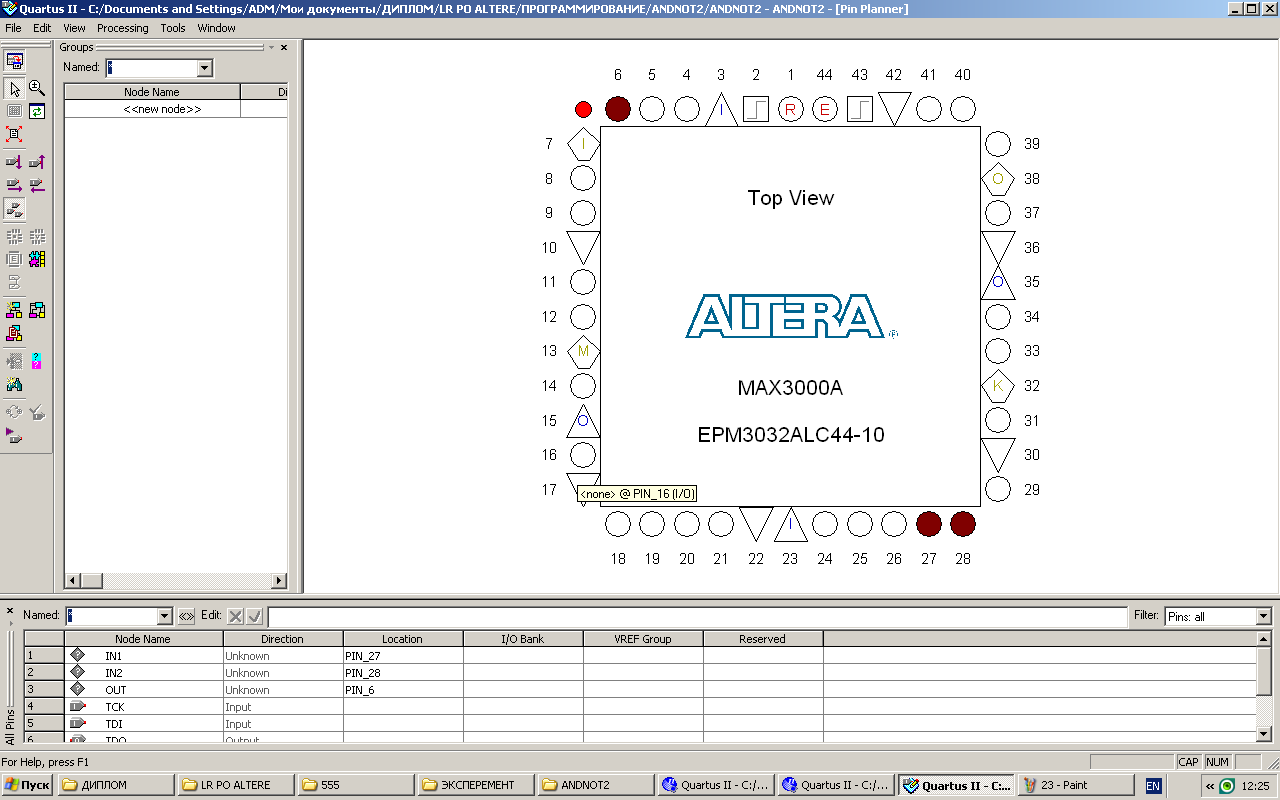

· При создании проекта входы и выходы на ПЛИСе задаются автоматически (программа автоматически определяет контакты и их назначение) и практически всегда находятся не там где нам нужно. Для принудительного назначения контактов входов и выходов необходимо в главном меню выбрать опцию “Assigments/Pins” (“Назначение/Контакты”) (рис. 2.44).

Рис. 2.44

· В появившемся окне выбрать на схематичном изображении один из контактов, например, номер 27 (рис. 2.45), и присвоить ему вход IN 1. Для этого необходимо 2 раза нажать левой кнопк ой мыши на контакт 27, после чего появится окно “Pin Properties” (“Свойства контакта”).

Рис. 2.45

· В окне “Pin Properties” (“Свойства контакта”) в списке “Node Name” выбираем интересующий нас вход IN1 и нажимаем “OK” (рис. 2.46).

Рис. 2.46

· Аналогично присваиваем контакту №28 (Рис….) IN2 и контакту №6 OUT (рис. 2.47).

Рис. 2.47

· Снова производим компиляцию проекта и убеждаемся в её правильном завершении.

Always -блоки, операторы if и case в Verilog

Процесс-блоки (always -блоки)

Блоки подобного типа здесь названы в силу того, что они реализуют некий процесс, который может повторятся многократно. В литературе их часто называют always-блоками по ключевому слову, определяющему такой блок.

Для описания поведенческого блока используется следующий синтаксис:

always @(<sensitivity_list>) <statements>

<sensitivity_list> – это список всех входных сигналов, к которым чувствителен блок. Это список входных сигналов, изменение которых влияет выходные сигналы этого блока. " Always " переводится как "всегда". Такую запись можно прочитать вот так: "Всегда выполнять выражения <statements> при изменении сигналов, описаных в списке чувствительности <sensitivity list>". Если указать список чувствительности неверно, то это не должно повлиять на синтез проекта, но может повлиять на его симуляцию. В списке чувствительности имена входных сигналов разделяются ключевым словом " or ": always @(a or b or d) <statements>

Иногда гораздо проще и надежней включать в список чувствительности все сигналы. Это делается так: always @* <statements>

Тогда исправляя выражения в <statements> вам не нужно задумываться об изменении списка чувствительности.

При описании выражений внутри поведенческих блоков комбинаторной логики, с правой стороны от знака равенства, как и раньше, можно использовать типы сигналов wire или reg, а вот с левой стороны теперь используется только тип reg:

reg [3:0] c;

always @(a or b or d)

begin

c = <выражение использующее входные сигналы a,b,d>;

end

Синтаксис оператора if

Оператор ветвления if широко применяется для реализации элементов регистровой логики, таких как регистры данных, сдвига, счетчиков, цифровых автоматов и т.д. Синтаксис этого оператора очень похож на синтаксис в языке С. Общий вид оператора выглядит так:

if (<cond_expr1>)

[ begin ]

<statements>;

[ end ]

else if (<cond_expr2>)

[ begin ]

<statements>;

[ end ]

Else

[ begin ]

<statements>;

[ end ]

Обязательной ветвью в этом операторе является ветвь после ключевого слова if. Ветви else if и else добавляются если они необходимы. Условные выражения cond_expr принимают значения true (результат cond_expr отличен от нуля) или false (результат равен нулю). Логика выполнения оператора следующая: если выполняется условие cond_expr1 (cond_expr1!= 0), то выполняется ветвь под оператором if, а остальные ветви пропускаются. Когда условие не выполняется (cond_expr1 == 0), осуществляется проверка условия cond_expr2. Ветвей else if в операторе может быть несколько. Если не выполняется предыдущее условие, то выполняется следующее. Когда не выполнилось ни одно из условий, управление передается ветви else (если она есть). Когда эта ветвь отсутствует, осуществляется выход из оператора. Ключевые слова begin – end обозначают границы последовательных блоков. Если в ветви только одно выражение, эти ключевые слова можно опустить. Ветви if, else if и else иногда называют параллельными в том смысле, что всегда выполняется только одна из них. Операторы if могут быть вложенными – внутри одной ветви оператора вполне может быть размещен другой оператор if.

Синтаксис операторов case

Синтаксис оператора case выглядит так:

case (<cond_expr>)

<const_cond_1>: <statement>;

<const_cond_2>: <statement>;

* * *

<const_cond_n>: <statement>;

[ default: <statement>;]

Endcase

В этом операторе результат cond_expr по порядку сравнивается с константными условиями const_cond. В случае совпадения результата с одним из выражений, выполняется выражение statement соответствующее этому константному условию. Если не выполнилось ни одно из условий, то выполняется ветвь под ключевым словом default (если она есть – в противном случае не выполняется ни одно из выражений). Завершается оператор ключевым словом endcase.