Синтаксис операций Verilog похож на синтаксис операций языка С. Символы операций, их названия, а также применимость к вещественным переменным приведены в таблице 1.

Таблица 1

| Символ

| Описание операции

| Применимость к real

|

| + - * /

| Арифметические

| Допустимо

|

| %

| Модуль

| Не допустимо

|

| > >= < <=

| Отношения

| Допустимо

|

| !

| Логическое отрицание

| Допустимо

|

| &&

| Логическое И

| Допустимо

|

| ||

| Логическое ИЛИ

| Допустимо

|

| ==

| Логическое равенство

| Допустимо

|

| !=

| Логическое неравенство

| Допустимо

|

| ===

| Идентичность

| Не допустимо

|

| !===

| Неидентичность

| Не допустимо

|

| ~

| Побитовая инверсия

| Не допустимо

|

| &

| Побитовое И

| Не допустимо

|

| |

| Побитовое ИЛИ

| Не допустимо

|

| ^

| Побитовое исключающее ИЛИ

| Не допустимо

|

| | | |

| <<

| Сдвиг влево

| Не допустимо

|

| >>

| Сдвиг вправо

| Не допустимо

|

| <<<

| Циклический сдвиг влево

| Не допустимо

|

| >>>

| Циклический сдвиг вправо

| Не допустимо

|

| ?:

| Условный оператор

| Допустимо

|

Рассмотрим операции Verilog в порядке убывания приоритета:

- + -! ~ (унарные) наивысший приоритет

- * / %

- + - (бинарные)

- << >> <<< >>>

- < <= > >=

- ?: Низший приоритет

Операции с равным приоритетом выполняются слева направо, за исключением символа?, который выполняется справа налево.

Для закрепления синтаксиса операций Verilog опишем на языке Verilog цифровое устройство шифратор с 8 входами и 3-мя выходами.

СДНФ:

Y 1 = X 1 v X 3 v X 5 v X 7

Y2=X2 v X3 v X6 v X7

Y3=X4 v X5 v X6 v X7

Зная структурные формулы шифратора, например, в СДНФ, опишем его схему на языке Verilog.

1-й способ:

module SHIFRATOR (input X1, input X2, input X3, input X4, input X5, input X6, input X7, output Y1, output Y2, output Y3);

assign Y 1 = X 1 | X 3 | X 5 | X 7; // где “ | ” – логическая операция ИЛИ (дизъюнкция)

assign Y2=X2 | X3 | X6 | X7;

assign Y3=X4 | X5 | X6 | X7;

Endmodule

2-й способ:

module SHIFRATOR (X1, X2, X3, X4, X5, X6, X7, Y1, Y2, Y3);

input X1, X2, X3, X4, X5, X6, X7;

output Y1, Y2, Y3;

assign Y1=X1 | X3 | X5 | X7;

assign Y2=X2 | X3 | X6 | X7;

assign Y3=X4 | X5 | X6 | X7;

Endmodule

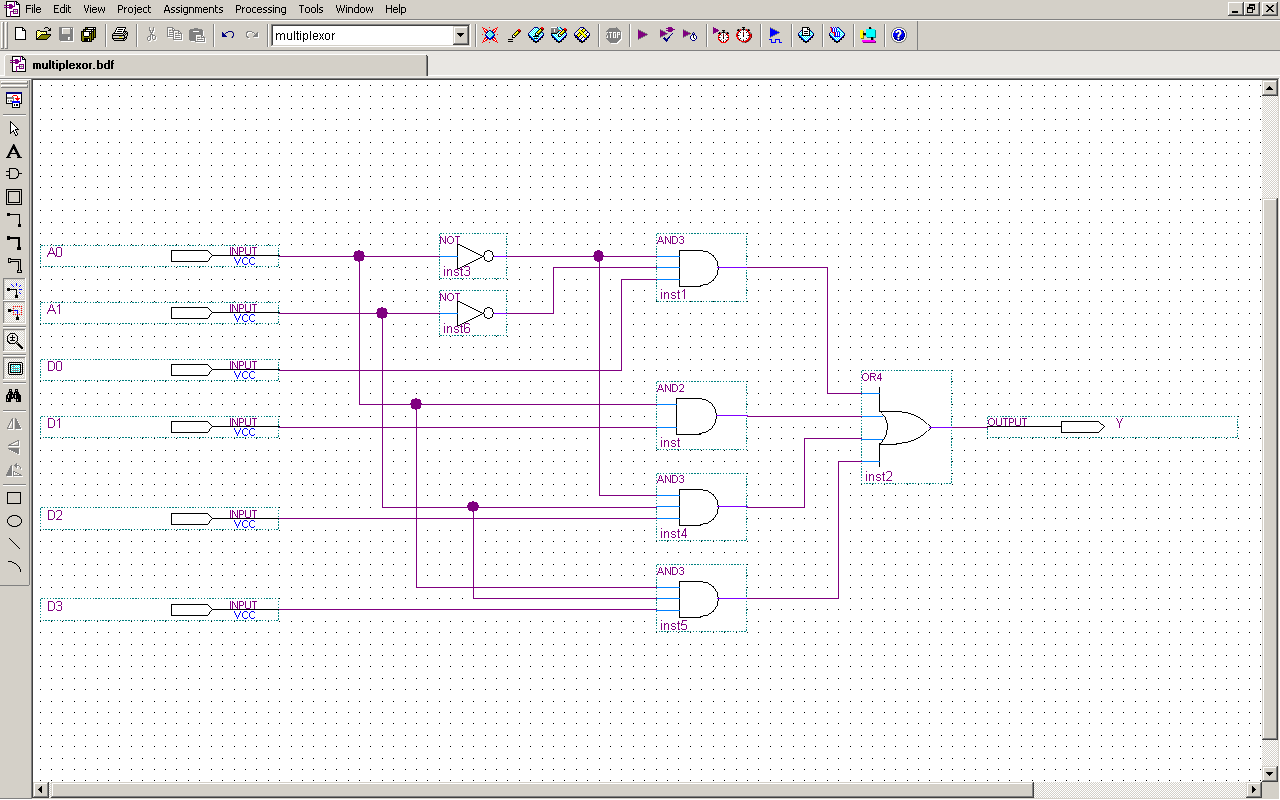

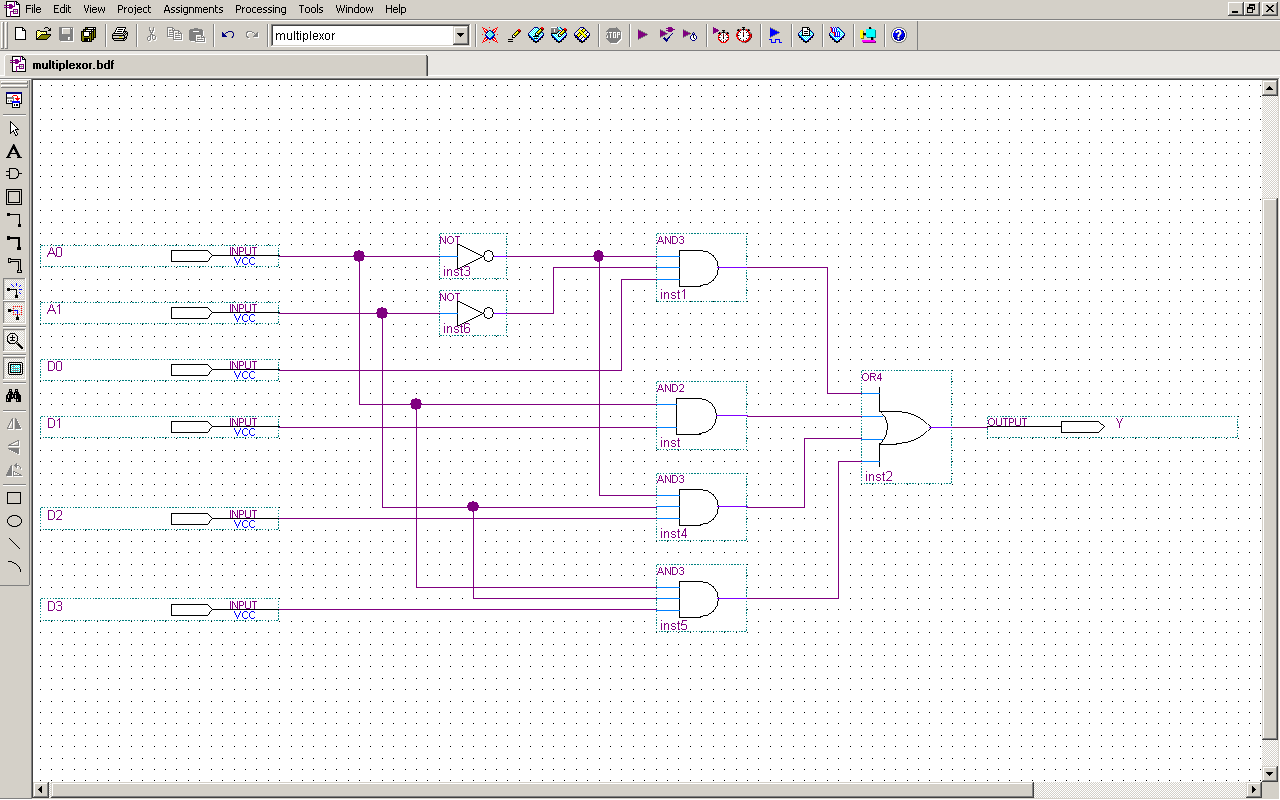

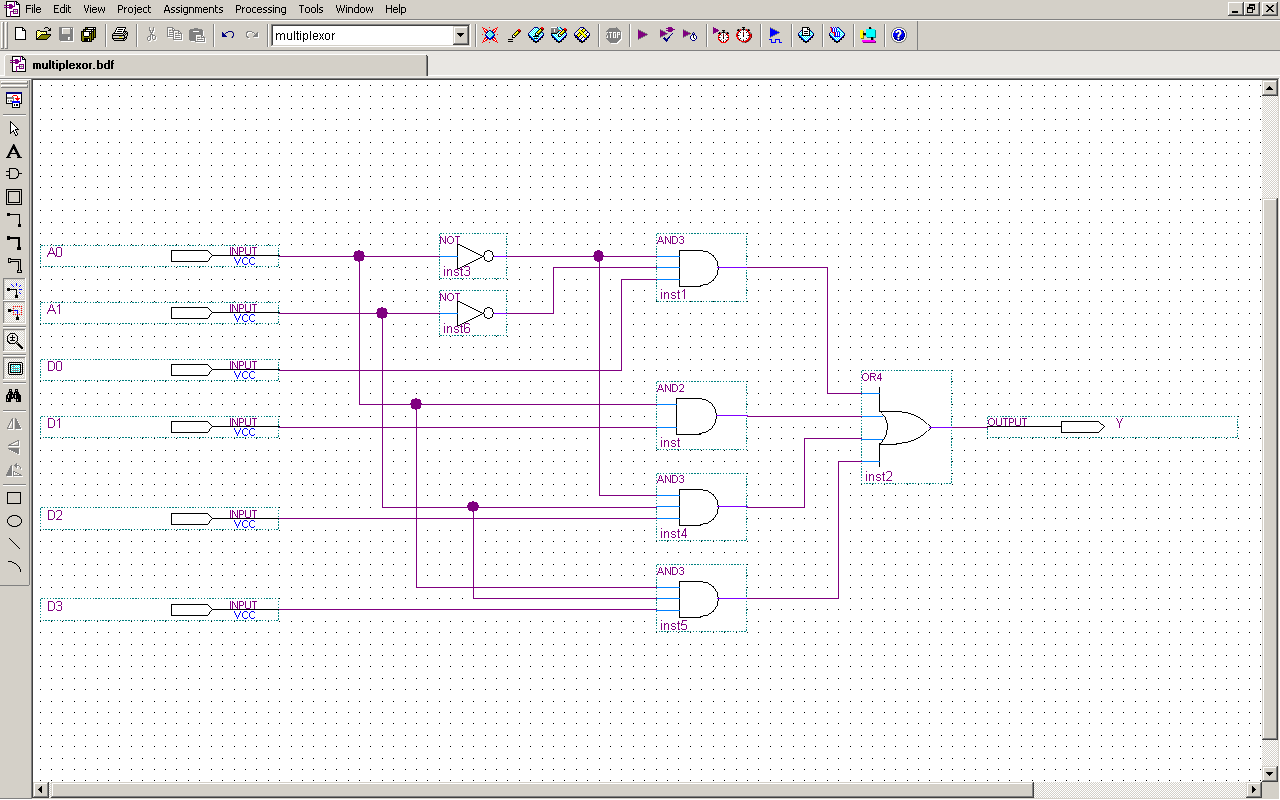

Аналогичная опишем четырехканальный мультиплексор, структурная формула которого в СДНФ имеет вид:

В соответствии со структурной формулой схема мультиплексора в блочном описании на языке Verilog имеет вид (исправить ошибку в схеме):

Опишем схему мультиплексора на языке Verilog

1-й способ:

module MULTIPLEXOR (A0, A1, D0, D1, D2, D3, Y);

input A0, A1, D0, D1, D2, D3;

output Y;

assign Y=(D0 &!A1&!A0) | (D1 &!A1& A0) | (D2 & A1&!A0) | (D3 & A1 & A0);

Endmodule

2-й способ (описание мультиплексора через wire):

module MULTIPLEXOR (input A0, input A1, input D0, input D1, input D2, input D3,

output Y);

wire S1, S2, S3, S4, S5, S6;

NOT my_1_not (.OUT(S1),.IN1(A0));

NOT my_2_not (.OUT(S2),.IN1(A1));

AND3 my_1_and (.OUT(S3),.IN1(S1),.IN2(S2),.IN3(D0));

AND2 my_2_and (.OUT(S4),.IN1(A0),.IN2(D1));

AND3 my_3_and (.OUT(S5),.IN1(S1),.IN2(A1),.IN3(D2));

AND3 my_4_and (.OUT(S6),.IN1(A0),.IN2(A1),.IN3(D3));

OR4 my_or (.OUT(Y),.IN1(S3),.IN2(S4),.IN3(S5),.IN4(S6));

Endmodule

Разработка модулей высокого уровня на ПЛИС на примере сумматора

Мы знаем про основные базовые логические элементы – и это тоже модули. Используем их в модуле более высокого уровня. Сделаем однобитный сумматор, а на его основе много битный сумматор (более высокого уровня).

Вначале рассмотрим синтез сумматора от постановки задачи до создания схемы однобитного сумматора.

Однобитный сумматор складывает два однобитных числа a и b. При выполнении сложения однобитных чисел может случиться «переполнение», то есть результат уже будет двух битным (1+1=2 или в двоичном виде 1’b1+1’b1=2’b10). Поэтому включим в сумматор выходной сигнал переноса c _ out.

Дополнительный входной сигнал c _ in служит для приема сигнала переноса от сумматоров младших разрядов (при построении много битных сумматоров).

Таблица истинности работы однобитного сумматора.

| №

п/п

| a

| b

| c_in

| sum

| c_out

| Примечание

|

| 0

| 0

| 0

| 0

| 0

| 0

|

|

| 1

| 0

| 1

| 1

| 1

| 1

| Перенос

|

| 2

| 1

| 0

| 0

| 1

| 0

|

|

| 3

| 1

| 1

| 1

| 0

| 1

| Перенос

|

Примечание: С целью упрощения таблицы не все события в таблице перечислены для c _ in, sum, c _ out.

Структурные формулы работы однобитного сумматора с учетом минимизации учитывает все возможные события.

sum=(a^b) ^ c_in

c_out=((a^b) & c_in) ^ (a &b),

где символ «^» - сложение по модулю 2, символ «&» - логическая операция конъюнкция (and).

Схема согласно структурной формулы в графическом виде имеет вид:

Опишем эту схему на языке Verilog, устанавливая в теле модуля экземпляры других модулей.

Итак, модуль одно битного сумматора содержит 3 экземпляра модуля XOR и два экземпляра модуля AND 2.

Порядок описания экземпляра модуля такой:

• название модуля, тип которого нам нужен (adder1) с указанием входов и выходов;

• описываем подключение сигналов: точка и затем имя сигнала модуля, затем в скобках имя проводника, который сюда подключен.

module adder1(input a, input b, input

c_in, output sum, output c_out);

wire s1,s2,s3;

XOR my_1_xor(.OUT (s1),.IN1 (a),.IN2 (b));

AND2 my_1_and2(.OUT (s3),.IN1 (a),.IN2 (b));

XOR my_2_xor(.OUT (sum),.IN1 (s1),.IN2 (c_in));

AND2 my_2_and2(.OUT (s2),.IN1 (s1),.IN2 (c_in));

XOR my_3_xor(.OUT (c_out),.IN1 (s2),.IN2 (s3));

Endmodule

Опишем на языке Verilog однобитный сумматор на поведенческом уровне, то есть на основе структурных формул:

module adder1(input a, input b, input

c_in, output sum, output c_out);

assign sum = (a^b) ^ c_in;

assign c_out = ((a^b) & c_in) ^ (a&b);

endmodule

Следует помнить, что существуют разные методы описания и нужно уметь ими всеми пользоваться.

Итак, мы создали однобитный сумматор. На его основе можно создать n-битный сумматор. Рассмотрим, например, четырех битный сумматор (с

последовательным переносом).

Блочнe. схемe 4-х битного сумматора представим в виде:

Опишем эту схему на языке Verilog:

module adder4(output [3:0]sum, output c_out, input [3:0]a, input

[3:0]b);

wire c0, c1, c2;

adder1 my0_adder1(.sum (sum[0]),.c_out (c0),.a (a[0]),.b

(b[0]),.c_in (1’b0));

adder1 my1_adder1(.sum (sum[1]),.c_out (c1),.a (a[1]),.b

(b[1]),.c_in (c0));

adder1 my2_adder1(.sum (sum[2]),.c_out (c2),.a (a[2]),.b

(b[2]),.c_in (c1));

adder1 my3_adder1(.sum (sum[3]),.c_out (c_out),.a (a[3]),.b

(b[3]),.c_in (c2));

endmodule

Таким образом, мы реализовали четырехбитный сумматор. Мы получили его как модуль верхнего уровня adder 4, состоящий из модулей adder 1, которые, в свою очередь состоят из модулей примитивов AND 2 и XOR.