Временные диаграммы шины PCI

7.Последовательность пакетов при вводе-выводе по шине USB.

Каждому пакету предшествует поле синхронизации SYNC, позволяющее приемнику настроиться на частоту передатчика. Кабель также имеет линии VBus и GND для передачи питающего напряжения 5 В к устройствам. Сечение проводников выбирается в соответствии с длиной сегмента для обеспечения гарантированного уровня сигнала и питающего напряжения.

В пакетах-маркерах IN, SETUP и OUT следующими являются адресные поля: 7-битный адрес функции и 4-битный адрес конечной точки. Они позволяют адресовать до 127 функций USB (нулевой адрес используется для конфигурирования) и по 16 конечных точек в каждой функции. В пакете SOF имеется 11-битное поле номера кадра (Frame Number Field), последовательно (циклически) увеличиваемое для очередного кадра. Поле данных может иметь размер от 0 до 1023 целых байт. Размер поля зависит от типа передачи и согласуется при установлении канала. Поле СКС-кола присутствует во всех маркерах и пакетах данных, оно защищает все поля пакета, исключая PID. CRC для маркеров (5 бит) и данных (11 бит) подсчитываются по разным формулам. Каждая транзакция инициируется хост-контроллером посылкой маркера и завершается пакетом квитирования. Последовательность пакетов в транзакциях иллюстрирует рис. 7.7. Хост-контроллер организует обмены с устройствами согласно своему плану распределения ресурсов. Контроллер циклически (с периодом 1 мс) формирует кадры (Frames), в которые укладываются все запланированные транзакции. Каждый кадр начинается с посылки маркера SOF (Start Of Frame), который является синхронизирующим сигналом для всех устройств, включая хабы. В конце каждого кадра выделяется интервал времени EOF (End Of Frame), на время которого хабы запрещают передачу по направлению к контроллеру. Каждый кадр имеет свой номер. Хост-контроллер оперирует 32-битным счетчиком, но в маркере SOF передает только младшие 11 бит. Номер кадра увеличивается (циклически) во время EOF. Хост планирует загрузку кадров так, чтобы в них всегда находилось место для транзакций управления и прерывания. Свободное время кадров может заполняться сплошными передачами (Bulk Transfers).

Архитектура шины USB.

USB (англ. Universal Serial Bus) — универсальная последовательная шина, предназначенная для периферийных устройств.

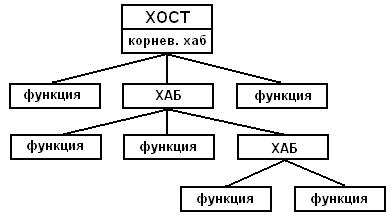

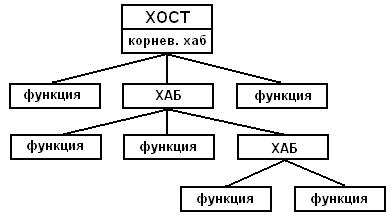

Общая архитектура шины:

Если ХАБ встроен в компьютер – это корневой хаб.

Типовая архитектура USB:

Практически все современные чипсеты поддерживают интерфейс USB, в том числе новой спецификации 2.0. Архитектурой USB предусмотрена топология так называемой «звезды». То есть в системе должен быть корневой (ведущий) концентратор, к которому подключаются периферийные концентраторы, а к последним — устройства USB. Корневой концентратор расположен в одной из микросхем системного набора (обычно в «южном мосту»). Периферийные концентраторы могут подключаться друг к другу, образуя каскады. Всего через один корневой концентратор может быть подключено до 127 устройств (концентраторов и устройств USВ). Однако, оптимальным числом следует считать 4-5 устройств. При этом рекомендуется более скоростные устройства подключать ближе к корневому концентратору. Проблема низкой пропускной способности снимается с внедрением спецификации интерфейса USB 2.0, чья пиковая производительность достигает 480 Мбит/с. Такого значения вполне хватает для типичных USB-устройств: принтеров, офисных сканеров, цифровых фотокамер, джойстиков и прочих. Но все же для внешних накопителей, сканеров высокого класса, цифровых видеокамер требуется более скоростной интерфейс: IEEE 1394 или SCSI.

Спецификация USВ определяет две части интерфейса: внутреннюю и внешнюю. Внутренняя часть делится на аппаратную (собственно корневой концентратор и контроллер USB) и программную (драйверы контроллера, шины, концентратора, клиентов). Внешнюю часть представляют устройства (концентраторы и компоненты) USB. Для обеспечения корректной работы все устройства делятся на классы: принтеры, сканеры, накопители и т. д.

Данные по шине USB передаются в различных форматах. Самый простой способ заключается в передаче потока байтов с маркером. Все устройства USB соединяются между собой четырехжильным кабелем. По одной паре передаются данные, по другой — электропитание, которое автоматически подключается устройством при необходимости. На концах кабеля монтируются разъемы типов «А» и «В». С помощью разъема «А» устройство подключают к концентратору. Разъем типа «В» устанавливают на концентраторы для связи с другим концентратором и на устройства, от которых кабель должен отключаться (например, сканеры). В духе современной тенденции к упрощению пользования компьютером реализована процедура подключения периферии к шине USB. Все происходит «в горячем режиме». Подключенное в свободный порт устройство вызывает перепад напряжения в цепи. Контроллер немедленно направляет запрос на этот порт. Присоединенное устройство принимает запрос и посылает пакет с данными о классе, затем ему присваивается уникальный идентификационный номер. Далее происходит автоматическая загрузка и активация драйвера устройства, его конфигурирование и, тем самым, окончательное подключение. Все. устройство готово к работе! Точно так же происходит инициализация уже подсоединенного и включаемого в сеть устройства.

Графическое обозначение

9 Организация внутренней памяти ПК типа PC\XT. Назначение управляющих сигналов системного интерфейса ПК #RAS, #CAS, #WE.

Динамическая память — DRАM (Dynamic RAM) — получила свое название от принципа действия ее запоминающих ячеек, которые выполнены в виде конденсаторов, образованных элементами полупроводниковых микросхем. При отсутствии обращения к ячейке со временем за счет токов утечки конденсатор разряжается и информация теряется, поэтому такая память требует периодической подзарядки конденсаторов (обращения к каждой ячейке) — память может работать только в динамическом режиме. Этим она принципиально отличается от статической памяти, реализуемой на триггерных ячейках и хранящей информацию без обращений к ней сколь угодно долго (при включенном питании).

Запоминающие ячейки микросхем DRAM организованы в виде двумерной матрицы. Адреса строки и столбца передаются по мультиплексированной шине адреса MA (Multiplexed Address) и стробируются по спаду импульсов RAS# (Row Access Strobe) и CAS# (Column Access Strobe).Выбранной микросхемой памяти является та, на которую во время активности (низкого уровня) сигнала RAS# приходит сигнал CAS# (тоже низким уровнем). Тип обращения определяется сигналами WE# и CAS#.

Поскольку обращения (запись или чтение) к различным ячейкам памяти обычно происходят в случайном порядке, то для поддержания сохранности данных применяется регенерация (Memory Refresh — обновление памяти) — регулярный циклический перебор ее ячеек (обращение к ним) с холостыми циклами. Циклы регенерации могут организовываться разными способами, классическим является цикл без импульса CAS#, сокращенно именуемый ROR (RAS Only Refresh — регенерация только импульсом RAS#). Другой вариант — цикл CBR (CAS Before RAS), поддерживаемый практически всеми современными микросхемами памяти. В этом цикле регенерации спад импульса RAS# осуществляется при низком уровне сигнала CAS# (в обычном цикле обращения такой ситуации не возникает). Адрес регене-нируемой строки для цикла ROR генерирует контроллер памяти, для CBR этот адрес берется из внутреннего счетчика каждой микросхемы памяти. Цикл скрытой регенерации (hidden refresh) является разновидностью цикла CBR.

Память PC \XT – 1 Мбайт (220) образована из 4х банков памяти, каждая по 256 Кбайт. Банки внутренней памяти состоят из 4х групп (bank0-3), каждый из которых состоит из 9ти микросхем, 9ая используется для контроля на четность. Контроллер управления памятью на основе сигналов А18, А19 формирует сигналы следующей последовательности:

1) Строб адреса строки.

2) Сигнал ASEL, по которому мультиплексор переключается с выдачи адреса строки на выдачу адреса столбца.

3) Формирует строб адреса столбцов.

4) Формирует сигнал разрешения записи WE# - 0 или 1.

Схема контроля на четность формирует 9ый бит – контрольный-для записи, т.е. при записи каждого байта подсчитывается контрольный бит. При чтении байта подсчитывается по 8ми битам контрольная сумма и сравнивается с 9ым битом. Если не совпадает, то сигнал PCK.

· RAS# (Row Access Strobe) — строб выборки адреса строки. По спаду сигнала начинается любой цикл обращения; низкий уровень сохраняется на все время цикла. Перед началом следующего цикла сигнал должен находиться в неактивном состоянии (высокий уровень) не менее, чем время предварительного заряда RAS (TRP — RAS precharge time).

· CAS# (Column Access Strobe) — строб выборки адреса столбца. По спаду сигнала начинается цикл записи или чтения; минимальная длительность (Тсдз) определяется спецификацией быстродействия памяти. Минимальная длительность неактивного состояния между циклами (высокий уровень) должна быть не менее, чем время предварительного заряда CAS (TCP — CAS precharge time).

· WE# (Write Enable) — разрешение записи. Данные записываются в выбранную ячейку либо по спаду CAS# при низком уровне WE# (Early Write — ранняя запись, обычный вариант), либо по спаду WE# при низком уровне CAS# (Delayed Write — задержанная запись). Переход WE# в низкий уровень и обратно при высоком уровне CAS# записи не вызывает, а только переводит выходной буфер EDO DRAM в высокоимпедансное состояние

10.Физическая реализация интерфейса ISA. Особенности применения интерфейса ISA в компьютерах типа PC\XT и современных компьютерах.

Магистраль ISA была разработана специально для персональных компьютеров типа IBM PC AT (начиная с процессора i80286) и является фактическим стандартом для всех изготовителей этих компьютеров. В то же время отсутствие официального международного статуса магистрали ISA (она не утверждена в качестве стандарта ни одним международным комитетом по стандартизации) приводит к тому, что многие производители допускают некоторые, порой существенные отклонения от фирменного стандарта.

ISA явилась расширением магистрали компьютеров IBM PC и IBM PC XT. В ней было увеличено количество разрядов адреса и данных, увеличено число линий аппаратных прерываний и каналов ПДП, а также повышена тактовая частота. К 62-контактному разъему прежней магистрали был добавлен 36-контактный новый разъем. Тем не менее, совместимость была сохранена, и платы, предназначенные для IBM PC XT, годятся и для IBM PC AT. Характерное отличие ISA состоит в том, что ее тактовый сигнал не совпадает с тактовым сигналом процессора, как это было в XT, поэтому скорость обмена по ней не пропорциональна тактовой частоте процессора.

Магистраль ISA относится к демультиплексированным (то есть имеющим раздельные шины адреса и данных) 16-разрядным системным магистралям среднего быстродействия. Обмен осуществляется 8- или 16-разрядными данными. На магистрали реализован раздельный доступ к памяти компьютера и к устройствам ввода/вывода (для этого имеются специальные сигналы). Максимальный объем адресуемой памяти составляет 16 Мбайт (24 адресные линии). Максимальное адресное пространство для устройств ввода/вывода - 64 Кбайта (16 адресных линий), хотя практически все выпускаемые платы расширения используют только 10 адресных линий (1 Кбайт). Магистраль поддерживает регенерацию динамической памяти, радиальные прерывания и прямой доступ к памяти. Допускается также захват магистрали. Каждая операция определяется протоколами. Пропускная способность шины=4,77МГц*8/8=4,77Мб/с.

Связь между двумя компьютерами осуществляется по принципу задатчик-исполнитель. В каждый момент времени шиной может управлять только одно устройство-задатчик, обращающееся к ресурсам (портам или ячейкам памяти) устройств-исполнителей. Задатчик – CPU или контроллер ПДП. Имеет 32 контактный разъём.

С появлением Pentium для соединения устройств было предложено использовать 2 интерфейса: локальный (PCI) и системный (ISA). Теперь к шине ISA стали подключать медленнодействующие устройства, такие как клавиатура, мышь, FDD, LPT, COM, а микропроцессор с памятью и некоторыми быстродействующими ВУ стала связывать шина PCI. В современных компьютерах основной шиной расширения является PCI; ее дополняет порт AGP. Шина ISA из настольных компьютеров уходит, но она сохраняет свои позиции в промышленных и встраиваемых компьютерах в традиционном слотовом варианте.

Физически слот ISA-8 представляет собой 62-х контактный разъем (ряды A, B).

Конструктивно выполнен в виде щелевого разъема с шагом выводов 2,54 мм (0,1 дюйма).

Сигналы имеют стандартный ТТЛ-уровень.

1) Линии передачи данных.

А19-А0 – 20-разрядная шина адреса

D7-D0 – 8-разрядная шина данных

BALE (Bus Address Latch Enable - разрешение защелкивания адреса) (ALE) - сигнал стробирования адресных разрядов. Его отрицательный фронт соответствует действительности адреса на линиях SAO...SA19 и LA17...LA23. Может использоваться устройствами ввода/вывода для заблаговременной подготовки к предстоящему обмену информацией (применяется редко). Тип выходного каскада - ТТЛ.  ,

,  - чтение/запись (БП)

- чтение/запись (БП)

- чтение/запись (УВВ)

- чтение/запись (УВВ)

2) Линии прерывания и ПДП.

IRQ2-IRQ7 – запрос на прерывания (Interrupt Request - запрос прерывания) - сигналы запроса радиальных прерываний. Запросом является положительный переход на соответствующей линии IRQ. Сигнал должен удерживаться до начала обработки процессором запрошенного прерывания. Тип выходного каскада - ТТЛ. На каждой линии IRQ должен быть один выход. Иногда в литературе можно встретить рекомендацию применять выходы с тремя состояниями, но все равно больше одного выхода на линию быть не должно во избежание конфликтов сигналов. Многие входы IRQ заняты системными ресурсами компьютера (табл. 6). Сигналы IRQ0...IRQ2, IRQ8 и IRQ13 задействованы на системной плате и недоступны платам расширения. В компьютере используются два 8-разрядных контроллера прерываний. Сигналы IRQ0...IRQ7 относятся к первому из них, a IRQ8...IRQ15 - ко второму. Для каскадирования второго контроллера прерываний задействован вход IRQ2. В связи с этим запросы прерывания имеют следующие приоритеты в порядке возрастания: IRQ7, IRQ6, IRQ5, IRQ4 IRQ3, IRQ15, IRQ14, IRQ12, IRQ11, IRQ10, IRQ9.

DRQ1-DRQ3 – (DMA Request - запрос ПДП) - сигналы запросов прямого доступа к памяти (ПДП). Запросом является положительный переход на соответствующей линии DRQ. Сигнал должен удерживаться до получения ответного сигнала -DACK с тем же номером. Тип выходного каскада - ТТЛ. На каждой линии DRQ должен быть один выход. В компьютере используются два контроллера ПДП. Каналы ПДП, соответствующие первому контроллеру (сигналы DRQ0...DRQ3) предназначены для 8-битного обмена, а соответствующие второму котроллеру (DRQ5...DRQ7) - для 16-битного. Канал DRQ4 используется для каскадирования контроллеров и недоступен пользователям. DRQO имеет наивысший приоритет, DRQ7 - наинизший. В IBM PC XT канал DRQ0 использовался для регенерации динамической памяти. Канал DRQ1 зарезервирован для контроллера бисинхронного обмена SDLC, а канал DRQ2 - для контроллера гибкого диска.DACK0- DACK1 – разрешение ПДП

AEN (Address Enable - разрешение адреса) – используется в режиме ПДП для сообщения всем платам расширения, что производится цикл ПДП. Устанавливается и снимается параллельно с адресом. При его переходе в активное состояние все платы расширения, не участвующие в данном ПДП, должны отключаться от магистрали (переходить в пассивное состояние). Тип выходного каскада - ТТЛ.T/C – конец счета

3) Линии общего назначения:

RESET DRV – сброс

CLK – системная синхронизация (8 Мгц)

OSC – сигнал генератора (14, 4 Мгц – несинхр. с шиной)

I/O CH RDY – сигнал снимается (делается низким) исполнителем (устройством ввода/вывода или памятью) по переднему фронту сигналов -IOR и -IOW в случае, если он не успевает выполнить требуемую операцию в темпе задатчика. При этом реализуется асинхронный обмен. Если исполнитель успевает работать в темпе задатчика, сигнал не снимается (фактически не устанавливается в низкий уровень). Цикл обмена в ответ на снятие этого сигнала продлевается на целое число периодов сигнала SYSCLK. Сигнал I/O CH RDY не должен сниматься на время, большее заданного в данном компьютере (по стандарту - 15 мкс), иначе компьютер переходит к обработке немаскируемого прерывания. Тип выходного каскада - открытый коллектор.

I/O CH CK – сигнал вырабатывается любым исполнителем (устройством ввода/вывода или памятью) для информирования задатчика о фатальной ошибке, например об ошибке четности при доступе к памяти. Сигнал вызывает немаскируемое прерывание. Тип выходного каскада - открытый коллектор.

4) Линии питания:

±5В, ±12В, GND

В разъеме ISA-16 применяется дополнительный 36-контактный слот (ряды C, D).

Расширена за счет:

1) расширения шины адресов до 24-х линий

2) расширения шины данных до 16-и линий

3) добавления IRQ8-IRQ15

4) добавления DRQ4-DRQ7

Особенности:

1) Динамическая память, применяемая в компьютере в качестве системного ОЗУ, а также, возможно, находящаяся на картах расширения, требует регенерации — периодического обновления (refresh) всех строк матрицы. На системной плате всегда имеется контроллер регенерации памяти, в задачу которого входит регулярный перебор строк памяти с формированием специального цикла регенерации. Каждые 15 мкс контроллер регенерации формирует цикл регенерации (сигнал REFRESH).

2) MASTER — запрос от устройства, использующего 16-битный канал DMA на управление шиной. При получении подтверждения DACK [5:7] Bus-Master может захватить шину.

Можно организовать многопроцессорную систему.

,

,  - чтение/запись (БП)

- чтение/запись (БП) - чтение/запись (УВВ)

- чтение/запись (УВВ)