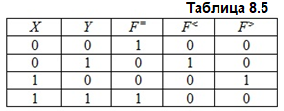

Число входов цифрового компаратора определяется разрядностью сравниваемых кодов, а на выходе всегда формируется только три сигнала: F = – равенство кодов, F > – если числовой эквивалент первого кода больше эквивалента второго, F < – если числовой эквивалент первого кода меньше числового эквивалента второго кода.

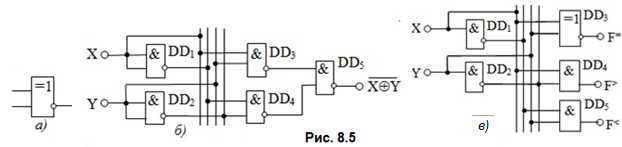

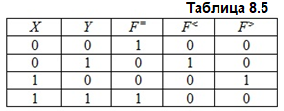

Работу цифрового компаратора при сравнении двух одноразрядных кодов X и Y поясняет таблица истинности (табл. 8.5).

Анализ табл. 8.5 показывает, что при любой комбинации входных сигналов на выходе компаратора может быть сформирован только один активный (например, единичный) логический сигнал. Поэтому при любой разрядности входных кодов достаточно сформировать только любые два из трех выходных сигналов. Третий сигнал всегда может быть получен из двух известных сигналов.

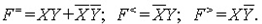

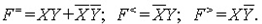

Приведенной табл. 8.5 соответствует следующая система ФАЛ:

Из анализа полученных ФАЛ следует, что для уменьшения аппаратных затрат на реализацию компаратора удобнее всего первоначально получить значения F < и F >, а F = реализовать как их функцию.

Из анализа полученных ФАЛ следует, что для уменьшения аппаратных затрат на реализацию компаратора удобнее всего первоначально получить значения F < и F >, а F = реализовать как их функцию.

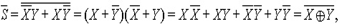

Выражение в цифровой технике имеет самостоятельное значение, это операция исключающее ИЛИ-НЕ или инверсия сложения по модулю два, условное обозначение которой

Выражение в цифровой технике имеет самостоятельное значение, это операция исключающее ИЛИ-НЕ или инверсия сложения по модулю два, условное обозначение которой

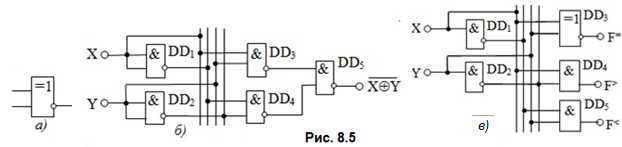

На рис. 8.5 б показана логическая схем а реализации этой операции на элементах 2И-НЕ с учетом условного обозначения элемента инверсии сложения по модулю два (см. рис. 8.5 а), а на рис. 8.5 в представлена комбинационная логическая схема одноразрядного компаратора.

ВЫПОЛНЕНИЕ МАТЕМАТИЧЕСКИХ ОПЕРАЦИЙ

Выполнение операции сложения бинарных чисел

Основными математическими операциями, выполняемыми в ЭВМ на аппаратном уровне, являются операции сложения и вычитания. Операции умножения и деления обычно выполняются посредством аппаратных средств первых двух операций.

Для выполнения операции сложения применяют комбинационные устройства – сумматоры (СМ), логические схемы которых определяются соответствующими таблицами истинности. Отметим, что разрядность выходного слова сумматора всегда принимается на один разряд больше разрядности слов слагаемых для формирования сигнала переноса в старший разряд.

Составим таблицы истинности, описывающие алгоритмы сложения младшего (табл. 8.6) и старших разрядов (табл. 8.7) двоичного кода, отличие которых состоит в наличии или в отсутствии входного сигнала переноса у младшего (первого) разряда и в его наличии у старших разрядов.

В табл. 8.6 и табл. 8.7 обозначено: X и Y – разряды слагаемых; S – разряд суммы; p -1 – разряд переноса из младшего разряда; p – разряд переноса в старший разряд.

Функции алгебры логики, соответствующие табл. 8.6, имеют вид:

Заметим, что для получения разряда суммы над слагаемыми Х и Y необходимо выполнить операцию исключающего ИЛИ. Действительно,

т.е. инверсия от суммы S определяется тем же выражением, что и функция F = в цифровом компараторе.

Устройство, реализующее данный алгоритм работы, называют полусумматором. Его условное изображение (а) и схема (б) приведены на рис. 8.6.

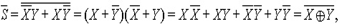

ФАЛ для табл. 8.7 имеет более сложный вид:

Отметим, что в этом случае для получения разряда суммы необходимо два раза выполнить операцию исключающее ИЛИ-НЕ: сначала над слагаемыми, а затем над полученным результатом и разрядом переноса из младшего разряда.

Устройство, реализующее данный алгоритм работы, называют одноразрядным сумматором, условное обозначение и логическая схема которого приведены на рис. 8.6 в и на рис. 8.6 г.

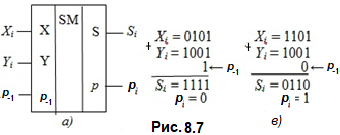

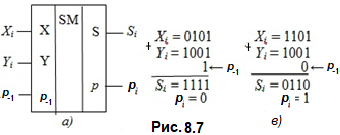

Упражнение 1. Выполним сложение 4-разрядных двоичных чисел Х = 01012 и Y = 10012 при p -1 = 1 (перенос из младшего разряда, рис. 8.7 а), и чисел Хi = 11012 и Yi = 10012 при p -1 = 0.

Решение. 1. Известно, что числа в любой позиционной системе счисления складываются поразрядно с учётом возможного переноса единицы из соседнего младшего разряда. Так, при суммировании 4-разрядных бинарных чисел Хi и Yi при p -1 = 1 получим на выходе сумматора SM сумму Si = 11112 и перенос pi = 0 (рис. 8.7 б).

2. При суммировании же второй пары 4-разрядных бинарных чисел Хi и Yi при p -1 = 0 получим на выходе сумматора SM сумму Si = 01102 и перенос pi = 1 (рис. 8.7 в).

Из анализа полученных ФАЛ следует, что для уменьшения аппаратных затрат на реализацию компаратора удобнее всего первоначально получить значения F < и F >, а F = реализовать как их функцию.

Из анализа полученных ФАЛ следует, что для уменьшения аппаратных затрат на реализацию компаратора удобнее всего первоначально получить значения F < и F >, а F = реализовать как их функцию. Выражение в цифровой технике имеет самостоятельное значение, это операция исключающее ИЛИ-НЕ или инверсия сложения по модулю два, условное обозначение которой

Выражение в цифровой технике имеет самостоятельное значение, это операция исключающее ИЛИ-НЕ или инверсия сложения по модулю два, условное обозначение которой