Кормораздатчик мобильный электрифицированный: схема и процесс работы устройства...

Индивидуальные и групповые автопоилки: для животных. Схемы и конструкции...

Кормораздатчик мобильный электрифицированный: схема и процесс работы устройства...

Индивидуальные и групповые автопоилки: для животных. Схемы и конструкции...

Топ:

Методика измерений сопротивления растеканию тока анодного заземления: Анодный заземлитель (анод) – проводник, погруженный в электролитическую среду (грунт, раствор электролита) и подключенный к положительному...

Оснащения врачебно-сестринской бригады.

Теоретическая значимость работы: Описание теоретической значимости (ценности) результатов исследования должно присутствовать во введении...

Интересное:

Лечение прогрессирующих форм рака: Одним из наиболее важных достижений экспериментальной химиотерапии опухолей, начатой в 60-х и реализованной в 70-х годах, является...

Как мы говорим и как мы слушаем: общение можно сравнить с огромным зонтиком, под которым скрыто все...

Уполаживание и террасирование склонов: Если глубина оврага более 5 м необходимо устройство берм. Варианты использования оврагов для градостроительных целей...

Дисциплины:

|

из

5.00

|

Заказать работу |

|

|

|

|

Контрольная работа

по курсу: "Информационные технологии в проектировании ИМС"

Тема: Средства функциональной верификации компании Mentor Graphics.

Минск 2014

Содержание

Введение

. Исследование и верификация системы на архитектурном и алгоритмическом уровне

. Программно-аппаратная верификация на уровне RTL

. Верификация аппаратной части на уровне RTL

. Аппаратная эмуляция

. Формальная верификация (контроль эквивалентности)

. Аналоговое и смешанное моделирование систем на кристалле

Литература

Введение

Компания Mentor Graphics входит в мировую элиту поставщиков САПР электронных систем. Диапазон предлагаемых средств проектирования чрезвычайно широк и охватывает все основные направления проектирования: проектирование СБИС, печатных плат, систем - от концептуального уровня до выдачи технологических файлов для производства. В данном материале рассматривается комплекс средств функциональной верификации СБИС Mentor Graphics, анализируются основные принципы и методы верификации, заложенные в этих средствах.

В настоящее время проблема функциональной верификации СБИС приобретает доминирующее значение в общем цикле разработки и верификации электронных изделий. По последним данным примерно половина всего инженерного состава, работающего над крупными проектами, занята функциональной верификацией. Временные затраты на функциональную верификацию в общем цикле проектирования выглядят еще более впечатляюще - более 60%. При этом подавляющее большинство ошибок относится к классу логических (функциональных) ошибок [1].

Компания Mentor Graphics была одной из первых, кто в полной мере осознал решающее значение функциональной верификации в современных маршрутах проектирования. Несколько лет назад в компании было создано специальное подразделение Design Verification and Test Division, которое сосредоточило усилия исключительно на данной проблеме. В результате была разработана комплексная платформа верификации, которая получила название Scalable Verification (“Масштабируемая Верификация”) [2], [3]. В основу платформы были заложены три базовых принципа [4]:

|

|

Комплексная верификация систем на кристалле с учетом трех основных составляющих: цифровые подсистемы, аналоговые подсистемы, встроенное программное обеспечение. Все модули платформы верификации интегрированы как по вертикали, охватывая все стадии проектирования - от системного до вентильного уровня, так и по горизонтали, обеспечивая совместное моделирование на одном уровне блоков проекта, представленных разными уровнями абстракции и разными составляющими - цифровой, аналоговой и программной частью.

Ориентация на общепринятые стандарты языков описания проекта, позволяющая не только обмениваться проектными файлами между различными маршрутами проектирования, но и повторно использовать ранее разработанные функциональные блоки и, что еще более важно, тестбенчи. К основным стандартам можно отнести такие языки, как VHDL, Verilog 2001, SystemC, SystemVerilog, PSL.

Использование методологии, получившей название Design for Verification (“Проектирование для Верификации”), включающей все основные методы повышения эффективности верификации: верификация с помощью ассертов (Assertion-Based Verification), верификация, управляемая полнотой функционального покрытия (Coverage-Driven Verification), автоматизация тестбенчей (Testbench Automation), моделирование на уровне транзакций (Transaction Level Modeling) и другие.

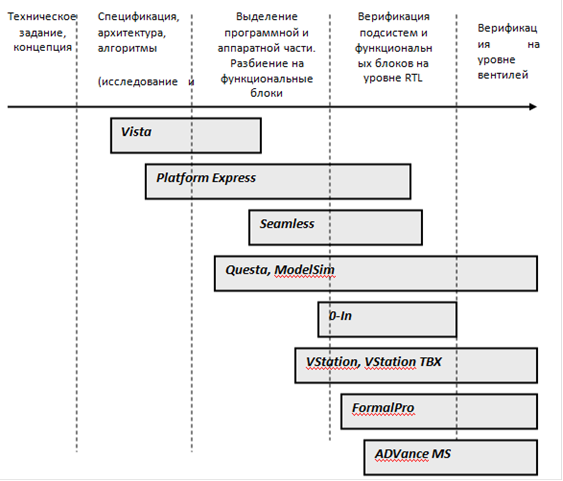

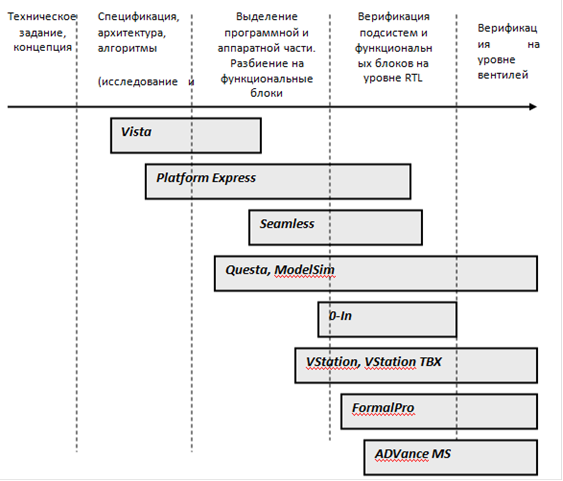

На рисунке 1 представлена схема последовательных этапов проектирования системы на кристалле и перечень средств верификации Mentor Graphics, являющихся составной частью платформы Scalable Verification, с указанием того, на каких этапах проектирования может применяться каждое из этих средств. Рассмотрим кратко назначение и основные характеристики перечисленных средств верификации, уделив особое внимание пакету Questa, который, как видно из рисунка, является ядром комплексной платформы верификации.

|

|

Рисунок 1 - Схема последовательных этапов проектирования системы на кристалле и перечень средств верификации Mentor Graphics

Аппаратная эмуляция

В случае, если необходимо верифицировать весь кристалл на уровне RTL или даже на вентильном уровне, и объем тестов чрезвычайно велик (например, в случае регрессионного тестирования на вентильном уровне) применяются системы аппаратной эмуляции. Система эмуляции 6-ого поколения компании Mentor Graphics - VStation Pro [7] поддерживает максимальный объем проекта 120 млн. вентилей. Она реализована на FPGA и использует запатентованную технологию эмуляции Virtual Wires. Скорость эмуляции достигает нескольких МГц, скорость компиляции - более 5 млн. вентилей в час, при любой комбинации форматов входного представления объекта (VHDL/Verilog/RTL/Gate). Отладочная среда приближается по своим возможностям к системе моделирования и обеспечивает 100%-ную наблюдаемость сигналов. В режиме внутрисхемной эмуляции (in-circuit emulation) VStation Pro оперирует практически в режиме реального времени. Система поддерживает интеграцию с Seamless и Questa/ModelSim. Опция VStation TBX обеспечивает многократное ускорение процесса верификации за счет компиляции тестбенчей, написанных на языках высокого уровня в систему VStation Pro, поддерживая VHDL, Verilog, SystemC, SystemVerilog, TLM. VStation TBX имеет встроенную библиотеку описания протоколов на уровне транзакций и интегрирована с Seamless и Quetsa/ModelSim.

Литература

1. 2004 IC/ASIC Functional Verification Study // Collet International Research, 2004.

2. Brian Bailey The Need for a Scalable Verification Methodology to Overcome the Limitations of Current Verification Approaches // Mentor Graphics White Paper, 2004.

3. А.Л. Лохов Функциональная верификация СБИС // Электроника: Наука, Технология, Бизнес, 1/2004.

4. Ping Yeung Four Pillars of Assertion-Based Verification // Euro DesignCon, 2004.

. Assertion-Based Verification V2.3 User Guides, 0-In Design Automation, 2004.

. Mitch Dale, “The Value of Hardware Emulation”, Mentor Graphics White Paper, 2003.

. Ian Burgess Gate-Level Functional verification is Imperative and Equivalence Checking Provides the Solution // Mentor Graphics White Paper, 2004.

. Rami Ahola, et al. BlueTooth Transceiver Design with VHDL-AMS // Mentor Graphics Deep Submicron Technical Publication”, 2003.

Контрольная работа

по курсу: "Информационные технологии в проектировании ИМС"

|

|

Тема: Средства функциональной верификации компании Mentor Graphics.

Минск 2014

Содержание

Введение

. Исследование и верификация системы на архитектурном и алгоритмическом уровне

. Программно-аппаратная верификация на уровне RTL

. Верификация аппаратной части на уровне RTL

. Аппаратная эмуляция

. Формальная верификация (контроль эквивалентности)

. Аналоговое и смешанное моделирование систем на кристалле

Литература

Введение

Компания Mentor Graphics входит в мировую элиту поставщиков САПР электронных систем. Диапазон предлагаемых средств проектирования чрезвычайно широк и охватывает все основные направления проектирования: проектирование СБИС, печатных плат, систем - от концептуального уровня до выдачи технологических файлов для производства. В данном материале рассматривается комплекс средств функциональной верификации СБИС Mentor Graphics, анализируются основные принципы и методы верификации, заложенные в этих средствах.

В настоящее время проблема функциональной верификации СБИС приобретает доминирующее значение в общем цикле разработки и верификации электронных изделий. По последним данным примерно половина всего инженерного состава, работающего над крупными проектами, занята функциональной верификацией. Временные затраты на функциональную верификацию в общем цикле проектирования выглядят еще более впечатляюще - более 60%. При этом подавляющее большинство ошибок относится к классу логических (функциональных) ошибок [1].

Компания Mentor Graphics была одной из первых, кто в полной мере осознал решающее значение функциональной верификации в современных маршрутах проектирования. Несколько лет назад в компании было создано специальное подразделение Design Verification and Test Division, которое сосредоточило усилия исключительно на данной проблеме. В результате была разработана комплексная платформа верификации, которая получила название Scalable Verification (“Масштабируемая Верификация”) [2], [3]. В основу платформы были заложены три базовых принципа [4]:

Комплексная верификация систем на кристалле с учетом трех основных составляющих: цифровые подсистемы, аналоговые подсистемы, встроенное программное обеспечение. Все модули платформы верификации интегрированы как по вертикали, охватывая все стадии проектирования - от системного до вентильного уровня, так и по горизонтали, обеспечивая совместное моделирование на одном уровне блоков проекта, представленных разными уровнями абстракции и разными составляющими - цифровой, аналоговой и программной частью.

|

|

Ориентация на общепринятые стандарты языков описания проекта, позволяющая не только обмениваться проектными файлами между различными маршрутами проектирования, но и повторно использовать ранее разработанные функциональные блоки и, что еще более важно, тестбенчи. К основным стандартам можно отнести такие языки, как VHDL, Verilog 2001, SystemC, SystemVerilog, PSL.

Использование методологии, получившей название Design for Verification (“Проектирование для Верификации”), включающей все основные методы повышения эффективности верификации: верификация с помощью ассертов (Assertion-Based Verification), верификация, управляемая полнотой функционального покрытия (Coverage-Driven Verification), автоматизация тестбенчей (Testbench Automation), моделирование на уровне транзакций (Transaction Level Modeling) и другие.

На рисунке 1 представлена схема последовательных этапов проектирования системы на кристалле и перечень средств верификации Mentor Graphics, являющихся составной частью платформы Scalable Verification, с указанием того, на каких этапах проектирования может применяться каждое из этих средств. Рассмотрим кратко назначение и основные характеристики перечисленных средств верификации, уделив особое внимание пакету Questa, который, как видно из рисунка, является ядром комплексной платформы верификации.

Рисунок 1 - Схема последовательных этапов проектирования системы на кристалле и перечень средств верификации Mentor Graphics

|

|

|

История развития хранилищ для нефти: Первые склады нефти появились в XVII веке. Они представляли собой землянные ямы-амбара глубиной 4…5 м...

Архитектура электронного правительства: Единая архитектура – это методологический подход при создании системы управления государства, который строится...

Таксономические единицы (категории) растений: Каждая система классификации состоит из определённых соподчиненных друг другу...

История развития пистолетов-пулеметов: Предпосылкой для возникновения пистолетов-пулеметов послужила давняя тенденция тяготения винтовок...

© cyberpedia.su 2017-2024 - Не является автором материалов. Исключительное право сохранено за автором текста.

Если вы не хотите, чтобы данный материал был у нас на сайте, перейдите по ссылке: Нарушение авторских прав. Мы поможем в написании вашей работы!