Перенос проекта начинается со стандартных действий, а именно – создание проекта в среде Xilinx Vivado, но при выборе типа проекта (рисунок 1.2) необходимо указать, что это будет импорт проекта из другой среды (Imported Project).

Когда программа попросит указать путь к проекту Xilinx ISE, необходимо указать на файл с расширением «.xise», находящийся в папке проекта (рисунок 2.11).

Рисунок 2.11 – Меню импорта проекта

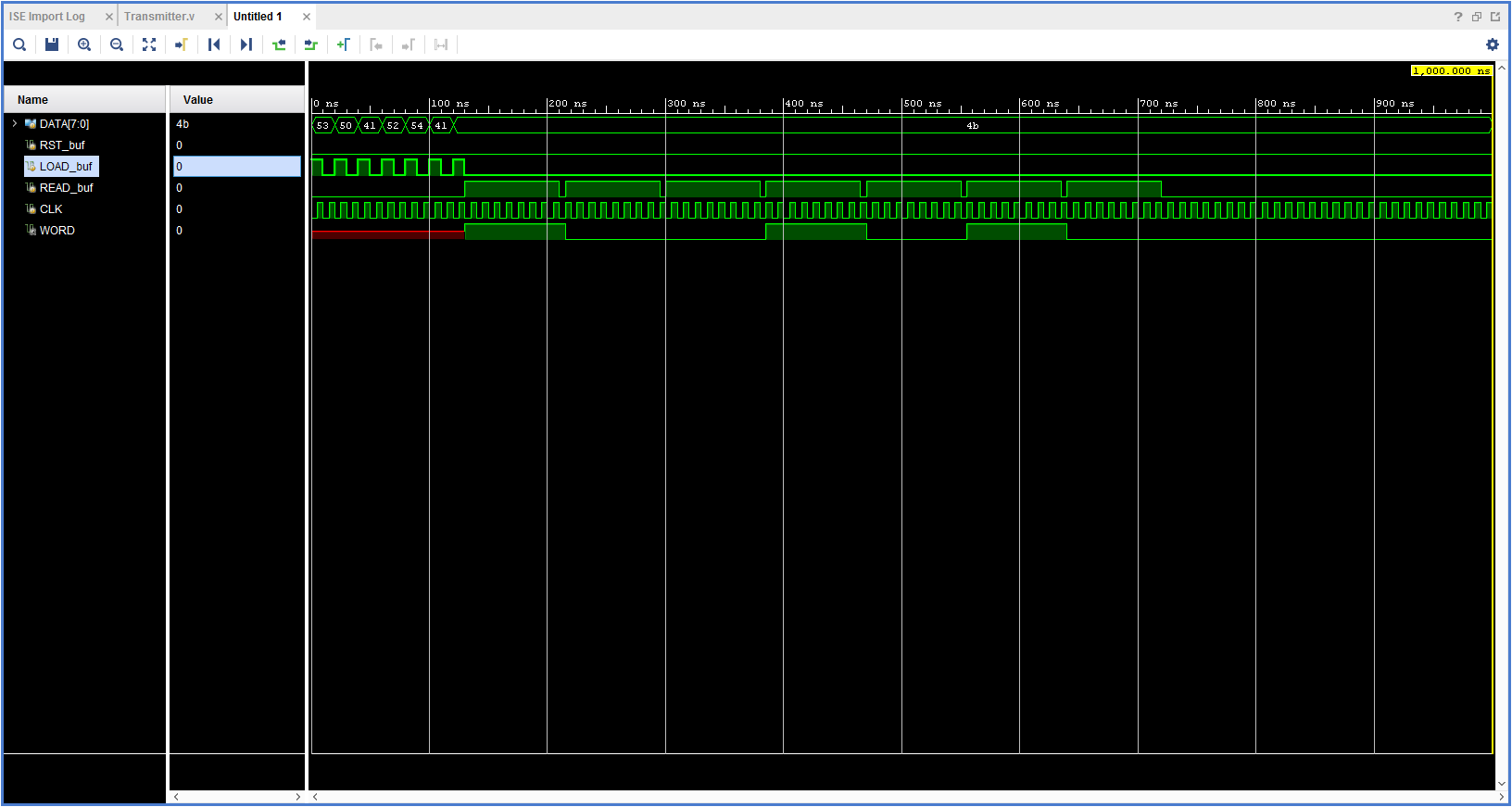

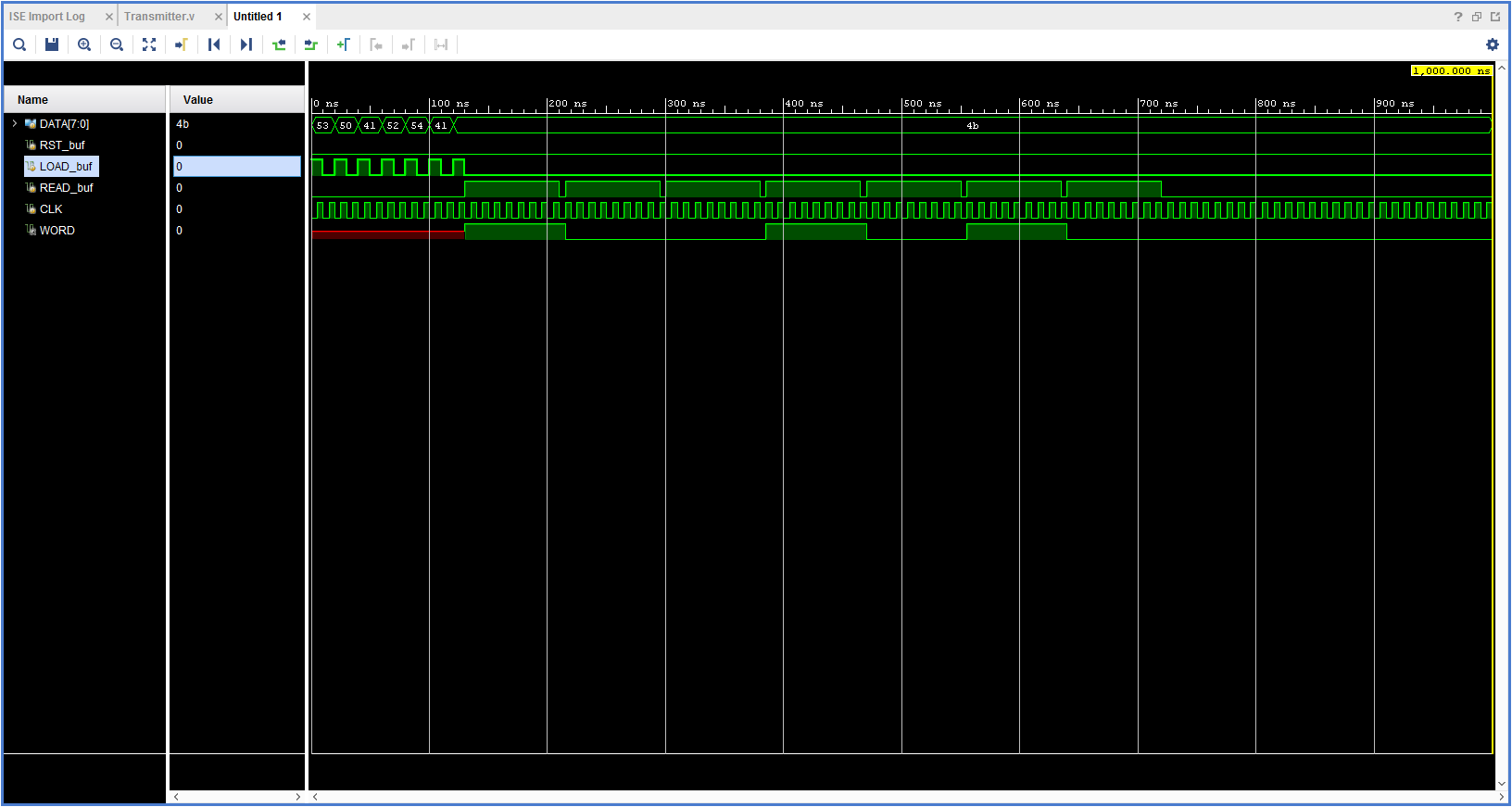

После успешного импорта проекта можно просмотреть лог. В данной работе, для наглядности произведем запуск симуляции еще раз (рисунок 2.12).

Рисунок 2.12 – Симуляция импортированного проекта из среды Xilinx ISE

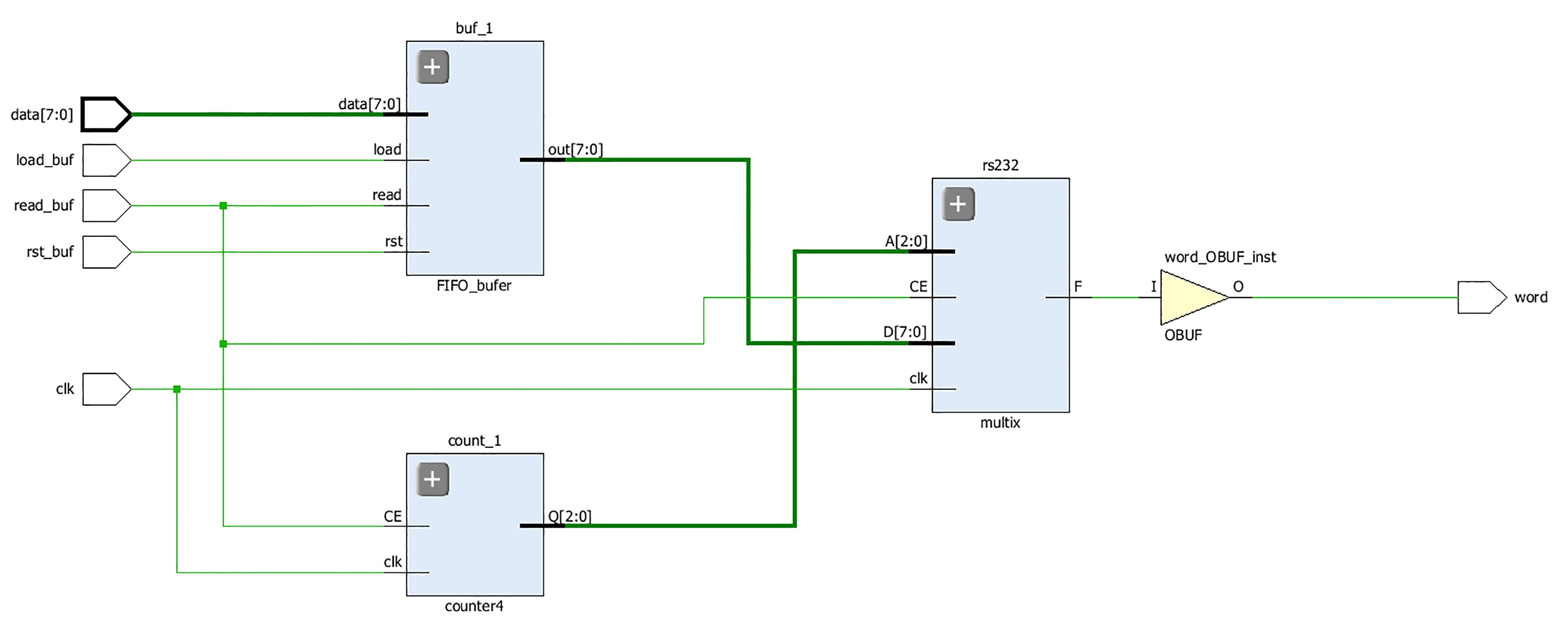

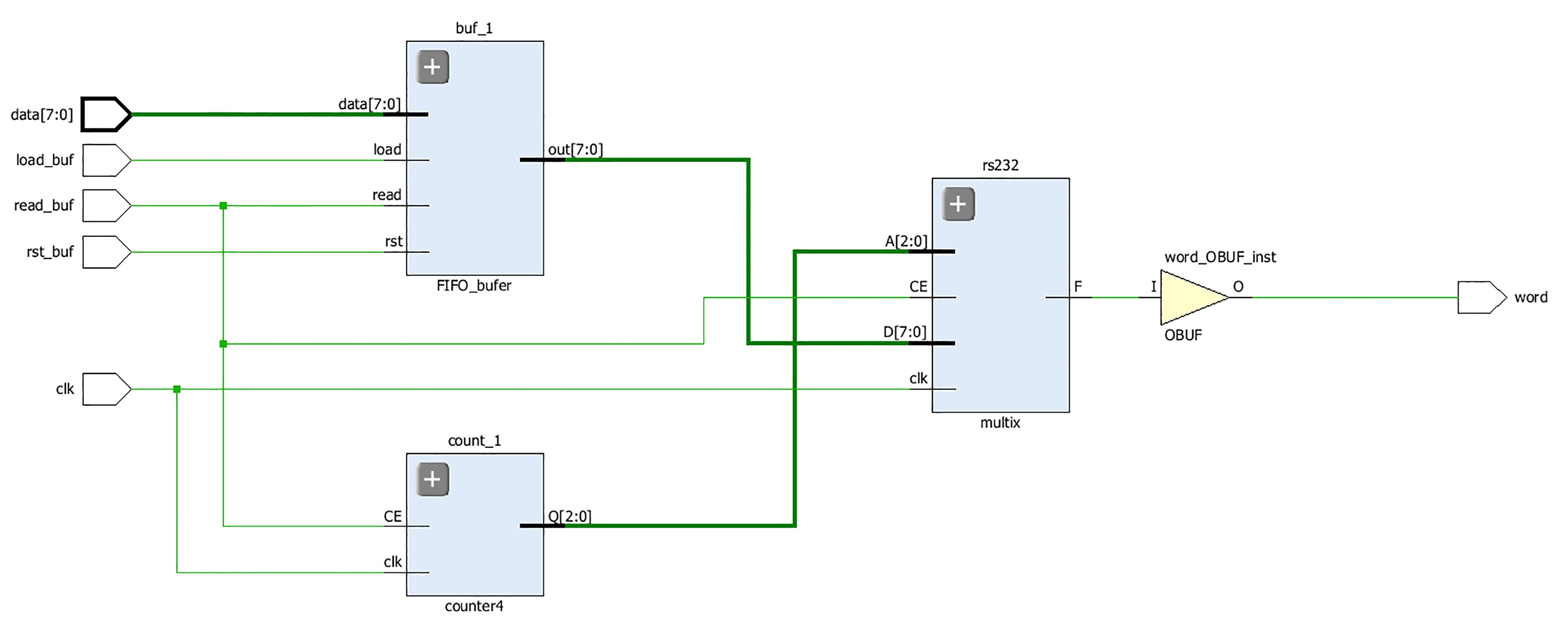

Так же можно просмотреть схему модуля, воспользовавшись меню «Flow Navigator», в разделе «RTL Analysis».

Рисунок 2.13 – Схема модуля на основе импортированного кода

ЗАКЛЮЧЕНИЕ

В ходе выполнения работы были изучены среды программирования Vivado и ISE от фирмы Xilinx.

С помощью САПР Vivado была построена модель работы дешифратора.

С помощью САПР ISE, была построена модель работы асинхронного интерфейса RS-232, состоящего из таких модулей, как: дешифратор, мультиплексор, счетчик, буфер. Затем, данный проект был импортирован в среду Xilinx Vivado.

Был получен ценный опыт написания тестовых модулей и проверки с их помощью работоспособности моделей, а также синтезирования готовых схем на основе готового кода.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

1. Основы HDL Verilog как средства проектирования цифровых устройств [интернет-источник] https://emirs.miet.ru/oroks-miet/upload/POPOVA.pdf (дата обращения 10.05.2019).

2. Основы верификации и отладки ПЛИС [интернет-источник] https://www.macrogroup.ru/sites/default/files/uploads/files_and_docs/prezent/otladka_plis_webinar.pdf (дата обращения 10.05.2019).

ПРИЛОЖЕНИЕ А

ТЕКСТ ПРОГРАММЫ ДЕШИФРАТОРА

И ТЕСТОВОГО МОДУЛЯ

module Decoder _1(

input [2:0] A, //трехразрядная шина входа А

Input EN, //разрешающий вход

output [7:0] X //восьмиразрядный выход X

);

//входы и выходы по умолчанию объявлены как переменные типа wire

reg [7:0] X; //выход хранит значения, по этому должен быть типа reg

always @* //при любом изменении сигналов

Begin

//только при разрешении работы

If (EN)

Begin

X =0; //обнулить шину

X [ A ]=1; //А-тому разряду положить "1"

End

End

Endmodule

module Testbench_1;

//!Тестбенч не имеет входных и выходных параметров.

//После объявления модуля описываются переменные

//с которыми работает тестбенч

reg [2:0] A;

reg EN;

wire [7:0] X;

//зетем объявляется объект класса decoder

Decoder _1 dc _1(A, EN, X);

Initial

Begin

A=2;

EN=1;

#5;

A=3;

#4;

A=7;

#9;

EN=0;

A=0;

#7

EN=1;

#6

A=5;

End

Endmodule

module Decoder_2(

input [2:0] A,

Input EN,

output [7:0] X

);

Genvar i; //объявление переменной для блока генерации

//начало области генерации

Generate

//цикл по переменной i, определяющей число выходных

//разрядов модуля

for(i = 0;i < 8;i = i+1)

Begin

//если работа разрешена

// и входной операнд равен номеру выхода

//присвоить выходному разряду (X [ i ]) 1 иначе(?) 0

assign X[i]=EN & A==I? 1:0;

End

Endgenerate

Endmodule

module Testbench_2();

wire [7:0] x;

reg en;

reg [2:0] a;

Decoder_2 dc_2(.a(a),.en(en),.x(x));

Initial

Begin

en = 0;

a = 0;

#5

en = 1;

Forever

#5

a = a+1;

#50

$finish;

End

Endmodule

ПРИЛОЖЕНИЕ Б