| Символ

| Позиция

| Имя и назначение

|

| ЕА

| IE.7

| Снятие блокировки прерывания. Сбрасывается, программно для запрета всех прерываний независимо от состояний IE.4–IE.0

|

|

| IE.6

| Не используется

|

|

| IE.5

| Не используется

|

| ES

| IE.4

| Бит разрешения прерывания, от приемопередатчика Установка/сброс программой для разрешения/запрета прерываний от флагов TI или RI

|

| ЕТ1

| IE.3

| Бит разрешения прерывания от таймера. Установка/сброс программой для разрешения/запрета прерываний от таймера 1

|

| ЕХ1

| IE.2

| Бит разрешения внешнего прерывания 1. Установка/сброс программой для разрешения/запрета прерывания 1

|

| ЕТО

| IE.1

| Бит разрешения прерывания от таймера 0. Установка/сброс программой для разрешения/запрета прерываний от таймера 0

|

| ЕХО

| IE.0

| Бит разрешения внешнего прерывания 0. Установка/сброс программой для разрешения/запрета прерывания 0

|

Во встроенной области памяти данных с адреса 08h по начальному сбросу процессора размещается стек (ячейки стека адресуются восьмиразрядным указателем SP, который может быть загружен программно иным требуемым адресом размещения стековой области).

В шестнадцати ячейках встроенной области памяти данных (с адреса 20h по 2Fh) предусмотрена прямая битовая адресация.

Адресная область 80h-FFh занята встроенными, специализированными по назначению, регистрами с прямой адресацией доступа, а для части регистров и прямой адресацией доступа к их битам. Регистры специализированы по назначению для внешнего обмена данными (порты), для адресации ячеек дополнительной внешней памяти (в процессоре предусмотрены команды, инициирующие управление передачу и приём для работы дополнительной внешней памятью данных), для управления внутренними настройками процессора. Специализированные регистры ОМЭВМ разработчиками процессора названы «регистрами специальных функций (РСФ)». Знаком «*» на рис. 9.3 отмечены РСФ с битовой адресацией.

Встроенная память программ ОМЭВМ i80´51 имеет объём 4kб. Предусмотрены технические возможности блокировки обращений во встроенную память программ и разрешения выборки из внешней дополнительной памяти программ. В ОМЭВМ К1816ВЕ31 (отечественный аналог ОМЭВМ i80´31) стенда УС-51 встроенная память программ отсутствует и ОМЭВМ в составе стенда работает с внешней совмещенной оперативной памятью для команд программ и данных. Адресное пространство совмещённой памяти учебного стенда представлено областью 1000h-17FFh, 1800h-1FFFh для хранения программ и данных пользователя и областью 0000-0FFFh, занятой программой «Монитор» и другими служебными программами стенда.

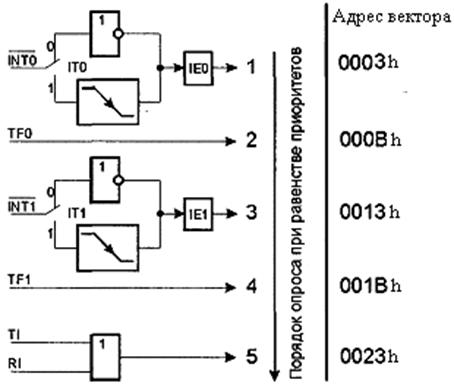

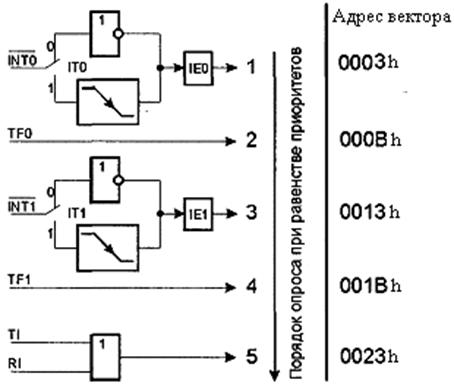

В работе учитывается спецификация векторов прерывания базового процессора i8051, показанная на рис. 9.4.

Рис. 9.4. Спецификация прерываний процессора i8051

Области прерываний с векторами 0003h и 0013h используются в стенде для собственных нужд, а области прерываний с векторами 000Вh, 001Вh, 0023 доступны для применения в программах приложений разрабатываемых пользователями стенда.

Подпрограмма обслуживания прерывания с входа INT0 (вектор 0003h) от встроенных кнопок имитации внешних прерываний I0,T0 размещена с адреса 26h нулевой страницы памяти программ.

Подпрограмма обслуживания прерывания с входа INT1 (вектор 0013h) от встроенного контроллера клавишного модуля и сегментного дисплея ОЭВМ размещена с адреса 02F1h.

Так как адресное пространство 0000-0FFFh, занято программой «Монитор» и другими служебными программами стенда, то начальные адреса программ обслуживания прерываний с векторами 000Вh, 001Вh, 0023 (от таймеров и встроенного модуля последовательного обмена данными с внешними устройствами) для программирования задач пользователя стенда переадресованы в область ОЗУ программ пользователя в следующем соответствии:

– прерывания со входа TF0 (000Bh на адрес 1753h);

– прерывания со входа TF1 (001Bh на адрес 1759h);

– прерывания со входа T1, R1 (0023h на адрес 175Ch).

Адрес области обработчика прерывания со входа TF0 соответствуют прерыванию от таймера T/C0 и, с учётом указанной выше переадресовки, начало программы обслуживания этого прерывания должно размещаться с адреса 1753h.

При подготовке программ учитывается специфика размещения кодов в ячейках памяти. Архитектурой процессора i8051 предусмотрено размещение трёхбайтовых команд в памяти программ последовательностью «код операции – старший байт числа команды – младший байт числа команды» (в отличие от принятой в для процессоров i8080, i8085, i8086 и их развитий). Принятая для стенда УС-51 спецификация приоритетов прерываний при подготовке программы управления по заданию не изменялась.

Программа управления

В соответствии с заданием на работу подготовлена программа управления, листинг которой представлен (алгоритм функционирования исполнители работы должны представить самостоятельно в отчёте).

Входными параметрами программы являются коды первого числа Х1=74h, которое должно быть набрано на переключателях SA8–SA1 стенда в прямом коде до запуска программы на исполнение и второго числа

Х2 = (принято 11h), которое должно быть установлено в течение первой паузы (в программе 10 с).

Выходными параметрами программы являются состояния индикаторов HL8–HL1 в соответствии с условиями задания.

Для достижения указанной длительности паузы таймер настраивается на 50000 счётных операций при длительности одной операции 2 мкс, что соответствует длительности счёта 0,1 с. Для счёта до 50000 в регистры TH0, TL0 следует загрузить число 1553610 (3CB0h). В программе в строке 5 установлен счётчик повтора таймерного цикла 100 раз. Настройка режима таймера, загрузка его счётчиков числом счётных операций, запуск счёта, разрешение прерывания от выбранного таймера и проверка завершения счёта таймерных циклов выполнены в основной программе управления. Обслуживание таймера сводится к перезагрузке счётчиков таймера и коррекции декрементом содержимого счётчика числа таймерных циклов.

При составлении программы учтены ограничения, связанные с архитектурой и процессора и учебного стенда.

Настройка режима таймера TMOD–11h. Статус TCON – битовая операция – «Разрешить счёт (set TR0)» / «Блокировать счёт (clr TR0)». Управление прерываниями – битовая операция – «Разрешить прерывание (set ET0)» / «Блокировать прерывание (clr ET0)». Загрузка старшего байта счёта в таймере -3C. Загрузка младшего байта счёта в таймере – B0.

Листинг программы:

1000 75 90 FF mov P1,# FF; очистка буфера порта P1

1003 E5 90 mov A, P1; ввод с порта P1

1005 B4 76 3D cjne A,#76, 3D;проверка Х1=74

1008 75 90 01 mov P1,#01; включение HL1

100b 74 64 mov A,#64; настройка числа повторов циклов

таймера в первой паузе

100d 75 89 11 mov TMOD, #11; таймер 0 в режим 1

1010 75 8C 3C mov TH0,# 3C; загрузка таймера 0

1013 75 8A B0 mov TL0,# B0;

1016 D2 8C set TR0; разрешение счёта таймера 0

1018 D2 A9 set ET0; разрешение прерываний от таймера 0

101a B4 00 fd cjne A,#00, FD; контроль завершения первой паузы 10 сек

101d C2 8C clr TR0; блокировка счёта импульсов в таймер 0

101f C2 A9 clr ET0; блокировка прерывания от таймера

1021 75 90 FF mov P1,# FF; очистка буфера порта

1024 E5 90 mov A, P1; ввод с порта

1026 B4 11 27 cjne A,#11, 27; проверка Х2=11

1029 F 5 90 mov P1,A; вывод Х2 для индикации

102b 74 C0 mov A,#C0; настройка числа циклов

; таймера 0 во второй паузе

102d 75 8C 3С mov TH0,# 3С; загрузка таймера 0

1030 75 8A B0 mov TL0,# B0;

1033 D2 8C set TR0; разрешение счёта

1035 D2 A9 set ET0; разрешение прерываний от таймера 0

1037 B4 00 FD cjne A,#00, FD; контроль завершения второй паузы 12 сек

103a C2 8C clr TR0; блокировка счёта импульсов в таймере 0

103c C2 A9 clr ET0; блокировка прерывания от таймера

103e 75 90 80 mov P1,#80; включение HL8 (оба числа опознаны)

1041 02 10 41 ljmp 1041; «пустой» цикл

1045 75 90 40 mov P1,#40; включение HL7 (неправильный набор Х1)

1048 02 10 48 ljmp 1048; «пустой» цикл

1050 75 90 20 mov P1,#20; включение HL6 (неправильный набор Х2)

1053 02 10 53 ljmp 1053; «пустой» цикл

1753 02 10 56 ljmp 1056; промежуточный переход к обработке

; прерывания от таймера Т0

Обработка прерывания:

1056 C2 8C clr TR0; блокировка подачи импульсов в таймер 0

1058 75 8C 3C mov TH0,# 3C; загрузка таймера 0 (ст. байт)

105b 75 8A B0 mov TL0,# B0; младший байт

105e 14 dec A; счёт повторов циклов таймера

105f D2 8C set TR0; разрешение счёта

1061 32 reti; возврат из прерывания по таймеру.

Адреса программы управления и обработчика прерывания через ячейку 1753h приведены в листинге.

Объём программы – 91 байт.

Время выполнения программы определяется длительностью двух таймерных пауз.