1. Реализация простых логических функций. Задание:

1.1. На основании определения логических операций НЕ (инверсии), И (коньюнкции), ИЛИ (дизъюнкции) заполните табл.1.1.

Таблица 1.1.

| Входные переменные

| Значение выходных функций F

|

| А

| В

| С

| НЕ А

| И

| И-НЕ

| ИЛИ

| ИЛИ-НЕ

|

|

|

|

| | | | | |

|

|

|

| | | | | |

|

|

|

| | | | | |

|

|

|

| | | | | |

|

|

|

| | | | | |

|

|

|

| | | | | |

|

|

|

| | | | | |

|

|

|

| | | | | |

1.2. Нарисуйте принципиальные схемы для реализации функций  ,

,  ,

,  ,

,  ,

,  на логических элементах типа И-НЕ.

на логических элементах типа И-НЕ.

Для функции  соберите нарисованную схему и проверьте, что она выполняет логическую операцию ИЛИ для трех переменных А, В, С.

соберите нарисованную схему и проверьте, что она выполняет логическую операцию ИЛИ для трех переменных А, В, С.

2. Минимизация сложных логических функций и их реализация.

2.1. Пример. Реализуем логическую функцию, представленную в табл. 1.2.

Таблица 1.2.

Остальным комбинациям А, В, С, не указанным в таблице, соответствует значение F=0. Табл. 1.2. соответствует логическое выражение  .

.

По правилам алгебры логики проведем минимизацию функции F. Выносим общий множитель за скобки

Используя очевидное соотношение  , можем в скобках еще раз повторить любой из членов. Добавим член

, можем в скобках еще раз повторить любой из членов. Добавим член  . Тогда

. Тогда  , но

, но  , поэтому

, поэтому  (1).

(1).

Для реализации выражения (1) с помощью элементов И-НЕ необходимо исключить операцию дизъюнкции, выразив ее по формуле Де Моргана:  .

.

Поэтому  (2)

(2)

Выражение (2) реализуется в схеме (рис.1.2.).

Рис.1.2.

Соберите схему (рис.1.2) и проверьте, что она реализует функцию, заданную в табл.1.2.

2.2. Задание:

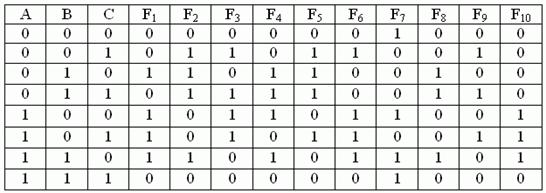

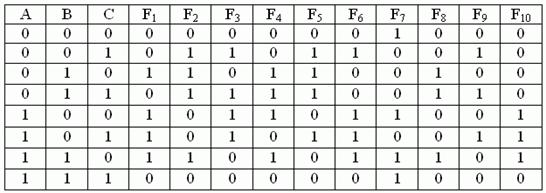

Из табл.1.3 выберите логическую функцию для своего варианта, составьте соответствующее логическое выражение, минимизируйте его и приведите к виду, удобному для схемной реализации.

Из типовых элементов И-НЕ соберите схему и проверьте, что она реализует логическую функцию вашего варианта.

Таблица 1.3.

3. Синтез логических схем.

3.1. Задание:

3.1.1. Синтезируйте и реализуйте схему электронного замка, открываемого (F=1) комбинацией входных сигналов А1А2А3А4, определяющих номер вашего варианта. Например, для варианта 9 замок должен открываться комбинацией 1001.

3.1.2. Синтезируйте и реализуйте схему, моделирующую автомат для голосования на примере трех участников. Алгоритм голосования: решение принято (F=1), когда за него голосует не менее двух человек из трех.

3.1.3. Синтезируйте и реализуйте схему “исключающее ИЛИ” (2 варианта), пользуясь элементами 2И-НЕ схемы К155ЛА3. Первый вариант имеет более простую запись и реализуется на пяти элементах 2И-НЕ, второй более сложную запись, но требует для реализации только 4 элемента.

3.1.4. Синтезируйте и реализуйте схему одноразрядного компаратора, работающего по алгоритму:

F=0, если А1>А2 и F=1, если А1=А2

3.1.5. Синтезируйте и реализуйте схему коммутатора сигналов, работающую по алгоритму: F=В1, если А=1 и F=В2, если А=0.

Здесь А-коммутирующий сигнал, В1,В2-коммутируемые сигналы.

3.1.6. С помощью логического преобразователя подтвердите результаты пп 3.1.4., 3.1.5 (задайте таблицу истинности, на ее основе получите минимизированное логическое выражение и схему устройства только на элементах И-НЕ).

4. Укоротитель импульсов.

4.1. Задание:

4.1.1. Соберите схему (рисунок 1). Зарисуйте осциллограммы в точках А, В, О, D при подаче на вход импульсов от внешнего генератора (соедините канал В осциллографа с выходом D, а к каналу А - поочередно подключите точки А, В, О исследуемой схемы).

Рисунок 1

5. Удлинитель импульсов (одновибратор).

5.1. Задание:

5.1.1. Соберите схему одновибратора (рисунок 2). Подайте на вход одновибратора импульсы от внешнего генератора. Зарисуйте осциллограммы напряжений в точках А, В, О, D.

Рисунок 2

Параметры функционального генератора:

- вид входных сигналов – прямоугольный;

- частота – 50 Гц;

- амплитуда входных сигналов – 10 В;

- скважность – 10%

6. Схема задержки импульсов.

6.1. Задание:

6.1.1. Синтезируйте схему, обеспечивающую выдачу положительных импульсов постоянной длительности, сдвинутых относительно коротких отрицательных импульсов на некоторое время t. Для этого воспользуйтесь схемами 1 и 2. Постройте диаграммы для характерных точек схемы.

6.1.2. Соберите синтезированную схему и пронаблюдайте ее работу.

Содержание отчета.

7.1. Результаты выполнения п. 1.1, 1.2.

7.2. Исходное логическое выражение, его минимизация и схемная реализация по п. 2.2.

7.3. Аналогично для п. 3.1.1, 3.1.2, 3.1.3, 3.1.4, 3.1.5.

7.4. Пункт 3.1.6. продемонстрировать при сдаче отчета.

Параметры функционального генератора:

- вид входных сигналов – прямоугольный;

- частота – 50 Гц;

- амплитуда входных сигналов – 10 В

7.5. Схема рис. 1 и результаты п.п. 4.1.1.

7.6. Схема рис. 2 и результаты п.п. 5.1.1.

7.7. Синтезированная схема задержки и результаты п.п. 6.1.1.

Раздел 6. Триггеры

1. Триггеры на логических элементах.

1.1. Асинхронный R-S триггер с инверсными входами.

Соберите схему триггера на логических элементах 2И-НЕ и проверьте таблицу его состояний.

| Таблица 1

|

| tn

| tn+1

|

|

| Qn+1

|

|

|

| |

|

|

| |

|

|

| |

|

|

| |

1.2. Тактируемый (синхронный) R-S триггер

Соберите схему триггера на логических элементах 2И-НЕ и проверьте таблицу его состояний.

| Таблица 2

|

| S

| R

| T

|

|

| Qn+1

|

|

|

|

| | | |

|

|

|

| | | |

|

|

|

| | | |

|

|

|

| | | |

| х

| х

|

| | | |

1.3. D-триггер

Соберите схему триггера на логических элементах 2И-НЕ и проверьте таблицу его состояний.

| Таблица 3

|

| D

| Т

|

|

| Qn+1

|

|

|

| | | |

|

|

| | | |

|

|

| | | |

|

|

| | | |

1.4. Задача: для R-S триггера с инверсными входами даны переменные входные параметры X и Y, изменение которых во времени показано на рис.1. По номеру своего варианта выбрать вид входных сигналов из таблицы:

| № варианта

|

|

|

|

|

|

|

| R

| x

| y

| x

|

|

| y

|

| S

| y

| x

|

| y

| x

|

|

Соберите схему R-S триггера с инверсными входами, подав на входы R и S коды с генератора слова, а на логический анализатор - входы R, S и выходы Q,  . Коды генератора слова следует задавать так: биты S и R соответствуют битам D0 и D1, остальные биты D2…D15 равны 0. Выбрав по номеру варианта последовательность битов R и S для каждого Тшаг, следует записать слово в шестнадцатиричном коде. Таким образом, в генератор слова вводится 10 слов (Tшаг=10).

. Коды генератора слова следует задавать так: биты S и R соответствуют битам D0 и D1, остальные биты D2…D15 равны 0. Выбрав по номеру варианта последовательность битов R и S для каждого Тшаг, следует записать слово в шестнадцатиричном коде. Таким образом, в генератор слова вводится 10 слов (Tшаг=10).

Например, в первом шаге R=0, S=1, следовательно в двоичном коде: 0000.0000.0000.00 01 или в шестнадцатеричном 0001 – первый код генератора слова. Во втором шаге R=1, S=0: 0000.0000.0000.00 10 2 = 0002 16 – второй код генератора слова и т.д.

Получите с помощью логического анализатора временные диаграммы для R, S, Q,  . Зарисуйте их.

. Зарисуйте их.

2. Интегральные триггеры.

2.1. D-триггер 74175 (триггер-защелка).

Выберите из библиотеки Digital интегральную схему D-триггера 74175 (Quad D-type FF (clr))  . Данная интегральная схема содержит четыре двухступенчатых Д-триггера. На выходы 1Q, 2Q, 3Q и 4Q поступает информация с входов 1D, 2D, 3D, и 4D при значении стробсигнала CLK=1 информация “защелкивается”. Сигнал CLR’=0 сбрасывает триггер в исходное состояние. Питание микросхемы: 8 (GND) – общий провод, 16 (VCC)- Uпит.

. Данная интегральная схема содержит четыре двухступенчатых Д-триггера. На выходы 1Q, 2Q, 3Q и 4Q поступает информация с входов 1D, 2D, 3D, и 4D при значении стробсигнала CLK=1 информация “защелкивается”. Сигнал CLR’=0 сбрасывает триггер в исходное состояние. Питание микросхемы: 8 (GND) – общий провод, 16 (VCC)- Uпит.

2.1.1. Задание: Исследуйте поведение триггера, воспользовавшись одним из входов Di и соответствующим выходом Qi. В какой момент происходит защелкивание информации?

Нарисуйте схему подключения ИС 74175 для записи на выходах ее кода Q4Q3Q2Q1=0011. Соберите схему и зафиксируйте на выходах заданный код.

2.2. JK-триггер 7472.

Выберите из библиотеки Digital интегральную схему JK-триггера 7472 (AND-gated JK MS-SLV FF (pre, clr)). Данная интегральная схема содержит: входы - J1, J2, J3, К1, К2, К3; выходы – Q и Q’, а также стробсигнал CLK, сброс – CLR’ и вход предустановки PRE’. Питание микросхемы: 7 – общий провод, 14 - Uпит.

2.2.1. Ознакомьтесь с работой JK-триггера. Запишите таблицу состояний триггера. Какие строчки таблицы соответствуют работе JK-триггера в качестве RS-триггера и Т-триггера?

2.2.2. Задание: Соберите схему включения триггера 7472. На выходы  подключите светодиоды. Проверьте все варианты таблицы состояний. Соберите схему D-триггера на JK-триггере и проверьте ее работу. В качестве инвертора воспользуйтесь соответствующим логическим элементом.

подключите светодиоды. Проверьте все варианты таблицы состояний. Соберите схему D-триггера на JK-триггере и проверьте ее работу. В качестве инвертора воспользуйтесь соответствующим логическим элементом.

Содержание отчета.

3.1. Результаты п. 1.1, 1.2., 1.3., 1.4.

3.2. Схема и результаты п. 2.1.1.

3.3. Таблица п. 2.2.1 и пояснение к ней

,

,  ,

,  ,

,  ,

,  на логических элементах типа И-НЕ.

на логических элементах типа И-НЕ. .

.

, можем в скобках еще раз повторить любой из членов. Добавим член

, можем в скобках еще раз повторить любой из членов. Добавим член  . Тогда

. Тогда  , но

, но  , поэтому

, поэтому  (1).

(1). .

. (2)

(2)

. Коды генератора слова следует задавать так: биты S и R соответствуют битам D0 и D1, остальные биты D2…D15 равны 0. Выбрав по номеру варианта последовательность битов R и S для каждого Тшаг, следует записать слово в шестнадцатиричном коде. Таким образом, в генератор слова вводится 10 слов (Tшаг=10).

. Коды генератора слова следует задавать так: биты S и R соответствуют битам D0 и D1, остальные биты D2…D15 равны 0. Выбрав по номеру варианта последовательность битов R и S для каждого Тшаг, следует записать слово в шестнадцатиричном коде. Таким образом, в генератор слова вводится 10 слов (Tшаг=10).

. Данная интегральная схема содержит четыре двухступенчатых Д-триггера. На выходы 1Q, 2Q, 3Q и 4Q поступает информация с входов 1D, 2D, 3D, и 4D при значении стробсигнала CLK=1 информация “защелкивается”. Сигнал CLR’=0 сбрасывает триггер в исходное состояние. Питание микросхемы: 8 (GND) – общий провод, 16 (VCC)- Uпит.

. Данная интегральная схема содержит четыре двухступенчатых Д-триггера. На выходы 1Q, 2Q, 3Q и 4Q поступает информация с входов 1D, 2D, 3D, и 4D при значении стробсигнала CLK=1 информация “защелкивается”. Сигнал CLR’=0 сбрасывает триггер в исходное состояние. Питание микросхемы: 8 (GND) – общий провод, 16 (VCC)- Uпит. подключите светодиоды. Проверьте все варианты таблицы состояний. Соберите схему D-триггера на JK-триггере и проверьте ее работу. В качестве инвертора воспользуйтесь соответствующим логическим элементом.

подключите светодиоды. Проверьте все варианты таблицы состояний. Соберите схему D-триггера на JK-триггере и проверьте ее работу. В качестве инвертора воспользуйтесь соответствующим логическим элементом.