Цель: Приобретение практических навыков синтеза бинарных счетчиков с произвольным коэффициентом пересчета

Теоретические сведения

Счетчиком называется узел ЭВМ, предназначенный для подсчета числа входных сигналов. Счетчики используются в ЭВМ для образования последовательных адресов команд, для счета количества циклов выполнения операций и т.п.

Счетчики работают в двух режимах: длительном и управляющем.

Длительный режим связан с одним из наиболее частых применений счетчика в качестве делителя частоты. В этом применении не имеет значения соответствие информации, записанной в разрядах счетчика в каждый данный момент, числу поступивших на его вход импульсов – основной задачей счетчика является деление (уменьшение) частоты входных импульсов.

Управляющий режим работы счетчика связан с необходимостью считывания информации о количестве поступивших импульсов после каждого такта события.

При использовании счетчика в качестве делителя частоты допустимая частота счетных импульсов определяется скоростными свойствами первого разряда независимо от вида применяемого поразрядного переноса.

Счетчики подразделяются на суммирующие, вычитающие (нереверсивные) и реверсивные.

Суммирующий счетчик предназначен для выполнения счета в прямом направлении, то есть для сложения. С приходом очередного счетного импульса на вход счетчика, его показание увеличивается на единицу.

Вычитающий счетчик предназначен для выполнения счета в обратном направлении, то есть в режиме вычитания. Каждый счетный импульс, поступивший на вход счетчика, уменьшает его показания на единицу.

Реверсивными называются такие счетчики, которые предназначены для выполнения счета как в прямом, так и в обратном направлении, то есть могут работать в режиме сложения и вычитания.

Счетчики могут быть построены:

- на основе счетных триггеров,

- на основе регистров и кольцевых схем (сдвигающие счетчики),

- на основе многоустойчивых схем.

Основными характеристиками счетчика являются:

- модуль счета или коэффициент пересчета К счетчика,

- быстродействие.

Коэффициент пересчета К характеризует число устойчивых состояний счетчика, то-есть предельное число импульсов, которое может быть сосчитано счетчиком. Например, при К=8 счетчик будет иметь 8 устойчивых состояний и каждый восьмой импульс, поступивший на его вход, будет возвращать счетчик в первоначальное состояние.

Счетный триггер является простейшим счетчиком, осуществляющим подсчет импульсов по модулю 2. Соединив несколько счетных триггеров определенным образом, можно получить схему многоразрядного счетчика

Рис. 8.1 – Асинхронный двоичный счетчик с последовательным переносом

Табл. 8.1 – Состояния счетчика асинхронного двоичного счетчика

Обычно счетчик имеет цепь установки в 0, однако начальное его состояние не обязательно нулевое. Начальное состояние может устанавливаться передачей в счетчик кода некоторого числа и с него уже будет начинаться операция счета единиц. Такой режим характерен, например, при образовании последовательности адресов команд при заданном исходном адресе.

Основной особенностью асинхронного счетчика является зависимость длительности переходного процесса в счетчике от его разрядности. С ростом разрядности счетчика понижается предельная частота его работы. Это объясняется тем, что с ростом разрядности счетчика n будет возрастать задержка поступления сигнала на вход с некоторого j -го разряда относительно времени поступления входного сигнала fcr на вход с младшего разряда счетчика. Такая задержка может привести к искажению информации в счетчике. Для повышения быстродействия счетчики выполняют с параллельным переносом, показанным на рис. 8.2. Схема вычитающего счетчика приведена на рис. 8.3.

Рис.8.2 – Синхронный суммирующий счетчик (двоичный) с параллельным переносом.

Рис. 8.3 – Синхронный вычитающий счетчик с параллельным переносом.

Отличительной особенностью счетчиков с параллельным переносом является то, что выходы всех предшествующих каскадов (разрядов) подаются на информационные входы J и К последующих триггеров. Длительность переходного процесса в таком счетчике равна длительности переключения одного разряда. Из схемы видно, что с возрастанием порядкового номера триггера увеличивается число входов в элементах ИJK-триггеров. А так как число входов J и К и нагрузочная способность выходов триггеров ограничены, то и разрядность счетчика с параллельным переносом невелика, и обычно равна 4. Поэтому, при числе разрядов счетчика большем максимального числа входов J и К, счетчик разбивают на группы и внутри каждой группы строят цепи параллельного переноса.

Такой подход удобен и потому, что счетчик часто реализуют в виде ИС в отдельном корпусе. В этом случае при последовательном переносе просто осуществляется увеличение разрядности счетчика.

Реверсивные счетчики выполняют операцию суммирования и вычитания импульсов. В зависимости от требований к схеме управления могут быть построены реверсивные счетчики 2 типов:

- с одним счетным и двумя управляющими входами (рис.8.4),

- с двумя счетными входами.

Реверсивный счетчик первого типа осуществляет суммирование или вычитание импульсов, поступающих на счетный вход в зависимости от разрешающего уровня на управляющих входах.

В реверсивных счетчиках второго типа по одному входу поступают импульсы для сложения, по второму – для вычитания. Для этих счетчиков не требуется дополнительных уровней управления.

Рис.8.4– Асинхронный реверсивный счетчик

В составе ИМС счетчики маркируютсябуквамиИЕ.

При использовании обратной связи можно выполнять схемы счетчиков с любым коэффициентом пересчета.

Рис.8.5, 8.6 – Двоичный счетчик с К=3;двоичный счетчик с К=10

Счетчики представляют собой автоматы Мура, в которых новое состояние определяется его предыдущим состоянием и значением логической переменной на входе.

По порядку изменения состояния могут быть счетчики:

– с естественным и

– с произвольным (принудительным) порядком изменения состояния.

В счетчиках с естественнымпорядкомизменениясостояния значение кода каждого последующего состояния счетчика отличается на единицу от кода предыдущего состояния.

В счетчиках с произвольнымпорядкомизменениясостояния значения кодов соседних состояний могут отличаться более чем на единицу.

Счетчики со сквозным переносом. Для ускорения процесса счета необходимо, чтобы изменение состояний отдельных разрядов в счетчике происходило не последовательно, а непосредственно вслед за приходом очередного счетного сигнала (рис.8.7).

Рис.8.7– Счетчик со сквозным переносом

Синтез счетчиков с К≠2n. Уменьшение числа устойчивых состояний в счетчике можно достигнуть

– за счет сброса счетчика в нулевое состояние по достижении некоторого кода в счетчике (рис.8.7);

– введения обратных связей (рис. 8.8).

Рис.8.8 – Пересчетная схема с К=6

На рис. 8.8 приведена пересчетная схема с К=6 и естественным порядком изменения состояний. Схема построена на Т-триггерах с последовательным переносом.

Пусть до прихода 1-го входного сигнала исходное состояние схемы 000, на выходе логической схемы И-НЕU1. При поступлении 5 входных сигналов изменения состояний разрядов счетчика от 000 до 101 происходит в естественной последовательности двоичных чисел, т.к. на выходе схемы И-НЕ уровень логической единицы не изменяется. Под воздействием 6-го входного сигнала на выходе схемы И-НЕ формируется уровень логического 0, устанавливающий триггер 2 в состояние 1, т.е. состояние счетчика будет 111. Длительность входных сигналов должна быть достаточной, чтобы осуществитьустановку всех разрядов счетчика. При таком условии 6-й входной сигнал произведет переход счетчика в состояние 000, т.е. в исходное состояние.

Число n триггерных ячеек в пересчетной схеме с коэффициентом пересчета К должно удовлетворять условию  .

.

Пересчетные схемы с параллельным переносом строят на JK-триггерах со встроенными логическими элементами.

Произведем синтез пересчетной схемы с К=10 на JK триггерах. Из соотношения получим разрядность пересчетной схемы n=4, а число запрещенных состояний схемы M=2n-K = 16-10 = 6.

Пусть требуется построить счетчик с параллельным переносом и естественным порядком изменения состояний, закон функционирования которой задан табл.8.2:

Табл.8.2 – Таблица переходов счетчика с параллельным переносом

| Номер входного сигнала

|

|

|

|

|

|

|

|

|

| 1.

|

|

|

|

|

|

|

|

|

| 2.

|

|

|

|

|

|

|

|

|

| 3.

|

|

|

|

|

|

|

|

|

| 4.

|

|

|

|

|

|

|

|

|

| 5.

|

|

|

|

|

|

|

|

|

| 6.

|

|

|

|

|

|

|

|

|

| 7.

|

|

|

|

|

|

|

|

|

| 8.

|

|

|

|

|

|

|

|

|

| 9.

|

|

|

|

|

|

|

|

|

| 10.

|

|

|

|

|

|

|

|

|

Табл.8.3 – Таблица переходов JK-триггера

| Вид перехода JK-триггера

| Логические уровни на входах

|

| J

| K

|

| 0→0

|

| *

|

| 0→1

|

| *

|

| 1→0

| *

|

|

| 1→1

| *

|

|

На основании табл.8.2 и 8.3 составим карты Карно для входов J и К всех триггеров пересчетной схемы. В картах Карно знак х означает запрещенные состояния схемы, для которых J и К для всех триггеров могут принимать произвольное значение (либо 0, либо 1); знак * означает произвольное значение J и К. Составим карты Карно-Вейча для минимизации функций возбуждения входов J и Kвсех триггеров

J1

J1

|

После склеивания и минимизации с помощью карт Карно получим функции переключения (возбуждения) для J и К входов каждого триггера пересчетной схемы с параллельным переносом для К=10, то-есть

J0=1 J1=  J2=Q0Q1 J3= Q0Q1Q2

J2=Q0Q1 J3= Q0Q1Q2

K0=1 K1=Q0 K2=Q0Q1 K3=Q0

Рис.8.9 – Схема счетчика с К=10

Рассмотрим работу схемы. Пусть показание счетчика 0111. Тогда на входе К триггеров Т1, Т2 и Т3 будут заблокированы по входу J уровнем логического 0 с выходов триггеров Т1, Т2 и Т3 соответственно. Показание счетчика будет 1001. Десятый входной сигнал вызовет переключение триггеров Т0 и Т3, так как Т1 и Т2 будут заблокированы по входу J уровнем 0 с выходов соответствующих триггеров. Счетчик зафиксирует двоичный код 0000, то есть установится в исходное состояние.

Пересчетные схемы с К=10 называются декадными счетчиками.

Уменьшение числа устойчивых состояний в счетчике прямого счета путем введения обратных связей обеспечивает поступление дополнительных сигналов с какого-либо старшего разряда в младшие, обеспечивая при этом изменение естественной последовательности двоичных чисел при подсчете входных сигналов.

На триггерах, работающих в режиме Т и имеющих дополнительные входы R и S для синтеза пересчетных схем с последовательным переносом используют так называемый общий метод введения обратных связей.

Рассмотрим построение пересчетной схемы с обратными связями для К=12 на синхронных RS-триггерах с динамическим управлением, работающих в режиме Т. Разрядность схемы n=4, число запрещенных состояний

m=2n-K=16-12=410=01002.

Закон функционирования схемы задан таблицей переходов (табл. 8.4):

Табл.8.4 – Таблица переходов синхронногоRS-триггера

| Номер входного сигнала

| Q3

| Q2

| Q1

| Q0

|

| 1.

|

|

|

|

|

| 2.

|

|

|

|

|

| 3.

|

|

|

|

|

| 4.

|

|

|

|

|

| 5.

|

|

|

|

|

| 6.

|

|

|

|

|

| 7.

|

|

|

|

|

| 8.

|

|

|

|

|

| OC

|

|

|

|

|

| 9.

|

|

|

|

|

| 10.

|

|

|

|

|

| 11.

|

|

|

|

|

| 12.

|

|

|

|

|

Период следования входных сигналов схемы не может быть меньше 2t3cp, где t3cp – время задержки сигнала триггером. В противном случае восьмой входной сигнал будет воздействовать на триггер Т2 до прихода сигнала на его вход S по цепи обратной связи, что может привести к ошибке при подсчете входных сигналов. Частота выходных сигналов равна fвых=fвх/К.

Рис.8.10 – Вычитающий счетчик с К=12

Задание для самостоятельной работы

1. Выполнить схемыреализации счетчика на JK-триггерах (модуль счета соответствует номеру варианта).

2. Выполнить схемы реализации синхронного и асинхронного вычитателя.

3. Выполнить схемы реализации управляемого суммирующего счетчика с параллельным переносом.

4. Синтезировать на D-триггерах схему асинхронного счетчика триггерах (модуль счета соответствует номеру варианта).

Тема9. Изучение сумматоров

Цель: приобретение практических навыков синтеза суммирования двоичных и десятичных чисел.

Теоретические сведения

Сумматоры. Комбинационные и накапливающие сумматоры двоичных чисел.Сложение в двоичной системе счисления является самой важной арифметической операцией, так как оно лежит в основе других арифметических операций: вычитания, умножения, деления.

Сумматоры предназначены для выполнения арифметических и логических операций над числами, представленными в двоичном, двоично-десятичном, троичном и др. кодах.

Для суммирования могут применяться одно- или многоразрядные сумматоры, а само суммирование осуществляется либо последовательно, начиная с младшего разряда, либо параллельно (т.е. суммируются все разряды чисел одновременно), либо параллельно-последовательно (когда многоразрядное число разбивается на группы и суммирование разрядов в группах осуществляется параллельно, а группы суммируются последовательно).

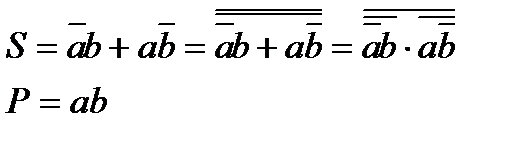

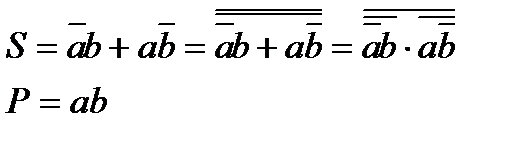

В цифровых устройствах применяются одноразрядные сумматоры на два и на три входа, причем первый называется полусумматором(ПС), а второй – полным одноразрядным сумматором (ПОС). Обе схемы реализуются на комбинационных ЛС и называются комбинационными.

Таблица состояний полусумматора (табл.9.1)

Табл.9.1– Таблица истинности двоичного полусумматора

(9.1)

(9.1)

где: S – функция суммы,

P – функция переноса в старший разряд

Табл.9.2 – Таблица состояний полного сумматор

| Значения переменных на входе

| состояние

выхода

|

| a

| b

| с

| S

| P

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

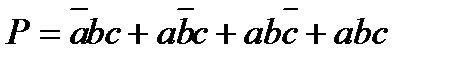

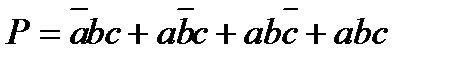

(9.2)

(9.2)

Преобразуем (9.2) в базисе И-НЕ:

Неполный сумматор имеет только два входа и два выхода. Один выход дает результат сложения двух бит, а второй – результат переноса, возникающий при сложении, т.е. неполный сумматор представляет собой, в принципе, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, дополненный выходом переноса.

Рис.9.1– Неполный сумматор (сумматор по модулю 2)

Полный же одноразрядный сумматор (ПОС), представленный таблицей истинности, имеет три входа и два выхода. На третий вход подается результат переноса предыдущего сумматора. ПОС можно построить из двух неполных (рис. 9.2).

Рис. 9.2 – Полный сумматор на 3 входа

(9.3)

(9.3)

P=ab+bc+ac

Карта Карно для S показывает, что логическая функция не минимизируется, поэтому ее преобразования можно делать только с учетом удовлетворения требований минимальных аппаратных затрат, необходимых для одновременной реализации S и Р. Вариантов таких преобразований много. Один из них, реализующий (2) в базисе И-ИЛИ-НЕ имеет вид (рис.9.3):

Рис. 9.3 – Полный сумматор на 3 входа на элементах И-ИЛИ-НЕ

(9.4)

(9.4)

Рис. 9.4 – Полный одноразрядный комбинационый сумматор на сдвоенном мультиплексоре.

ПОС вырабатывает выходные сигналы суммы и переноса, определяемые комбинацией цифр слагаемых, одновременно поданных на входы. Сумматор не обладает памятью и после снятия сигналов с входов сигналы S и P на выходе также снимаются. Такие сумматоры называются комбинационными.

Параллельный (многоразрядный) сумматор может быть составлен из одноразрядных, число которых равно числу слагаемых, путем соединения выхода, на котором формируется сигнал переноса данного разряда, с входом для сигнала переноса соседнего старшего разряда (рис. 9.5).

Рис.9.5– Сумматор параллельного типа

Последовательныйсумматор можно реализовать в соответствии со схемой, приведенной на рис. 9.6.

Рис.9.6 – Последовательный сумматор

В сумматоре рис. 9.6 операнды А и В соответственно с регистров РгА и РгВ последовательно, начиная с младших разрядов, подаются на входы А и В сумматора. Значение суммы выводится на выход Sсумматора, а значение переноса – на выход сумматора Р, к которому подключен триггер переноса. Выход триггера соединен со входом С сумматора. После суммирования значений двух одноименных разрядов суммы и переноса производится сдвиг содержимого регистров А, В и S и образуется новое значение суммы. Количество циклов сдвига определяется разрядностью слагаемых.

К достоинству схемы относится то, что для получения эначения суммы нужен только один сумматор, но при этом время суммирования зависит от числа разрядов операндов.

Организация накапливающих сумматоров на основе комбинационных схем требует применения запоминающих регистров и может строиться, например, по схеме рис. 9.7:

Рис.9.7– Сумматор накапливающего типа

Ко входам комбинационной схемы (КС) подключены два регистра слагаемых А и В, а к выходу сумматора подключен регистр суммы С, выходы которого через схемы ИЛИ могут передавать результат суммирования через регистр второго слагаемого вновь на сложение с новым значением числа А, то есть в схеме может осуществляться суммирование чисел с накоплением результатов сложения.

Рассмотренные схемы сумматоров имеют выходы S и Р. Для повышения быстродействия переносы выполняют не последовательно, а параллельно или групповым методом.

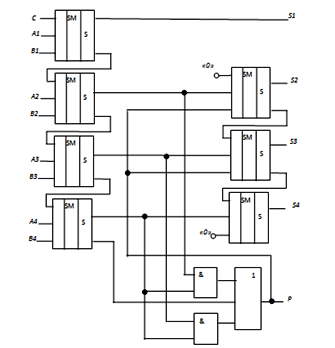

Десятичный сумматор. При сложении десятичных чисел сумматоры строят по четырехразрядному принципу.

В последние годы большинство новых ЭВМ, предназначенных для инженерных расчетов, строится так, чтобы вычисления в них выполнялись в 10 системе счисления. Это делает более удобным программирование натаких ЦВМ, обеспечивает простоту индикации промежуточных и конечных результатов, исключает блоки преобразования чисел из одной системы счисления в другую.

Задача построения десятичного одноразрядного сумматора (точнее двоично-десятичного) в принципе может решаться также, как и задача построения двоичного сумматора. Однако, если в случае двоичного сумматора требовалось реализовать 2 функции от трех двухзначных переменных (S и Р), то в случае десятичного сумматора необходимо реализовать 5 функций от 9 двухзначных переменных – по 4 переменных для каждой десятичной цифры и одна переменная – перенос из младшего разряда. При этом выходные функции будут определены лишь на 200 наборах из 29=512. Можно было бы записатьСДНФ этих функций и минимизировать их известными формальными методами. Однако СДНФ в этом случае содержали бы десятки дизъюнктивных членов, что значительно затрудняет минимизацию. Кроме того, вследствие большого числа неопределенных значений функций трудно решить вопрос об их оптимальномдоопределении. Поэтому при использовании двоично-десятичных кодов с весами 8421 задачу суммирования десятичных цифр решают в два этапа. На первом этапе суммируют двоичные коды десятичных цифр по правилам двоичной арифметики. На втором этапе производят коррекцию результата путем прибавления или вычитания некоторой поправки, величина которой связана с величиной нескорректированного результата. При этом могут возникать три случая.

1. Результат, полученный на 1 этапе, меньше 10. В этом случае никакой коррекции не требуется. Результат представляется четырьмя двоичными разрядами, а переноса в старший десятичный разряд нет.

2. Результат 1 этапа находится в пределах от 10 до 15. Здесь необходимо передать единичный сигнал переноса в старший десятичный разряд, а в данном десятичном из полученной суммы следует вычесть поправку, равную 10.

3. Результат 1 этапа находится в пределах от 16 до 19. В этом случае необходимо передать единицу переноса в старший десятичный разряд. Но при этом сумма в данном десятичном разряде уменьшится сразу на 16, в то время, как она должна уменьшиться только на 10. Поэтому необходимая коррекция – прибавление 6. Следует заметить, что во втором случае коррекция может быть введена точно также, как в третьем, так как вычитание цифры 10 может быть заменено сложением с ее дополнительным кодом, которым и является код цифры 6 – 0110.

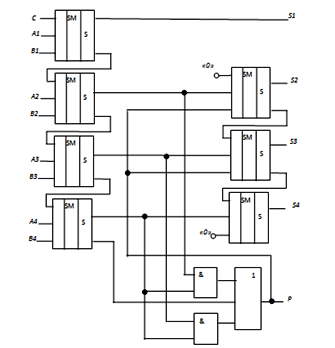

На рис. 9.8 ряд сумматоров реализует первый этап сложения. Наличие сигнала переноса на выходе старшего двоичного разряда означает, что результат первого этапа больше или равен 16. Кроме того, перенос в старший разряд (десятичный) должен формироваться в тех случаях, когда сумма больше или равна 10, то есть когда в ее двоичном представлении будут получены коды 1010, 1011, 1100, 1101, 1110, 1111. Для обнаружения таких кодов необходима схема из двух элементов И.

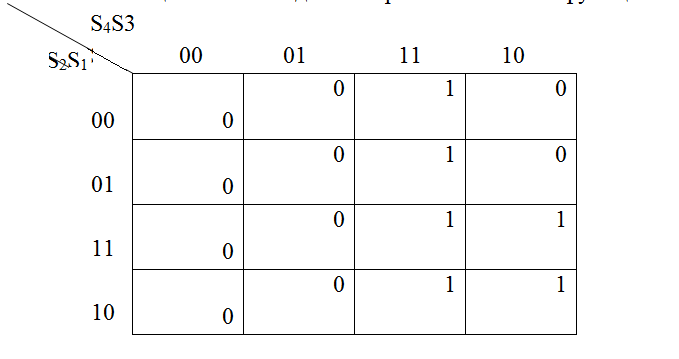

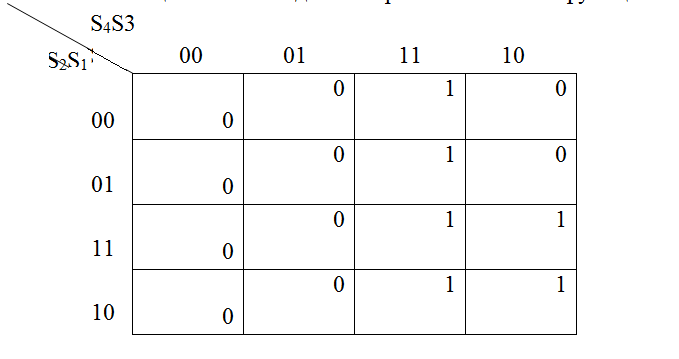

Для определения переключательной функции переноса воспользуемся картой Карно-Вейча, полученной на основе анализа выходов сумматоров S1…S4 (Табл.9.3).

Табл.9.3 – Нахождение переключательной функции переноса

Переключательная функция формирования сигналов переноса в старшую декаду P запишется в виде:

P = S4S3 VS4S2.(9.5)

Рис. 9.8– Схема одноразрядного десятичного сумматора

Другой ряд сумматоров предназначен для прибавления корректирующей поправки.

Схему можно упростить, заменив SM5 и SM7 полусумматорами.

По такому принципу можно строить и сумматоры, например, для кодов с избытком 3.

Буквенное обозначение в составе ИМС: сумматоры – ИМ, полусумматоры – ИЛ.

Рис.9.9 – Обозначение двоично-десятичного сумматора ИМ3

Задание для самостоятельной работы

1. Выполнить синтез двоичного сумматора на 2 входа на элементах И-НЕ.

2. Выполнить синтез двоичного сумматора на 2 входа на элементах ИЛИ-НЕ.

3. Выполнить схему сумматора на элементах базиса И, ИЛИ, НЕ.

4. Выполнить схему одноразрядного двоичного сумматора на 3 входа на элементах 2-2И-ИЛИ-НЕ.

5. Выполнить синтез последовательного сумматора для суммирования двух четырехразрядных двоичных чисел.

6. Выполнить синтез параллельного сумматора для суммирования двух четырехразрядных двоичных чисел.

.

.

J1

J1

(9.1)

(9.1) (9.2)

(9.2)

(9.3)

(9.3)

(9.4)

(9.4)