В компьютерной технике для хранения информации используют:

оперативные запоминающие устройства (ОЗУ), которые содержат наборы регистров на RS-триггерах – ячейки памяти; эти ОЗУ (RAM) формируются на основе сверхбольших интегральных схем (СБИС);

долговременные запоминающие устройства (ДЗУ) на специальных носителях информации.

ОЗУ более быстродействующие, чем ДЗУ, но имеют меньший информационный объем.

ДЗУ хранят информацию, как правило, на оптических и магнитных дисках, постоянно работающих в составе устройства или сменных накопителях.

На НП имеются две такие СБИС. Они представлены на рис. 21 и рис. 22.

Рис. 21. RAM1 на НП. Рис. 22. RAM2 на НП.

На рис. 21 ячейки памяти – регистры RG1..RG4, содержащие по четыре D триггера. Номер регистра – адрес ячейки памяти. Обеспечивают работу регистров элементы “И”, ”ИЛИ”, ”НЕ” и логические ключи BF (буфер).

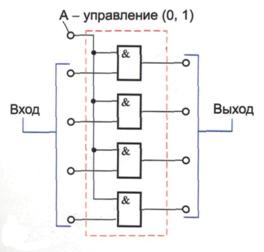

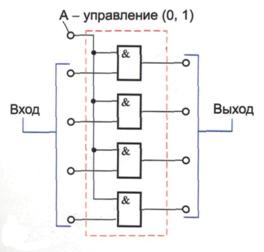

Схема буфера для четырехразрядной шины – на рис. 24. Сигнал А = 1 разрешает прохождение входных логических переменных на выход. При А = 0 на выходе буфера – нули.

Чтобы считать информацию с RG нужно подключить Q-выходы этого RG к шине данных RAM (D1..D4).

Выбор нужной ячейки памяти производится указанием ее адреса. Два двоичных разряда (А1, А2) позволяют задать один из четырех адресов.

Рис. 23. Структура СБИС.

00 – RG1, 01 – RG2, 10 – RG3, 11 – RG4

Преобразователь кода в сигнал управления на линии, соответствующей номеру ячейки – дешифратор адреса (ДША).

Рис. 24. Схема буфера для четырехразрядной шины.

Считывание информации с RG1

Для считывания информации с RG1 необходимо задать два нулевых двоичных разряда (A1 = 0, A2 = 0). На выходе “1” ДША – логическая “1”. Разрешающий сигнал поступает на ключевые схемы “2И”: &1з, &1с. Первая из них работает в режиме “запись”, вторая – “считывание”.

Сигнал “запись в RAM” отсутствует (W = 0). На второй вход &1с инвертор подает “1”. На всей линии “считывание” +5В!

На выходе &1с – логическая “1”, она поступает на управляющий вход А BF1. Буфер BF1 открыт. Сигналы с выходов Q1..Q4 RG1 поступают на шину данных RAM!

Аналогично, при задании кода адреса, считывается информация с любой ячейки RAM – с любого RG.

Запись информации в RAM

Для записи информации на вход W необходимо подать логическую “1”. Зададим адрес ячейки, например: “00” (RG1), тогда откроется ключ – &1з. Логическая “1” с выхода &1з поступает на вход С RG1, тем самым регистр принимает информацию по входам D1..D4 с шины данных.

Существует ряд особенностей модулей RAM на НП ЭЛИК.

Первая – это многостраничные ОЗУ. RAM1 и RAM2 содержат по 8 модулей – страниц памяти.

Перемещая движки переключателей “Номер страниц в ОЗУ”, мы выбираем одну из страниц памяти: 000, 001..111. Каждая из страниц соответствует RAM1 и RAM2, изображенным на НП ЭЛИК. Связи между страницами нет.

Выбор страницы производится с помощью дешифратора, аналогичного ДША. Буферы страничного ОЗУ позволяют подключать любую из страниц памяти к шинам адресов и данных.

Вторая особенность – RAM1 и RAM2 при четырехразрядных адресах (А1, А2, А4, А8) содержат 24 = 16 ячеек. Но в RAM1 используется только 10 регистров 0, 1..9. Это обусловлено тем, что для индикации адресов достаточно использовать один семисегментный индикатор. От 0 до 9-ти считает счетчик команд РС. В учебных целях этого является достаточно.

Микросхемы RAM на НП ЭЛИК – энергонезависимые. При включении питания записанные в ячейки памяти данные сохраняются. Для стирания данных в ячейку записывают “0”.

Входы A и D в RAM1 и RAM2 при записи “подтянуты” к “1”!

Для усвоения и проверки работы RAM сделаем несколько ознакомительных тестов.

Тест 1. Запись и считывание кодов

Для проведения этого теста необходимо подключить шину А RAM2 к правому индикатору “Результат”, выходы клавиатуры К10 (n) – к левому индикатору “Результат”, а также к шине D RAM2. Необходимо выбрать страницу “000”. Схема подключения приведена на рис. 25.

Для задания двоичных кодов адресов ячеек, от “0” до “15” нужно подать логический “0” на шину А RAM2 (0000..1110). С помощью К10 в ячейки RAM2 будет записываться последовательность чисел, например, четные.

Рис. 25. Схема подключения контактов для “Теста 1”.

● (1-4) – Подключение шины А RAM2 к правому индикатору “Результат”.

● (5-8) – Подключение клавиатуры к шине данных RAM2 и левому индикатору “Результат”.

Для считывания кодов необходимо отключить К10, а переключатель “ОЗУ” перевести в положение “ИСП”. Задавая адреса от “0” до “15”, проверяем записанные коды.

Тест 2. Автоматизация записи и считывания кодов.

Для реализации теста необходимо собрать схему, представленную на рис. 26. Соединяем выход Р РС с выходом ОСТ1 ГТИ, выход SA4 с “Пуск” ГТИ, выход ТИ ГТИ с “+1” РС.

Выберем  .

.

Шину А RAM1 подключим на индикатор “Операнд А”. Выходы К10 – на два индикатора “Результат”, а также на шину данных RAM1.

При проведении теста движок SA2 необходимо перевести в нижнее положение. Пуск ГТИ осуществляется с помощью SA4!

При появлении на индикаторе нового адреса задаем новое число с К10, нажимаем на кнопку “Запись”!

Повторяем проход по адресам с помощью РС в режиме “ИСП”.

Рис. 26. Схема подключения контактов для “Теста 2”.

● 1 – Подключение выхода ОСТ1 ГТИ к выходу Р РС.

● 2 – Подключение выхода Пуск ГТИ к выходу SA4.

● 3 – Подключение выхода ТИ ГТИ к выходу “+1” РС.

● (4-7) – Вывод на индикатор.

● (8-11) – Подключение шины D RAM1 к левому индикатору “Результат” и клавиатуре К10 (m).

● (12-15) – Подключение шины D RAM1 к правому индикатору “Результат” и клавиатуре К10 (n).

Тест 3. Проверка работы страниц RAM1 от “0” до “7”

Данный тест реализуется схемой, аналогичной схеме, представленной в Тесте 2. Различие между этими тестами заключается в том, что мы используем для записи различные страницы ОЗУ. Как отмечалось ранее, переключение между страницами осуществляется перемещением движков переключателей “Номер страницы в ОЗУ”.

После записи всех страниц движки необходимо перевести на нулевую страницу а переключатель ОЗУ в режим “ИСП”.

В качестве практического примера рассмотрим, как работает микросхема памяти. Будем использовать для этого микросхему RAM2 наборного поля ЭЛИК 01.ИН. На рис.27 представлена схема подключения RAM2.

Рис. 27. Схема подключения RAM2.

Для того чтобы записать данные в микросхему памяти нужно:

1. Перевести микросхему в режим записи. Это выполняется с помощью переключателей, представленных на рисунке ниже. Левый переключатель – чтение/запись, а правый выбирает микросхему памяти RAM1 или RAM2.

2. Задать адрес ячейки памяти, в которую будет производиться запись первым нажатием на кнопку клавиатуры;

3. Подать данные на входы Dx микросхемы RAM2 вторым нажатием на кнопку клавиатуры.

4. Подать сигнал записи W=1 кнопкой

При вводе адреса и данных с клавиатуры они будут сразу же отображаться на индикаторах.

Теперь для чтения данных из микросхемы памяти нам придется отключить выходы Dx микросхемы RAM2 от клавиатуры, чтобы они не перебивали сигнал.

Переведем RAM2 в режим чтения и зададим с клавиатуры адрес ячейки памяти, из которой хотим считать данные. Результат будет виден на втором индикаторе.

Для последовательного занесения данных можно использовать микросхему PC. Пример с использованием PC приведен на рис. 28.

Рис. 28. Схема подключения RAM2 с последовательным чтением

и записью данных.

В схеме на рис. 28 PC играет роль счетчика ячеек памяти. Он последовательно перебирает их при нажатии на кнопку SA4. Для сброса можно воспользоваться переключателем SA3. В остальном, схема работает так же, как и предыдущая.

Внимание! Для чтения данных из микросхемы памяти нам придется отключить выходы Dx микросхемы RAM2 от клавиатуры, чтобы они не перебивали сигнал, как в выше рассмотренном примере. Если этого не сделать - схема работать не будет.

На рис. 29 показана схема подключения контактов на наборном поле ЭЛИК 01.ИН для схемы на рис. 28.

Рис. 29. Схема подключения контактов RAM2 с последовательным

чтением и записью данных.

● (1-4) – Подключение клавиатуры и дисплея к RAM2 для ввода и вывода данных.

● (5-8) – Подключение PC к RAM2 для выбора адреса ячейки памяти.

● (9-12) – Вывод на индикатор адреса ячейки памяти.

● (13-14) – Подключение кнопки и переключателя для управления счетчиком адресов.

.

.