СОДЕРЖАНИЕ

Реферат ………………………………………………………………….......3

Введение ………………………………………………………………….....4

1. Постановка задачи…………………………………………………….....6

1.1 Операционный автомат…………………………………………......6

1.2 Управляющий автомат………………………………………….......7

1.3 Алгоритмы выполняемых операций……………………………….9

1.3.1 Алгоритм умножения целых двоичных

беззнаковых чисел, начиная с младших

разрядов множителя, со сдвигом суммы частичных

произведений вправо…………………………………………..……9

1.3.2 Алгоритм деления целых двоичных беззнаковых

чисел без восстановления остатка………………………………...10

1.4 Объединеннная граф схема функционирования……………........12

2. Проектирование операционного автомата…………………….............13

3. Проектирование управляющего автомата…………………...…..........17

4. Проектирование процессороного модуля………………………..........21

4.1 Схема объединения операционного и управляющего автоматов…………………………………………………………...21

4.2 Результаты тестирования …………………………………...…….21

Вывод…………………………………………..............................................22

Список использованной литературы………………………………...........23

Приложение А …………………………………………………………..24

РЕФЕРАТ

Пояснительная записка содержит 27 страниц, 4 части, 1 приложение, 5 источников литературы.

Целью данного курсового проектирования является разработка процессорного модуля на основе построения управляющего и операционного автомата.

В результате выполнения проектирования получены принципиальная схема управляющего автомата и функциональная схема операционного автомата.

КЛЮЧЕВЫЕ СЛОВА: УПРАВЛЯЮЩИЙ АВТОМАТ, ОПЕРЦИОННЫЙ АВТОМАТ, ФУНКЦИОНАЛЬНАЯ СХЕМА, ПРИНЦИПИАЛЬНАЯ СХЕМА, АРИФМЕТИЧЕСКИЕ ОПЕРАЦИИ, МИКРОКОМАНДА.

ВВЕДЕНИЕ

ЭВМ – искусственная (инженерная) система, предназаначенная для выполнения вычислений на основе алгоритмов. Принципы построения ЭВМ определяются, с одной стороны, назначением ЭВМ и, с другой стороны, элементной базой – набором элементов, который может быть использован для создания ЭВМ. Назначение ЭВМ – выполнение вычислений на основе алгоритмов, и поэтому свойства алгоритмов предопределяют принципы построения ЭВМ – организацию ЭВМ.

К числу важнейших свойств алгоритмов, наиболее существенно влияющих на организацию ЭВМ, относятся:

· дискретность информации, с которой оперируют алгоритмы;

· конечность и элементарность набора операций, выполняемых при реализации алгоритмов;

· детерминированность вычислительных процессов, порождаемых алгоримами.

ЭВМ, как и любую систему, можно рассматривать в двух аспектах: функциональном и структурном.

С функциональной точки зрения ЭВМ – это система функциональных, абстрактных элементов, в терминах которых представляется информация, относящаяся к данным и алгоритмам. К числу таких элементов относятся наборы символов, используемых для представления данных, машинные операции, адреса и команды, в терминах которых могут быть представлены алгоритмы и процессы вычислений.

Со структурной точки зрения ЭВМ – это система, состоящая из взаимосвязанных материальных объектов, организованных таким образом, чтобы их функционирование, представляемое совокупностью физических процессов, приводило к реализации заданных функций – вычислениям на основе алгоритмов. Одни и те же функции могут быть реализованы различными структурами, отличающимися номенклатурой и количеством используемых элементов и конфигурацией связей между ними. Различные структуры обеспечивают различную скорость вычислений при различных затратах оборудования.

Следовательно, функции являются первичными по отношению к структурам и проектирование ЭВМ должно начинаться с конкретизации принципа программного управления в плане способов представления данных, состава операций, способов адресации информации и типов команд, соответствующих назначению ЭВМ.

Для реализации на ЭВМ различных алгоритмов выполняемых операций, таких как умножение, деление, используется специальное устройство, называемое процессорным модулем, разработка которого и представлена в данном курсовом проекте.

ПОСТАНОВКА ЗАДАЧИ

В данном курсовом проекте необходимо разработать процессорный модуль на основе синтеза управляющего автомата и операционного автомата. Необходимо построить управляющий автомат П-автомат с естественной адресацией и операционный автомат класса I для устройств деления целых двоичных беззнаковых чисел без восстановления остатка и ускоренного умножения целых двоичных беззнаковых чисел.

1.1 Операционный автомат

Операционные автоматы, структура которых обеспечивает возможность одновременного выполнения всех функционально совместимых микроопераций при использовании минимального числа комбинационных схем, называют операционные автоматы класса I.

Операционный автомат осуществляют вычислительные действия над операндами. Структурно операционный автомат состоит из элементов памяти (регистров), осуществляющих хранение значений операндов, и комбинационных схем, отвечающих за выполнение микроопераций. Входной информацией для операционного автомата являются линии данных {D} и множество выполняемых в данном такте микроопераций {Y}, выходами являются линии результата {R} и выработанные признаки результата {X}, используемые в управляющем автомате.

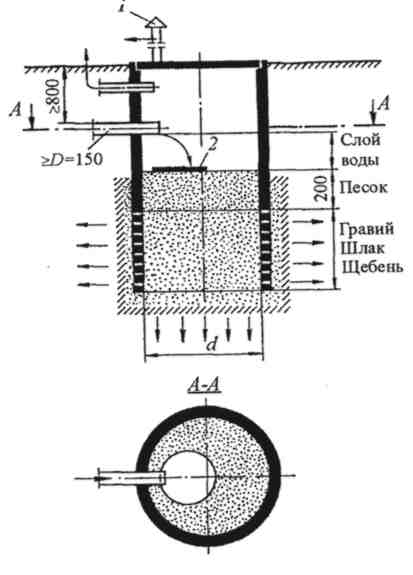

Структура операционного автомата класса I представлена на рис. 1.1.

Рис. 1.1 Структура операционного автомата класса I.

ПРИЛОЖЕНИЕ А

Листинг программы

---------------

-- unit.vhd

---------------

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_unsigned.all;

entity OU is

generic (n:natural:=8);

port(-- n = 8

clk,rst:in std_logic;

d1:in std_logic_vector(2*n-1 downto 0);

d2:in std_logic_vector(n-1 downto 0);

f:in std_logic;

y:in std_logic_vector(22 downto 1);

x:out std_logic_vector(9 downto 1);

DBUS:out std_logic_vector(2*n-1 downto 0)

);

end OU;

--}} End of automatically maintained section

architecture OU of OU is

--use ieee.std_logic_unsigned.all;

signal A:std_logic_vector(2*n downto 0);

signal B:std_logic_vector(n downto 0);

signal C:std_logic_vector(n+1 downto 0); --Po GSA 7

signal CnT:std_logic_vector(3 downto 0);

--signal CnTu:std_logic_vector(2 downto 0);

signal TgA,IRQ1,IRQ2:std_logic;

--signal stop:std_logic:= '0';

begin

process (clk,rst) is

begin

if rst='0' then A <=(others=>'0');

B <=(others=>'0');

C <=(others=>'0');

Cnt <= "1000";

-- CnT <= "111";

elsif rising_edge(clk) then

if y(1)='1' then A <= ("00000000" & d1(2*n-1 downto 0));

elsif y(15)='1' then A <= ("00000000" & d1(n-1 downto 0));

elsif y(3)='1' then A(2*n downto n) <= IEEE.std_logic_signed."+"(A(2*n downto n), (not B));

A(2*n-1 downto n-1) <= IEEE.std_logic_signed."+"(A(2*n downto n),1);--****

elsif y(8)='1' then A(2*n downto n) <= IEEE.std_logic_signed."+"(A(2*n downto n), B);

elsif y(5)='1' then A <= '0'&A(2*n-1 downto 0) & '0';

elsif y(17)='1' then A <= '0'&A(n-1 downto 0) & '0';

end if;

if y(2)='1' then B <= ("00000000" & d2(n-1 downto 0));

elsif y(16)='1' then B <= d2(n-1 downto 0);

elsif y(20)='1' then B <= '0' & C(1 downto 0) & B(n-1 downto 2);

end if;

if y(6)='1' then C <=(others=>'0');

elsif y(9)='1' then C <= '0'&C(n-2 downto 0)&(not A(2*n));

elsif y(19)='1' then C(n+1 downto 0) <= IEEE.std_logic_signed."+"(C(n+1 downto 0), (not A));

C(n downto -1) <= IEEE.std_logic_signed."+"(C(n+1 downto 0),1);--****

elsif y(18)='1' then C(n+1 downto 0) <= IEEE.std_logic_signed."+"(C(n+1 downto 0), A);

elsif y(21)='1' then c <= '0' & C(n+1)& C(n+1)& C(n+1 downto 2);

end if;

if y(7)='1' then CnT<="1000";

elsif y(10)='1' then CnT <= CnT - 1;

end if;

if y(4)='1' then TgA <= A(2*n);

end if;

if y(13)='1' then IRQ1 <= '1'; assert (0>1) report "IRQ1 was thrown" severity failure;

elsif y(14)='1' then IRQ2 <= '1'; assert (0>1) report "IRQ2 was thrown" severity failure;

end if;

end if;

end process;

----------------------

-- IRQ1 <= '1' when y(13)='1';--assert (0>1) severity failure;

-- IRQ2 <= '1' when y(14)='1';--assert (0>1) severity failure;

DBUS <= C(n-1 downto 0) & B(n-1 downto 0) when y(22)='1'else

--DBUS <=

C(n-1 downto 0) when y(11)='1' else

A(2*n-1 downto n) when y(12)='1' else (others=>'Z');

x(1) <= f;

x(2) <= '1' when B = "000000000" else '0';

x(3) <= A(2*n);

x(4) <= TgA;

x(5) <= '1' when CnT = "000" else '0';

x(6) <= (not B(1)) and (C(n+1) xor B(0));

x(7) <= ((not C(n+1)) and B(1) and (not B(0))) or (C(n+1) and (not B(1))and B(0));

x(8) <= B(1) and (C(n+1) xor B(0));

x(9) <= C(n+1);

end OU;

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.std_logic_unsigned.all;

entity CU is

port(

clk,rst:in std_logic;

x:in std_logic_vector(9 downto 1);

y:out std_logic_vector(22 downto 1)

);

end CU;

architecture CU of CU is

subtype TCommand is std_logic_vector(10 downto 0);

type TROM is array (0 to 37) of TCommand;

constant ROM:TROM:= (

"10001010110",--0

"00001001000",--1

"10010001110",--2

"00010000000",--3

"10011010000",--4

"00011010011",--5

"10100010010",--6

"00010000000",--7

"00011011100",--8

"10101010100",--9

"10100001100",--10

"00100000000",--11

"00101100000",--12

"10000000000",--13

"00110000000",--14

"10000000000",--15

"00111000000",--16

"10000001111",--17

"00100000000",--18

"10000001000",--19

"00000010000",--20

"10000000110",--21

"01000101011",--22

"10110011111",--23

"01010000000",--24

"01100110100",--25

"10101100101",--26

"11001011101",--27

"01010000000",--28

"00000111000",--29

"10000000000",--30

"10111100010",--31

"01001000000",--32

"10000011000",--33

"11000100100",--34

"01011000000",--35

"10000011001",--36

"10000010111");--37

signal RegCom:TCommand;

signal PC:integer;

begin

process(rst,clk) is

variable PCv:integer range 0 to 37;

begin

if rst='0' then PCv:=0;

elsif rising_edge(clk) then

if RegCom(10)='1' and ((x and RegCom(9 downto 6))="0000") then

PCv:=conv_integer(RegCom(5 downto 0));

else

PCv:=PCv+1;

end if;

end if;

RegCom<=ROM(PCv);

PC<=PCv;

end process;

y <= RegCom(9 downto 0) when RegCom(10)='0' else (others=>'0');

end CU;

----------------

--cpu.vhd

----------------

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use work.all;

entity CPU is

port(

clk,rst:in std_logic;

d1:in std_logic_vector(15 downto 0);

d2:in std_logic_vector(7 downto 0);

F:in std_logic;

DBUS:out std_logic_vector(15 downto 0)

);

end CPU;

--}} End of automatically maintained section

architecture cpu of cpu is

component OU

port(

clk,rst:in std_logic;

d1:in std_logic_vector(15 downto 0);

d2:in std_logic_vector(7 downto 0);

f:in std_logic;

y:in std_logic_vector(22 downto 1);

x:out std_logic_vector(9 downto 1);

DBUS:out std_logic_vector(15 downto 0)

);

end component;

component CU

port (

clk,rst:in std_logic;

x:in std_logic_vector(9 downto 1);

y:out std_logic_vector(22 downto 1)

);

end component;

signal y: std_logic_vector (22 downto 1);

signal x: std_logic_vector (9 downto 1);

signal nclk: std_logic;

begin

nclk <= not clk;-- after 10 ns;

dd1:OU port map (nclk,rst,d1,d2,f,y,x,DBUS);

dd2:CU port map (clk,rst,x,y);

end cpu;

СОДЕРЖАНИЕ

Реферат ………………………………………………………………….......3

Введение ………………………………………………………………….....4

1. Постановка задачи…………………………………………………….....6

1.1 Операционный автомат…………………………………………......6

1.2 Управляющий автомат………………………………………….......7

1.3 Алгоритмы выполняемых операций……………………………….9

1.3.1 Алгоритм умножения целых двоичных

беззнаковых чисел, начиная с младших

разрядов множителя, со сдвигом суммы частичных

произведений вправо…………………………………………..……9

1.3.2 Алгоритм деления целых двоичных беззнаковых

чисел без восстановления остатка………………………………...10

1.4 Объединеннная граф схема функционирования……………........12

2. Проектирование операционного автомата…………………….............13

3. Проектирование управляющего автомата…………………...…..........17

4. Проектирование процессороного модуля………………………..........21

4.1 Схема объединения операционного и управляющего автоматов…………………………………………………………...21

4.2 Результаты тестирования …………………………………...…….21

Вывод…………………………………………..............................................22

Список использованной литературы………………………………...........23

Приложение А …………………………………………………………..24

РЕФЕРАТ

Пояснительная записка содержит 27 страниц, 4 части, 1 приложение, 5 источников литературы.

Целью данного курсового проектирования является разработка процессорного модуля на основе построения управляющего и операционного автомата.

В результате выполнения проектирования получены принципиальная схема управляющего автомата и функциональная схема операционного автомата.

КЛЮЧЕВЫЕ СЛОВА: УПРАВЛЯЮЩИЙ АВТОМАТ, ОПЕРЦИОННЫЙ АВТОМАТ, ФУНКЦИОНАЛЬНАЯ СХЕМА, ПРИНЦИПИАЛЬНАЯ СХЕМА, АРИФМЕТИЧЕСКИЕ ОПЕРАЦИИ, МИКРОКОМАНДА.

ВВЕДЕНИЕ

ЭВМ – искусственная (инженерная) система, предназаначенная для выполнения вычислений на основе алгоритмов. Принципы построения ЭВМ определяются, с одной стороны, назначением ЭВМ и, с другой стороны, элементной базой – набором элементов, который может быть использован для создания ЭВМ. Назначение ЭВМ – выполнение вычислений на основе алгоритмов, и поэтому свойства алгоритмов предопределяют принципы построения ЭВМ – организацию ЭВМ.

К числу важнейших свойств алгоритмов, наиболее существенно влияющих на организацию ЭВМ, относятся:

· дискретность информации, с которой оперируют алгоритмы;

· конечность и элементарность набора операций, выполняемых при реализации алгоритмов;

· детерминированность вычислительных процессов, порождаемых алгоримами.

ЭВМ, как и любую систему, можно рассматривать в двух аспектах: функциональном и структурном.

С функциональной точки зрения ЭВМ – это система функциональных, абстрактных элементов, в терминах которых представляется информация, относящаяся к данным и алгоритмам. К числу таких элементов относятся наборы символов, используемых для представления данных, машинные операции, адреса и команды, в терминах которых могут быть представлены алгоритмы и процессы вычислений.

Со структурной точки зрения ЭВМ – это система, состоящая из взаимосвязанных материальных объектов, организованных таким образом, чтобы их функционирование, представляемое совокупностью физических процессов, приводило к реализации заданных функций – вычислениям на основе алгоритмов. Одни и те же функции могут быть реализованы различными структурами, отличающимися номенклатурой и количеством используемых элементов и конфигурацией связей между ними. Различные структуры обеспечивают различную скорость вычислений при различных затратах оборудования.

Следовательно, функции являются первичными по отношению к структурам и проектирование ЭВМ должно начинаться с конкретизации принципа программного управления в плане способов представления данных, состава операций, способов адресации информации и типов команд, соответствующих назначению ЭВМ.

Для реализации на ЭВМ различных алгоритмов выполняемых операций, таких как умножение, деление, используется специальное устройство, называемое процессорным модулем, разработка которого и представлена в данном курсовом проекте.

ПОСТАНОВКА ЗАДАЧИ

В данном курсовом проекте необходимо разработать процессорный модуль на основе синтеза управляющего автомата и операционного автомата. Необходимо построить управляющий автомат П-автомат с естественной адресацией и операционный автомат класса I для устройств деления целых двоичных беззнаковых чисел без восстановления остатка и ускоренного умножения целых двоичных беззнаковых чисел.

1.1 Операционный автомат

Операционные автоматы, структура которых обеспечивает возможность одновременного выполнения всех функционально совместимых микроопераций при использовании минимального числа комбинационных схем, называют операционные автоматы класса I.

Операционный автомат осуществляют вычислительные действия над операндами. Структурно операционный автомат состоит из элементов памяти (регистров), осуществляющих хранение значений операндов, и комбинационных схем, отвечающих за выполнение микроопераций. Входной информацией для операционного автомата являются линии данных {D} и множество выполняемых в данном такте микроопераций {Y}, выходами являются линии результата {R} и выработанные признаки результата {X}, используемые в управляющем автомате.

Структура операционного автомата класса I представлена на рис. 1.1.

Рис. 1.1 Структура операционного автомата класса I.

Управляющий автомат типа П с естественной адресацией

Управляющий автомат может быть построен на основе принципа программного управления, использующего операционно-адресную структуру управляющих слов. Управляющее слово определяет порядок функционирования устройства в течение одного такта и называется микрокомандой. Совокупность микрокоманд образует массив МК [0… P ], отдельные микрокоманды в котором выделяются посредством адреса, равного номеру 0, 1, … Р элемента массива МК. Микрокоманда содержит информацию о микрооперациях, которые должны выполняться в данном такте работы устройства, и (или) информацию об адресе следующей микрокоманды.

Определим простейшую структуру управляющих слов, достаточную для представления микрокоманд.

Пусть множество Y содержит М микроопераций, которым присвоим номера 1, 2, … М. Номера микроопераций будем кодировать м- разрядными двоичными числами, где м ³log2(M +2). Коды микроопераций указываются в операционной части микрокоманды. Поле Y определяет номер микроопераций, возбуждаемых микрокомандой. Если Y=0, то поле Y является пустым и не возбуждает ни одной микрооперации.

Для определения адреса следующей микрокоманды используются следующие способы адресации:

- Принудительная адресация.

- Естественная адресация.

При естественной адресации адрес следующей микрокоманды принимается равным увеличенному на единицу адресу предыдущей микрокоманды, т.е. если А – адрес выполняемой микрокоманды, то следующая микрокоманда выбирается из ячейки с адресом (А +1). При естественной адресации отпадает необходимость во введении адресного поля в каждую микрокоманду. Если микрокоманды следуют в естественном порядке, то порядок адресации реализуется счетчиком адреса микрокоманды, состояние которого увеличивается на единицу после чтения очередной микрокоманды, которые задают функциональные преобразования, состоящие из набора микроопераций, могут содержать только операционную часть, представляемую полями Y 1, Y 2, … YH. После выполнения микрокоманды с адресом А может возникнуть необходимость в переходе к микрокоманде с адресом В¹А +1. Переход может быть безусловным или зависеть от текущего значения условий хХ. Для реализации переходов в состав микрокоманды вводятся поля Х и В.

При естественной адресации обычно используются микрокоманды двух типов – операционные и управляющие. Операционная микрокоманда задает набор микрокоманд, выполняющихся на данном такте, и неявно полагает адрес следующей микрокоманды, равным А +1. Управляющие микрокоманды предназначены для изменения естественного порядка следования микрокоманд, что сводится к выполнению безусловных и условных переходов.

Управляющая микрокоманда содержит поле Х, определяющее условие ветвления, и поле В, определяющее адрес следующей микрокоманды. Если условие не выполняется (или при реализации безусловных переходов), адрес становится равным В. Для разделения операционных и управляющих микрокоманд в управляющем слове вводится разряд признака Р, при Р =0 микрокоманда является операционной, при Р =1 – управляющей.

Возможная структура управляющей и операционной микрокоманд представлена на рис. 1.2

Рис. 1.2 Структура операционной и управляющей микрокоманды