План: 1. Логические и запоминающие элементы ЭВМ.

2. Функциональные узлы ЭВМ. Схемотехника БИС и СБИС.

Логические и запоминающие элементы ЭВМ. Технические устройства средств вычислительной техники строятся на основе и различного рода логических элементов и узлов. К типовым логическим элементам относятся: элемент И, элемент ИЛИ, элемент НЕ. На основе комбинации данных элементов строятся различные логические устройства, называемые логическими схемами.

Запоминающие устройства ЭВМ выполняются на базе типовых элементов памяти, к которым относятся триггеры, ферромагнитные и оптоэлектронные элементы памяти и их комбинации.

Вспомогательные устройства представляют усилители, ограничители, формирующие схемы и т.д.

В группу специальных устройств входят усилители записи-считывания для магнитных головок, усилители считывания с фотодиодов, формирователи, задающие генераторы, повторители, генераторы одиночных сигналов, индикаторные схемы и др.

Логические элементы и элементы памяти называют основными функциональными элементами средств вычислительной техники.

Комплекс основных функциональных, вспомогательных и специальных элементов, на основе которых разрабатываются средства вычислительной техники, называется системой элементов.

Функциональные узлы ЭВМ представляют отдельные части ЭВМ, реализующие заданные функции в виде определенных машинных операций. Они выполняются, как правило, на основе единых серий элементов ЭВМ. Промышленность выпускает серии элементов (и узлов), на основе которых может быть реализована ЭВМ, выполняющая любые заложенные в нее функции.

Примером подобной серии элементов и узлов может служить комплекс интегральных элементов: К580, КР580, К1810, К1801.

Различают следующие типовые функциональные узлы ЭВМ:

- триггеры;

- регистры;

- счетчики;

- шифраторы;

- дешифраторы;

- мультиплексоры;

- демультиплексоры;

- сдвигатели;

- распределители (уровней и импульсов) и др.

Триггер – это функциональный узел ЭВМ, содержащий элемент памяти и схемы управления данным элементом. Существуют различные классификации триггеров, в частности:

1. По времени поступления сигналов:

· асинхронные, синхронные.

· однотактные - одноступенчатые, двуступенчатые;

· многотактные.

2. По базису, т.е. используемым логическим элементам:

· в базисе И–НЕ;

· в базисе ИЛИ-НЕ;

· в смешанном базисе.

3. По типу: RS, D, JK, T, DV, DT, RST и др.

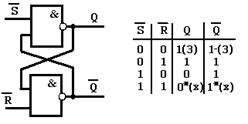

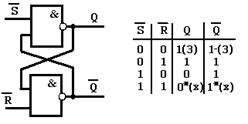

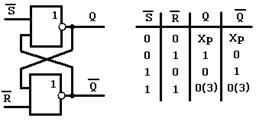

Асинхронные триггеры бывают только RS-типа и представляют логическую схему вида:

Асинхронный RS-триггер в базисе И-НЕ

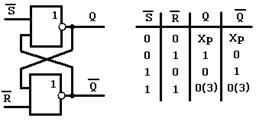

Асинхронный RS-триггер в базисе ИЛИ-НЕ

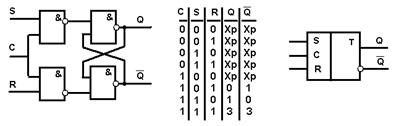

Синхронные триггеры могут быть более разнообразного типа, в частности, следующие:

Синхронные однотактные одноступенчатые триггеры.

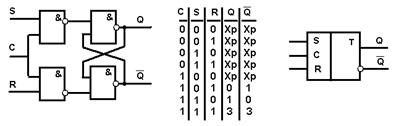

Синхронный RS-триггер в базисе И-НЕ

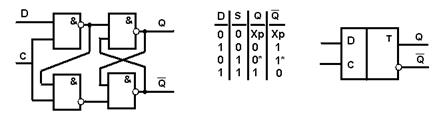

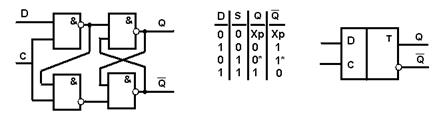

D-триггер в базисе И-НЕ

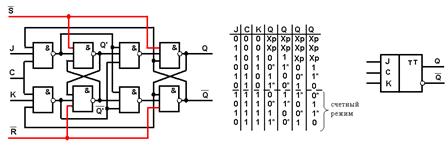

Синхронные однотактные двуступенчатые триггеры.

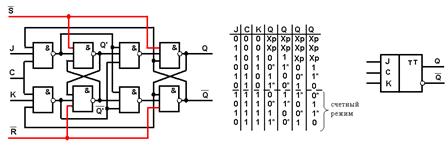

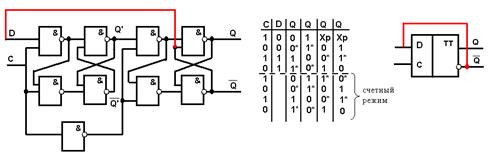

JK-триггер в базисе И-НЕ с запрещающими связями

D-триггер в базисе И-НЕ с инвертором

Триггеры, имеющие в названии типа букву V – имеют дополнительный синхровход с названием V. Триггеры RST и DvT выполняют комбинированные функции, RST – может выполнять функции RS и T-триггеров, DvT – имеет дополнительный синхровход V, может выполнять функции D и T-триггеров.

Регистр – это функциональный узел ЭВМ, предназначенный для записи, хранения, считывания n-разрядного слова информации. Регистры строятся на однотактных или двутактных двуступенчатых триггерах. Они позволяют осуществлять выполнение логических операций, таких как:  а также сдвиг информации на заданное количество разрядов.

а также сдвиг информации на заданное количество разрядов.

Типы регистров различаются:

· по способу записи-считывания – на:

- последовательные – т.е. с последовательной записью и считыванием информации;

- параллельные – т.е. с параллельной записью и считыванием информации;

- последовательно-параллельные – с последовательной записью и параллельным считыванием информации;

- параллельно-последовательные – с параллельной записью и последовательным считыванием информации;

- универсальные – с параллельной и последовательной записью и параллельным и последовательным считыванием информации.

· по фазности поступающей и выходной информации:

- однофазные на D-триггерах;

- парафазные на RS и JK-триггерах;

- комбинированные:

однофазное занесение, парафазная выдача;

o парафазное занесение, однофазная выдача.

· по способу тактирования:

- однотактные, т.е.управляемые одной последовательностью тактовых

сигналов;

- многотактные, т.е.управляемыея несколькими последовательностями

тактовых сигналов.

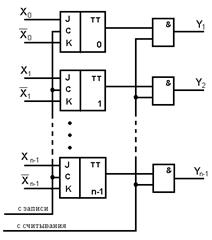

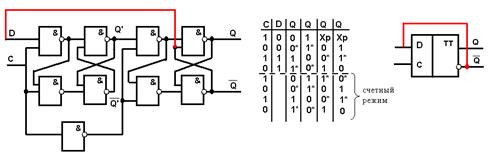

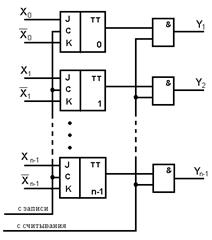

Параллельный регистр на JK-триггерах

Регистр характеризуется парафазным занесением однофазным считыванием информации. Возможна также парафазная выдача информации.

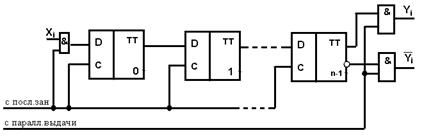

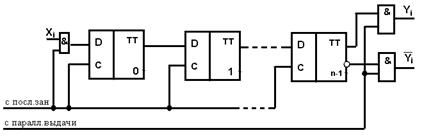

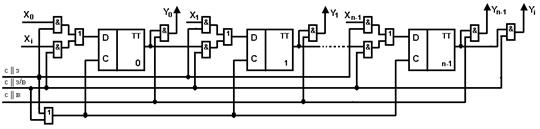

Последовательный регистр на D-триггерах

Регистр характеризуется однофазным занесением информации слева направо и парафазной выдачей информации.

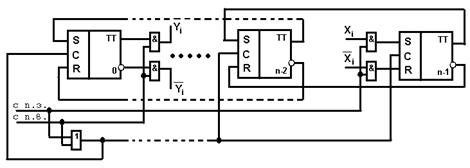

Последовательный регистр на RS-триггерах

В регистре осуществляется парафазное занесение информации справа налево и однофазным считыванием.

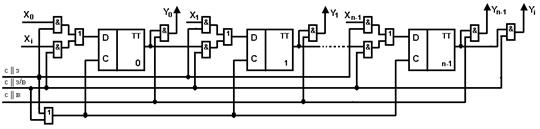

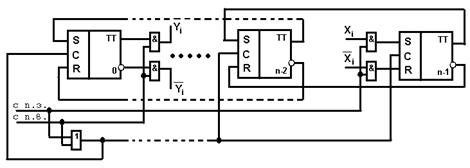

Универсальный регистр на D-триггерах

В регистре реализуется однофазное, последовательное, слева направо и параллельное занесение информации, последовательное и параллельное считывание информации (однофазное).

Счетчик – это функциональный узел ЭВМ, предназначенный для подсчета количества поступивших на его вход сигналов и выдачи его в виде n-разрядного двоичного кода. Максимальное число, до которого может считать счетчик, образует коэффициент пересчета N=2n, где N – разрядность счетчика.

Счетчики строятся на однотактных двуступенчатых Т-триггерах. Они классифицируются по следующим признакам:

- По направлению счета:

- суммирующие;

- вычитающие;

- реверсивные;

- По основанию системы счисления:

- двоичные;

- недвоичные:

а) двоично-десятичные;

б) с произвольным коэффициентом;

- по времени поступления сигналов:

- асинхронные;

- синхронные;

- по способу организации разрядного переноса:

- с последовательным переносом;

- с параллельным переносом;

- с комбинированным (групповым) переносом.

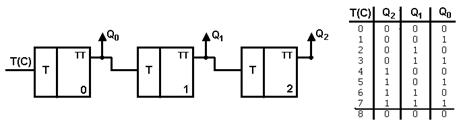

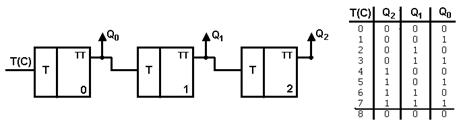

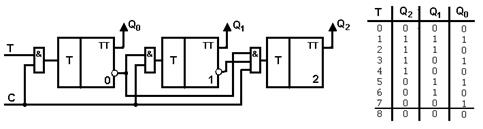

Асинхронный суммирующий двоичный счетчик с последовательным переносом

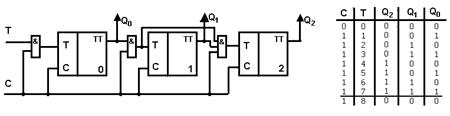

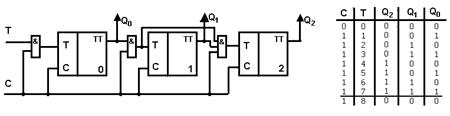

Синхронный суммирующий двоичный счетчик с параллельным переносом. Переключение (подсчет входных сигналов) возможно только в присутствии синхросигнала С.

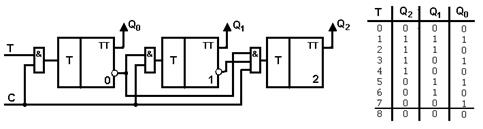

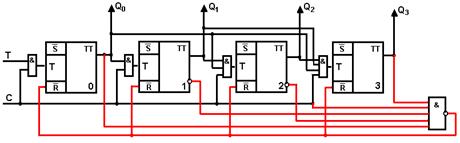

Вычитающий синхронный двоичный счетчик с параллельным переносом

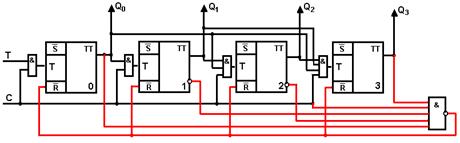

Десятичный синхронный суммирующий счетчик с параллельным переносом.

Схемотехника БИС. Развитие цифровой вычислительной техники характеризуется широким внедрением в технические средства интегральных схем (БИС). Однако рост степени интеграции схем сопровождается ростом их специализации.

Проектирование цифровых устройств на основе универсальных микропроцессорных комплексов частично решает проблему применимости БИС. Программная реализация логики управления здесь осуществляется сравнительно медленно, и микропроцессор зачастую не способен обеспечить необходимое быстродействие. В связи с этим в настоящее время элементные базы высокопроизводительных вычислительных машин составляют полу заказные матричные БИС на основе базовых матричных кристаллов, а также программируемые логические интегральные микросхемы.

Быстродействующие матричные БИС. В матричных БИС микросхемы проектируются на основе базового матричного кристалла (БМК). В БМК несоединенные между собой активные и пассивные компоненты (транзисторы, диоды, резисторы и т.д.) размещаются на постоянных позициях полупроводникового кристалла, образуя базовую ячейку (БЯ). Определенное число БЯ группируется образуя так называемую топологическую ячейку (ТЯ). Топологические ячейки на БМК размещаются регулярно, образуя матрицу одинаковых повторяющихся ячеек. Кроме того, между БЯ имеется трассировочное пространство, в котором размещаются трассы металлических проводников, соединяющих БЯ в функционально законченную БИС. В периферийной области БМК располагаются вспомогательные схемы, обеспечивающие работу БИС, и контактные площадки для подключения внешних выводов.

Литература:

1. К. Хамахер, З. Вранешич, С. Захи. Организация ЭВМ. СПб.: Питер, 2003-848 с.

2. Э. Таненбаум. Архитектура компьютера.-СПб.:Питер, 2003-704с.

а также сдвиг информации на заданное количество разрядов.

а также сдвиг информации на заданное количество разрядов.