Пусть дана таблица 8 состояний детерминированного конечного дискретного автомата. Тогда ситуация 1 и ситуация 2 явно противоречивы. Входные состояния переменных не изменились, а команда по каналу 3 изменила состояние. Это фактически одна и та же ситуация, и команды не должны менять состояние. Если бы произошло чередование ситуаций, то тогда бы эти события можно рассматривать, как дискретный автомат с памятью. В этот раз синтезируется дискретный автомат без соблюдения жёсткой последовательности выполнения очередности тактов (ситуаций), поэтому 10-ю ситуацию исключаем, т.к. она полностью повторяет 2-ю ситуацию, но входит в противоречие с первой[12] по третьему каналу. Ситуации 4-я и 8-я соответствуют дискретному автомату с памятью. С учётом всех этих изменений появляется таблица 9. В таблице 9 первая, пятая, третья и седьмая ситуации для реализации требуют памяти. В таблице 9 состояния, требующие памяти, выделены кружочками.

Таблица 8

| N ситуации

| X1

| X2

| X3

| X4

| U1

| U2

| U3

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 9

| N ситуации

| X1

| X2

| X3

| X4

| U1

| U2

|  U3 U3

|

1

|

|

|

|

|

|  0 0

|

|

|

|

|

|

|

|

|

|  1 1

|

3

|

|

|

|  1 1

|

|  0 0

|

|

|

|

|

|

|

|

|

|

|

5

|

|

|

|

|

|  1 1

|  0 0

|

|

|

|

|

|

|

|

|

|

7

|

|

|

|  1 1

|

|  1 1

|  0 0

|

|

|

|

|

|

|

|

|

|

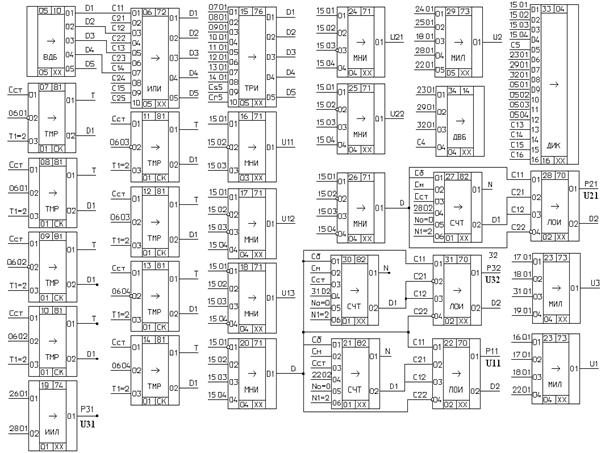

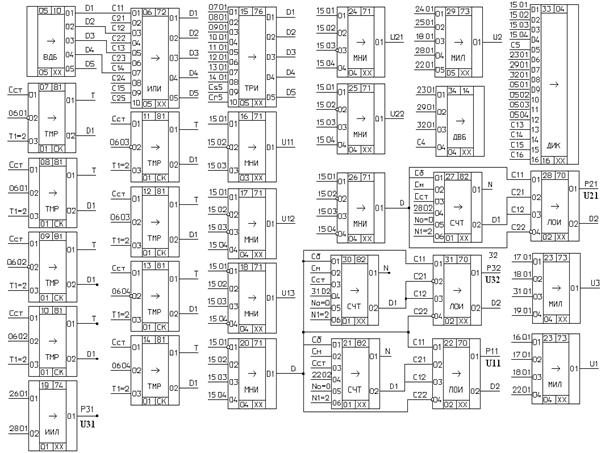

По таблице 9 выпишем функции управления. Будем брать единичные состояния, не связанные с памятью. Те состояния, которые формируются с учётом памяти, добавляются отдельно. В программе для данной функции управления все слагаемые собираются на элементе ИЛИ.

Рис. 42 Память, которая изменяет состояние с нуля на единицу

На рис.42 представлена программа, реализующая память по второму каналу. В данном фрагменте рассмотрена ситуация 1010 первая и пятая для управления по второму каналу U2. Память по первому каналу обозначим в программе P11. Первую память по второму каналу обозначим P21. Вторую память по второму каналу обозначим P22.Сигнал управления по второму каналу обозначили U21 и U22, который изменяет состояние с нуля на единицу.

Аналогичное изменение происходит и по первому каналу (U11) и по второму (U22). U21 – так обозначили первое управление по второму каналу (для первой и пятой ситуации: 1010). U22 – второе управление по второму каналу для третьей и седьмой ситуаций: 0111 (анализируются ситуации, где требуется память).

Рис. 43 Память, которая изменяет состояние с единицы на ноль

На рис.43 представлена программа, реализующая память по третьему каналу. В данном фрагменте рассмотрена ситуация 0111 - третья и седьмая строка из таблицы 9. Сигнал управления обозначили U32, который изменяет состояние с единицы на ноль.

Память П31 формируется для третьей ситуации инверсно по отношению к памяти П21, поэтому на сборку (на ИЛИ) этот сигнал поступает после исключающего ИЛИ (ИИЛ).

Рис. 44 Программа дискретного автомата с памятью

Конфигурационная таблица.

Имя схемы: AVT4UCHP.rem

Дата создания отчета: 14/12/2009(СЮВ)

С И С Т Е М Н Ы Е П А Р А М Е Т Р Ы:

Системный номер контроллера: 3

Модель контроллера: Логическая

Комплектность УСО группы А: 8 ан.вх. и 2 ан.вых.(1)

Комплектность УСО группы Б: 8 д.вх. и 8 д.вых.(5)

Временной диапазон контроллера: Младший(Сек/Мин)

Время цикла: 0.4 сек.

А Л Г О Р И Т М Ы И К О Н Ф И Г У Р А Ц И Я:

Таблица 10

| Ал.б.

| Алгоритм

| Мод

| Вход

| Значение

| Источник

|

|

|

|

| N Имя

|

| Ал.б. Выход

|

|

| ВДБ(10)

|

|

|

|

|

|

| ИЛИ(72)

|

|

|

|

|

|

|

|

| 1 C11

|

| 5 1(D1)

|

|

|

|

| 2 С21

|

|

|

|

|

|

| 3 C12

|

| 5 2(D2)

|

|

|

|

| 4 С22

|

|

|

|

|

|

| 5 C13

|

| 5 3(D3)

|

|

|

|

| 6 С23

|

|

|

|

|

|

| 7 C14

|

| 5 4(D4)

|

|

|

|

| 8 С24

|

|

|

|

| ТМР(81)

|

|

|

|

|

|

|

|

| 1 Сст

|

|

|

|

|

|

| 2 Ссбр

| инверсия

| 6 1(D1)

|

|

|

|

| 3 T1=2

|

|

|

|

| ТМР(81)

|

|

|

|

|

|

|

|

| 1 Сст

|

|

|

|

|

|

| 2 Ссбр

|

| 6 1(D1)

|

|

|

|

| 3 T1=2

|

|

|

|

| ТМР(81)

|

|

|

|

|

|

|

|

| 1 Сст

|

|

|

|

|

|

| 2 Ссбр

| инверсия

| 6 2(D2)

|

|

|

|

| 3 T1=2

|

|

|

|

| ТМР(81)

|

|

|

|

|

|

|

|

| 1 Сст

|

|

|

|

|

|

| 2 Ссбр

|

| 6 2(D2)

|

|

|

|

| 3 T1=2

|

|

|

|

| ТМР(81)

|

|

|

|

|

|

|

|

| 1 Сст

|

|

|

|

|

|

| 2 Ссбр

| инверсия

| 6 3(D3)

|

|

|

|

| 3 T1=2

|

|

|

|

| ТМР(81)

|

|

|

|

|

|

|

|

| 1 Сст

|

|

|

|

|

|

| 2 Ссбр

|

| 6 3(D3)

|

|

|

|

| 3 T1=2

|

|

|

|

| ТМР(81)

|

|

|

|

|

|

|

|

| 1 Сст

|

|

|

|

|

|

| 2 Ссбр

| инверсия

| 6 4(D4)

|

|

|

|

| 3 T1=2

|

|

|

|

| ТМР(81)

|

|

|

|

|

|

|

|

| 1 Сст

|

|

|

|

|

|

| 2 Ссбр

|

| 6 4(D4)

|

|

|

|

| 3 T1=2

|

|

|

|

| ТРИ(76)

|

|

|

|

|

|

|

|

| 1 Cs1

|

| 7 2(D1)

|

|

|

|

| 2 Cr1

|

| 8 2(D1)

|

|

|

|

| 3 Cs2

|

| 9 2(D1)

|

|

|

|

| 4 Cr2

|

| 10 2(D1)

|

|

|

|

| 5 Cs3

|

| 11 2(D1)

|

|

|

|

| 6 Cr3

|

| 12 2(D1)

|

|

|

|

| 7 Cs4

|

| 13 2(D1)

|

|

|

|

| 8 Cr4

|

| 14 2(D1)

|

|

| МНИ(71)

|

|

|

|

|

|

|

|

| 1 C1

|

| 15 1(D1)

|

|

|

|

| 2 C2

| инверсия

| 15 2(D2)

|

|

|

|

| 3 C3

|

| 15 3(D3)

|

|

| МНИ(71)

|

|

|

|

|

|

|

|

| 1 C1

|

| 15 1(D1)

|

|

|

|

| 2 C2

| инверсия

| 15 2(D2)

|

|

|

|

| 3 C3

| инверсия

| 15 3(D3)

|

|

|

|

| 4 C4

|

| 15 4(D4)

|

|

| МНИ(71)

|

|

|

|

|

|

|

|

| 1 C1

| инверсия

| 15 1(D1)

|

|

|

|

| 2 C2

|

| 15 2(D2)

|

|

|

|

| 3 C3

|

| 15 3(D3)

|

|

|

|

| 4 C4

| инверсия

| 15 4(D4)

|

|

| ИИЛ(74)

|

|

|

|

|

|

|

|

| 1 C11

|

| 26 1(D)

|

|

|

|

| 2 C21

|

| 28 1(P21)

|

|

| МНИ(71)

|

|

|

|

|

|

|

|

| 1 C1

| инверсия

| 15 1(D1)

|

|

|

|

| 2 C2

|

| 15 2(D2)

|

|

|

|

| 3 C3

|

| 15 3(D3)

|

|

|

|

| 4 C4

|

| 15 4(D4)

|

|

| СЧТ(82)

|

|

|

|

|

|

|

|

| 1 Cб

|

| 20 1(D)

|

|

|

|

| 2 См

|

|

|

|

|

|

| 3 Сст

|

|

|

|

|

|

| 4 Cсбр

|

| 22 2(D2)

|

|

|

|

| 5 No=0

|

|

|

|

|

|

| 6 N1=2

|

|

|

|

| ЛОИ(70)

|

|

|

|

|

|

|

|

| 1 C11

|

| 20 1(D)

|

|

|

|

| 2 C21

|

| 21 2(D1)

|

|

|

|

| 3 C12

|

| 21 2(D1)

|

|

|

|

| 4 C22

| инверсия

| 20 1(D)

|

|

| МИЛ(73)

|

|

|

|

|

|

|

|

| 1 C1

|

| 16 1(U11)

|

|

|

|

| 2 C2

|

| 17 1(U12)

|

|

|

|

| 3 C3

|

| 18 1(U13)

|

|

|

|

| 4 C4

|

| 22 1(P11)

|

|

| МНИ(71)

|

|

|

|

|

|

|

|

| 1 C1

|

| 15 1(D1)

|

|

|

|

| 2 C2

|

| 15 2(D2)

|

|

|

|

| 3 C3

| инверсия

| 15 3(D3)

|

|

|

|

| 4 C4

|

| 15 4(D4)

|

|

| МНИ(71)

|

|

|

|

|

|

|

|

| 1 C1

|

| 15 1(D1)

|

|

|

|

| 2 C2

| инверсия

| 15 2(D2)

|

|

|

|

| 3 C3

|

| 15 3(D3)

|

|

|

|

| 4 C4

|

| 15 4(D4)

|

|

| МНИ(71)

|

|

|

|

|

|

|

|

| 1 C1

|

| 15 1(D1)

|

|

|

|

| 2 C2

| инверсия

| 15 2(D2)

|

|

|

|

| 3 C3

|

| 15 3(D3)

|

|

|

|

| 4 C4

| инверсия

| 15 4(D4)

|

|

| СЧТ(82)

|

|

|

|

|

|

|

|

| 1 Cб

|

| 26 1(D)

|

|

|

|

| 2 См

|

|

|

|

|

|

| 3 Сст

|

|

|

|

|

|

| 4 Cсбр

|

| 28 2(D2)

|

|

|

|

| 5 No=0

|

|

|

|

|

|

| 6 N1=2

|

|

|

|

| ЛОИ(70)

|

|

|

|

|

|

|

|

| 1 C11

|

| 26 1(D)

|

|

|

|

| 2 C21

|

| 27 2(D1)

|

|

|

|

| 3 C12

|

| 27 2(D1)

|

|

|

|

| 4 C22

| инверсия

| 26 1(D)

|

|

| МИЛ(73)

|

|

|

|

|

|

|

|

| 1 C1

|

| 24 1(U21)

|

|

|

|

| 2 C2

|

| 25 1(U22)

|

|

|

|

| 3 C3

|

| 18 1(U13)

|

|

|

|

| 4 C4

|

| 28 1(P21)

|

|

|

|

| 5 C5

|

| 22 1(P11)

|

|

| СЧТ(82)

|

|

|

|

|

|

|

|

| 1 Cб

|

| 20 1(D)

|

|

|

|

| 2 См

|

|

|

|

|

|

| 3 Сст

|

|

|

|

|

|

| 4 Cсбр

|

| 31 2(D2)

|

|

|

|

| 5 No=0

|

|

|

|

|

|

| 6 N1=2

|

|

|

|

| ЛОИ(70)

|

|

|

|

|

|

|

|

| 1 C11

|

| 20 1(D)

|

|

|

|

| 2 C21

| инверсия

| 30 2(D1)

|

|

|

|

| 3 C12

|

| 30 2(D1)

|

|

|

|

| 4 C22

| инверсия

| 20 1(D)

|

|

| МИЛ(73)

|

|

|

|

|

|

|

|

| 1 C1

|

| 16 1(U11)

|

|

|

|

| 2 C2

|

| 17 1(U12)

|

|

|

|

| 3 C3

|

| 18 1(U13)

|

|

|

|

| 4 C4

|

| 31 1(P31)

|

|

|

|

| 5 C5

|

| 19 1(D1)

|

|

| ДИК(04)

|

|

|

|

|

|

|

|

| 1 С1

|

| 15 1(D1)

|

|

|

|

| 2 С2

|

| 15 2(D2)

|

|

|

|

| 3 С3

|

| 15 3(D3)

|

|

|

|

| 4 С4

|

| 15 4(D4)

|

|

|

|

| 6 С6

|

| 23 1(U1)

|

|

|

|

| 7 С7

|

| 29 1(U2)

|

|

|

|

| 8 С8

|

| 32 1(U3)

|

|

|

|

| 9 С9

|

| 5 1(D1)

|

|

|

|

| 10 С10

|

| 5 2(D2)

|

|

|

|

| 11 С11

|

| 5 3(D3)

|

|

|

|

| 12 С12

|

| 5 4(D4)

|

|

| ДВБ(14)

|

|

|

|

|

|

|

|

| 1 C1

|

| 23 1(U1)

|

|

|

|

| 2 C2

|

| 29 1(U2)

|

|

|

|

| 3 C3

|

| 32 1(U3)

|

Таблица 11

| N ситуации или такта

| Вход

| Выход

|

| X1

| X2

| X3

| X4

| U1

| U2

|

|

|

|

|

|

| U11=1

|

|

|

|

|

|

|

|

| U21=1

|

|

|

|

|

|

| U12=1

|

|

|

|

|

|

|

|

| U22=1

|

|

|

|

|

|

| U13=1

|

|

|

|

|

|

|

| U14=1

|

|

|

|

|

|

|

| U15=1

|

|

Анализ таблицы 25 показывает, что реализация конечного автомата без памяти по классической схеме приведёт к возникновению сбоев в работе автомата. Представим, что допустима любая последовательность ситуаций. Состояния выходных переменных определяется только состоянием входных переменных. Допустим, что команды U1 и U2 - это включение асинхронных двигателей первого или второго соответственно.

Рассмотрим формирование второй ситуации (N=2). Состояние переменной Х2 и переменной Х3 в таблице 25 равны единице. Допустим сигналы Х2 и Х3 идут с конечных выключателей, поэтому в реальных условиях они не могут изменить своё состояние в одно мгновение. Время задержки изменения состояния Х2 и Х3, допустим, составляет одну – две секунды. Если вначале из состояния «0» переменная Х2 перешла в состояние «1», то такое состояние соответствует первой ситуации. На выходе U1 сформируется команда U1=1 и включится первый двигатель. Допустим, через секунду перейдёт в единичное состояние и переменная Х3, т.е. появится вторая ситуация. Сформируются состояния переменных, соответствующие второй ситуации. В этом случае, т.е. через секунду, первый двигатель должен отключиться и, согласно новой комбинации, должен включиться второй двигатель. В этом случае произойдёт ложное кратковременное включение первого двигателя. При каждом включении двигателя происходят броски по току, нагрев двигателя и т.д.

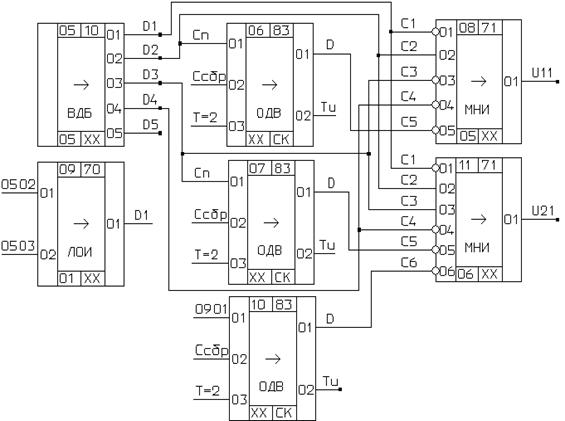

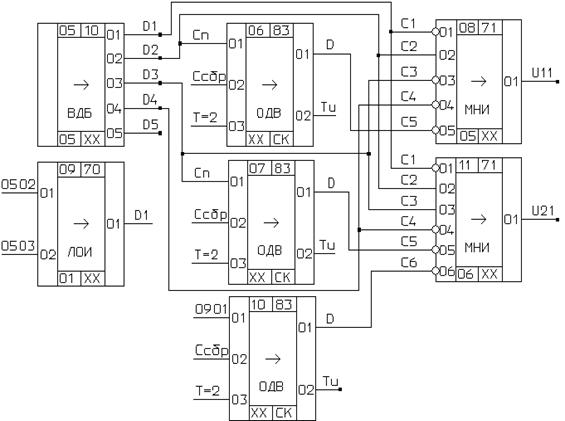

На рис.44 представлена программа (primsinx.rem) поканальной синхронизации, уменьшающая вероятность ложного формирования команды. Следует обратить внимание, что обозначение команд, приведённое в таблице 24, сохраняется и в программе (рис.44). На выходе алгоблока 5 имеются пять дискретных переменных: D1, D2, D3, D4 и D5, которые соответствуют нашим обозначениям переменных X1, X2, X3, X4 и X5. Обозначения D1, D2, D3, D4 и D5 приняты по умолчанию для алгоритма ВДБ разработчиками контроллера. В алгоблоке 05 размещён алгоритм опроса дискретных сигналов по пяти каналам. Анализ работы программы начнём с первой ситуации. Переменная D2 поступает одновременно на вход Сп (пуск) одновибратора (ОДВ) и на второй вход многовходового элемента И (алгоблок 08). Команда U11 появилась бы сразу, как только состояние переменной Х2 стало 1, если бы не одновибратор (ОДВ), расположенный в алгоблоке 06. Зная, что задержка между сигналами при изменении состояния не превышает двух секунд, с помощью ОДВ фактически осуществляется задержка формирования команды U11. Таким образом, на выходе алгоблока 08 появится команда U11=1, только при состоянии переменных, соответствующих первой ситуации: 0100. Допустим, через секунду после появления D2=1 появится сигнал D3=1, который поступает одновременно на вход Сп (пуск) одновибратора (алгоблок 07), инверсно на вход 3 алгоблока 08 и на второй вход многовходового элемента И (алгоблок 11). Поэтому команда U11 не появится, даже если сигнал с выхода ОДВ станет равным нулю. Если сигнал D3 не появится, спустя две секунды плюс время цикла контроллера, то на выходе алгоблока 08 появится команда U11=1. Рассмотрим формирование команды U21, появляющейся в результате реализации второй ситуации 0110. Ближайшими состояниями к этой ситуации являются: пятая ситуация 1110 и шестая ситуация 0010. Общей единицей для трёх ситуаций является состояние Х3=1. Поэтому сигнал с D3 идёт на ОДВ (алгоблок 07) и на сборку (алгоритм И, алгоблок 11). Таким образом, идёт выжидание: появятся ещё единицы или нет. Третья переменная сама себя держит две секунды. Предположим, что появился сигнал D2=1. Мы видим, что вторая ситуация и пятая отличаются состоянием Х1. Для исключения ложного формирования команды U21 ОДВ (алгоблок 10) формирует задержку. Запуск ОДВ происходит с алгоблока 09. В алгоблоке 09 размещена двухвходовая операция И. На вход алгоблока 09 поступают два сигнала: D2 и D3. Если сигнал D1=1 не появляется, то разрешается формировать команду U21=1. Если же появляется сигнал D1=1, с задержкой относительно сигналов D2 и D3 не более двух секунд, то команда U21 не подаётся, а формируется команда U31=1 и т.д.

Синхронизацию сигналов можно осуществлять всех каналов одновременно. Например, установлено, что каждая ситуация формируется в течение не более 5-ти секунд. С появлением очередной единицы по любому входному каналу (алгоблок 5) формируется задержка по всем сборкам (алгоблок 12, алгоритм ОДВ). На выходе сборок команды появятся только спустя пять секунд. Пример групповой синхронизации представлен программой (sinxron5.rem) на рис.45.

На каждом из пяти выходов алгоблока 5 формируются состояния дискретных переменных D1,…,D5. Затем эти сигналы поступают на одновибраторы (ОДВ) и с них на многовходовой элемент ИЛИ (алгоблок 11) Выход алгоблока 11 связан с ОДВ (алгоблок 12). Пятисекундный импульс с ОДВ (алгоблок 12) поступает инверсно на все сборки: алгоблоки с 13-го по 19-й (МНИ – многовходовой элемент И). На эти же сборки поступают сигналы D1, …, D4. Например, на сборке (алгоблок 13) формируется первая ситуация, соответствующая состоянию переменных: 0100. Сигнал с ОДВ (алгоблок 12, алгоритм ВДБ) осуществляет задержку, за время которой формируется новая ситуация и выдаётся команда управления: U11, U21, U22, U13, …, U15.

Рис. 45 Поканальная синхронизация состояний для двух ситуаций

U3

U3

0

0

1

1

1

1

0

0

1

1

0

0