История развития пистолетов-пулеметов: Предпосылкой для возникновения пистолетов-пулеметов послужила давняя тенденция тяготения винтовок...

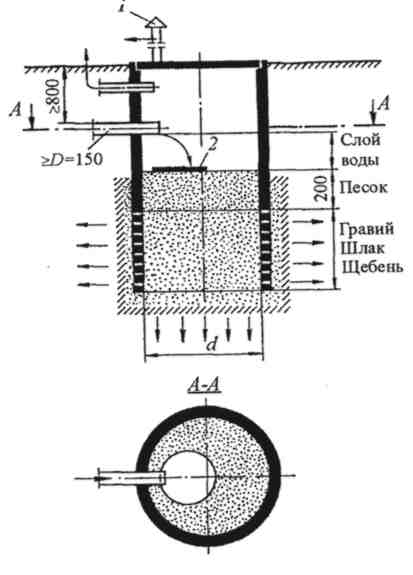

Общие условия выбора системы дренажа: Система дренажа выбирается в зависимости от характера защищаемого...

История развития пистолетов-пулеметов: Предпосылкой для возникновения пистолетов-пулеметов послужила давняя тенденция тяготения винтовок...

Общие условия выбора системы дренажа: Система дренажа выбирается в зависимости от характера защищаемого...

Топ:

Методика измерений сопротивления растеканию тока анодного заземления: Анодный заземлитель (анод) – проводник, погруженный в электролитическую среду (грунт, раствор электролита) и подключенный к положительному...

Марксистская теория происхождения государства: По мнению Маркса и Энгельса, в основе развития общества, происходящих в нем изменений лежит...

Интересное:

Уполаживание и террасирование склонов: Если глубина оврага более 5 м необходимо устройство берм. Варианты использования оврагов для градостроительных целей...

Национальное богатство страны и его составляющие: для оценки элементов национального богатства используются...

Что нужно делать при лейкемии: Прежде всего, необходимо выяснить, не страдаете ли вы каким-либо душевным недугом...

Дисциплины:

|

из

5.00

|

Заказать работу |

|

|

|

|

Для получения более детальное представление о структуре и функциях устройств ВМ рассмотрим фон-неймановскую ВМ в виде гипотетической машины с аккумуляторной архитектурой.

Архитектура на базе аккумулятора исторически возникла одной из первых. В ней для хранения одного из операндов арифметической или логической операции в процессоре предусмотрен выделенный регистр – аккумулятор. Изначально оба операнда находятся в памяти, до выполнения операции один из операндов загружается в аккумулятор[11]. После выполнения команды результат пересылается в аккумулятор, если он не является операндом для последующей команды, то он сохраняется в ячейке памяти.

| |||

|

Типичная архитектура ВМ на базе аккумулятора приведена на рис. 3.1. Достоинством аккумуляторной архитектуры считаются короткие команды и простота декодирования команд.

Для упрощения схемы гипотетической машины принимаются следующие характеристики вычислительной машины:

· все команды одноадресные. Адресная часть команды содержит адрес только одного из операндов. При выполнении операций с двумя операндами предполагается нахождение в аккумуляторе второго операнда (его адрес не указан в команде). Результат остается в аккумуляторе;

· длина команд и данных совпадает с разрядностью ячеек памяти (адрес очередной команды в памяти может быть получен увеличением на 1 адреса текущей команды, для чтения любой команды или операнда достаточно одного обращения к памяти).

На функциональной схеме (рис. 3.2) показаны типовые узлы каждого из основных устройств ВМ, связи между узлами.

|

|

Устройство управления (УУ)- важнейшая часть ВМ, организующая автоматическое выполнение программы (путём реализации функций управления) и обеспечивающая функционирование ВМ как единой системы. При этом ВМ рассматривается как совокупность элементов, между которыми происходит пересылка информации, в ходе которой эта информация может подвергаться определённым видам обработки. Пересылка информации между любыми элементами ВМ инициируется своим сигналом управления (СУ), то есть управление вычислительным процессом сводится к выдаче нужного набора СУ в нужной временной последовательности. Основной функцией УУ является формирование управляющих сигналов, отвечающих за извлечение команд из памяти в порядке, определяемым программой, и последующее исполнение этих команд. Кроме этого, УУ формирует СУ для синхронизации и координации внутренних и внешних устройств ВМ.

Арифметико-логическое устройство обеспечивает арифметическую и логическую обработку двух входных переменных, в результате которой формируется выходная переменная. Функции АЛУ обычно сводятся к простым логическим и арифметическим операциям, а также операциям сдвига. Помимо результатов операции АЛУ формирует ряд признаков результата (флагов), характеризующих полученный результат и события, произошедшие в процессе его получения (равенство нулю, чётность, перенос, переполнение, знак и т.д.). Флаги могут анализироваться в УУ для принятия решения о дальнейшей последовательности выполнения команд программы.

| |||

| |||

Рис. 3.2. Функциональная схема гипотетической фон-неймановской ВМ.

УУ и АЛУ тесно взаимосвязаны и их обычно рассматривают как единое устройство, известное как центральный процессор (ЦП). Помимо УУ и АЛУ в процессор входит также набор регистров общего назначения (РОН), служащих для промежуточного хранения информации в процессе её обработки.

Узлы УУ

|

|

Устройство управления организует автоматическое выполнение программ и функционирование ВМ как единой системы.

Счетчик команд (СК) – это узел УУ, который указывает какую команду следует выполнять дальше. Согласно принципу программного управления, соседние команды программы располагаются в ячейках памяти со следующими по порядку адресами. Перед началом вычислений в СК заносится адрес ячейки памяти первой команды. В процессе выполнения каждой команды содержимое СК увеличивается на длину выполняемой команды, либо (для команды перехода) в СК заносится адрес точки перехода. По завершению текущей команды адрес следующей команды всегда берется из СК. В ряде ВМ счетчик команд реализуется в виде обычного регистра, увеличение его содержимого производится внешней схемой.

Регистр команды (РК). Счетчик команд определяет адрес команды, выбираемый из памяти на РК. В РК команда хранится в течение всего времени её выполнения. Так как любая команда содержит два поля, то РК иногда рассматривают как совокупность двух регистров - регистра кода операций (РКоп) и регистра адреса (РА). Если команда занимает более одной ячейки памяти (несколько последовательных байтов), то код операции всегда находится в первом слове команды. По коду операции определяется необходимость считывания из памяти и загрузки в РК остальных слов команды. Выполнение команды начинается только после занесения в РК её полного кода.

Указатель стека (УС). Это регистр, где хранится адрес вершины стека. В реальных вычислительных машинах стек реализуется в виде участка основной памяти, обычно расположенной в области наибольших адресов. Заполнение стека происходит в сторону уменьшения адресов, при этом вершина стека – это ячейка, куда была произведена последняя по времени запись. При выполнении операции push (занесение в стек) содержимое УС сначала уменьшается на единицу, после чего используется в качестве адреса, по которому производится запись. Соответствующая ячейка становится вершиной стека. Считывание из стека (операция pop) происходит из ячейки, на которую указывает текущий адрес УС, после чего содержимое указателя стека увеличивается на единицу. Вершина стека опускается, а считанное слово считается удалённым из стека (физически считанное слово осталось в ячейке памяти).

|

|

Регистр адреса памяти (РАП) предназначен для хранения адреса ячейки основной памяти вплоть до завершения операции (считывания или записи) с этой ячейкой. Наличие РАП позволяет компенсировать различия в быстродействии ОП и прочих устройств машины.

Регистр данных памяти (РДП) призван компенсировать разницу в быстродействии ОП и устройств, являющихся источником или потребителем хранимой информации. При чтении в РДП заносится содержимое ячейки основной памяти, при записи – помещается информация, которую следует сохранить в ячейки основной памяти. Момент считывания из ячейки определяется сигналом ЧтЗУ, момент записи - сигналом ЗпЗУ.

Дешифратор кода операции (ДКоп) преобразует код операции в форму, требуемую для работы микропрограммного автомата (МПА). Информация после декодирования (унитарный код[12] УнитК) определяет последующие действия МПА, её вид зависит от организации МПА.

Микропрограммный автомат (МПА) является центральным узлом УУ. МПА формирует последовательность сигналов управления, в соответствии с которыми производятся все действия, необходимые для выборки из памяти и выполнения команд. Исходной информацией для МПА служат: декодированный код операций, состояние признаков (флагов), характеризующих результат предшествующих вычислений, а также внешних запросов на прерывание текущей программы и переход на программу обслуживания прерываний.

Узлы АЛУ

АЛУ выполняет сложение, вычитание и другие простые операции над входными данными и помещает результат в выходной регистр. арифметической и обработки данных.

Операционный блок (ОПБ) выполняет арифметические и логические операции над поданными на вход операндами. Выбор конкретной операции определяется кодом операции команды. На нашей схеме код операции поступает после предварительной дешифрации из регистра команд, в реальных машинах КОп зачастую поступает из МПА после преобразования в иную форму.. Операционные блоки АЛУ строятся как комбинационные схемы им не обладают внутренней памятью, поэтому до момента сохранения результата операнды должны присутствовать на входе блока.

|

|

Регистры операндов РХ и РУ обеспечивают сохранение операндов на входе операционного блока вплоть до получения результата операции и его записи (в аккумулятор).

Регистр признаков (РПрз) предназначен для фиксации и хранения признаков результата последней выполненной команды (флагов). Такие признаки информируют о равенстве результата нулю, о знаке результата, о возникновении переноса из старшего разряда, переполнении разрядной сетки и т.д. Содержимое РПрз обычно используется УУ для реализации условных переходов по результатам операций АЛУ[13]. Для каждого признака отводится отдельный разряд в РПрз.

Аккумулятор (Акк)- это регистр, выполняющий разнообразные функции: в него предварительно загружается один из операндов, участвующих в арифметической или логической операции, хранится результат предыдущей команды, заносится результат очередной операции, через Акк зачастую производятся операции ввода вывода. Аккумулятор в равной мере можно отнести как к АЛУ, так и к УУ, а в ВМ с регистровой архитектурой его можно рассматривать как один из регистров общего назначения.

Основная память.

Вне зависимости от типа используемых микросхем основная память (ОП) представляет собой массив запоминающих элементов (ЗЭ), организованных в виде ячеек, способных хранить некую информацию, обычно один байт. Каждая ячейка имеет свой уникальный адрес. Ячейки ОП образуют матрицы. Выбор ячейки обеспечивает дешифратор адреса памяти, который преобразует поступивший из РАП адрес ячейки в разрешающие сигналы, подаваемые на горизонтальные (строки) и вертикальные (столбцы) линии матрицы, на пересечении которых расположена адресуемая ячейка. Обычно приходится использовать несколько микросхем памяти, при этом процесс обращения к ячейке состоит из выбора микросхемы (на основании старших разрядов адреса) внешними схемами и выбора ячейки внутри микросхемы (младшие разряды адреса).

Модуль ввода/вывода

Задачей модуля ввода/вывода (МВВ) является обеспечение подключения к ВМ различных периферийных устройств (ПУ) и обмена информацией с ними. На нашей схеме МВВ состоит из дешифратора порта ввода/вывода, множества портов ввода и множества портов вывода.

· Периферийное устройство (ПУ)– это устройство, которое конструктивно отделено от центральной части и имеет собственное управление, выполняет запросы микропроцессора без его непосредственного вмешательства.

· Интерфейс – соглашение о связи с другими устройствами.

Порты ввода и порты вывода. Портом называют схему, ответственную за передачу информации из ПУ ввода в аккумулятор АЛУ (порт ввода) или из аккумулятора на ПУ вывода (порт вывода). Схема обеспечивает электрическое и логическое сопряжение ВМ с подключенным к нему периферийным устройством.

|

|

Различают два типа коммуникационных портов:

· Последовательный (serial) - используется для побитового обмена с медленнодействующими или удаленными ПУ.

· Параллельный (parallel) - используется для обмена с быстродействующими ПУ.

Каждое ПУ подключается к своему порту, каждый порт имеет свой уникальный адрес, адрес порта указывается в адресной части команды ввода/вывода.

Дешифратор номера порта ввода/вывода обеспечивает преобразование номера порта в сигнал, разрешающий операцию ввода или вывода на соответствующем порте. Непосредственно ввод (вывод) происходит при поступлении из МПА сигнала Вв или Выв.

Цикл команды.

Функционирование вычислительной машины можно описать как последовательность пересылок информации между ее узлами и элементарных действий, выполняемых в узлах. Любое элементарное действие производится при поступлении из микропрограммного автомата УУ соответствующего сигнала управления (СУ). Возможная частота формирования сигналов на выходе автомата определяется синхронизирующими импульсами (ТИ), поступающими от генератора тактовых импульсов (ГТИ). Элементарные пересылки или преобразования информации, выполняемые в течение одного такта сигналов синхронизации, называются микрооперациями. В течение одного такта могут одновременно выполняться несколько микроопераций. Совокупность сигналов управления, порождающих микрооперации, выполняемые в одном такте, называют микрокомандой. Относительно сложные действия, осуществляемые вычислительной машиной в процессе ее работы реализуются как последовательность микроопераций и могут быть заданы последовательностью микрокоманд, называемой микропрограммой. Реализует микропрограмму (вырабатывает управляющие сигналы, задаваемые ее микрокомандами) микропрограммный автомат (МПА).

Действия, требуемые для выборки и выполнения команды, называют циклом команды. В общем случае цикл команд включает в себя несколько этапов:

· выборка команды;

· формирование адреса следующей команды

· декодирование команды;

· вычисление адресов операндов;

· выборка операндов;

· исполнение операции;

· запись результата.

В зависимости от типа команды ряд этапов могут отсутствовать.

Рассмотрим более подробно каждый из этих этапов, имея в виду, что приводимые алгоритмы являются приближенными.

|

|

после размещения КОп в РК производится его декодирование. Если команды не БП/УП, то команды располагаются в естественном порядке следования. Команда передаётся на выполнение либо в АЛУ, либо в МПА

после размещения КОп в РК производится его декодирование. Если команды не БП/УП, то команды располагаются в естественном порядке следования. Команда передаётся на выполнение либо в АЛУ, либо в МПА

Рис. 3.3. Упрощенный алгоритм выборки и декодирования команды.

Этап выборки команды. По адресу, хранимому в счётчике команд (СК), двоичный код команды извлекается из памяти и помещается в регистр команд. На рис.3.3 приведен упрощенный алгоритм выборки команды и ее декодирования команд, длина которых совпадает с разрядностью ячейки памяти. Здесь и далее на блок-схеме в левом верхнем углу функционального блока указывается номер соответствующего действия приведенного на фрагменте функциональной схемы фон-неймановской ВМ (рис.3.4), выдаваемые МПА сигналы управления указаны над пунктирными стрелками, название СУ состоит из двух частей – первые символы обозначают откуда будет передавать информация, а во второй части – куда (например: СУ СКРАП соответствует передачи адреса команды из СК на РАП).

| |||

|

Система команд многих ВМ предполагает несколько форматов команд, причем в различных форматах команда может занимать 1, 2 и более ячеек. Этап выборки команды может считаться завершенным лишь после того, как в РК будет помещен полный код команды. Информация о фактической длине команды содержится в полях кода операции и способа адресации. Обычно эти поля расположены в первом слове команды, для выяснения необходимости продолжения считывания команды требуется декодировать команду.

Этап формирование адреса следующей команды. Для фон-неймановских машин характерно размещение соседних команд программы в смежных ячейках памяти. Если извлечённая команда ненарушает естественного порядка выполнения программы, то для вычисления адреса следующей команды содержимое СК увеличивается на длину текущей команды. Длина команды вычисляется в ходе предварительного декодирования. Если извлечённая команда может изменить последовательность выполнения программы, то процесс формирования адреса следующей команды переносится на этап исполнения операции.

Этап декодирования команды. ЦП расшифровывает находящийся в РК код команды и выясняет:

· длину команды (требуется ли дозагрузка остальных слов команды, например: дочитать адрес одного из операндов либо адрес хранения результата);

· какие последующие действия нужны для выполнения данной команды;

· местонахождение операндов (номера регистров, адрес ячейки ОП), т.е. способ адресации;

· если команда формирует результат, то куда результат должен быть записан.

По результатам декодирования производится подготовка электронных схем ВМ к выполнению предписанных командой действий.

Этап вычисления адресов операндов. Этап имеет место, если в процессе декодирования выясняется, что команда использует операнды. Если операнды размещаются в ОП, то вычисляются их исполнительные адреса с учётом указанного в команде способа адресации.

| |||

|

Этап выборки операндов. Исполнительные адреса, вычисленные на предыдущем этапе, используются для считывания операндов из ОП и занесения их на определённые регистры процессора (чаще операнды предварительно заносятся на специальные вспомогательные регистры процессора, а их пересылка на вход АЛУ происходит на этапе исполнения операции).

Этап исполнения операции. На этом этапе реализуется указанная в команде операция, содержание этапа соответствует текущей команде.

Этап записи результата присутствует в цикле тех команд, которые предполагают занесение результата в регистр или ячейку ОП (РА ->РАП одновременно Акк ->РДП ->ОП).

Пример выполнения программы.

Для анализа стандартных циклов команд составим программу сложения двух чисел и вывода суммы на устройство вывода, если эта сумма не равна нулю. Список необходимых команд приведен в табл.3.1, программа – в табл.3.2.

Предположим, что команды программы будут размещаться в основной памяти, начиная с адреса 300, а операнды- с адреса 400. Результат выводится на порт с номером 5.

Таблица 3.1. Команды гипотетической ВМ.

| КОп | АЧ | Описание |

| LDA | Adr | Загрузка в аккумулятор содержимого ячейки ОП с адресом Adr |

| ADD | Adr | Сложение содержимого аккумулятора с содержимым ячейки ОП с адресом Adr. Результат остаётся в аккумуляторе |

| BRZ | Adr | Переход к команде, хранящейся по адресу Adr, если результат предыдущей арифметической операции равен 0, иначе естественный порядок вычислений не нарушается |

| OUT | PortN | Вывод содержимого аккумулятора на ПУ, подключённое к порту с номером PortN |

| HLT | Останов вычислений |

Таблица 3.4. Программа к рассматриваемому примеру

| Адрес ОП | Код операции | Адрес ячейки или номер порта |

| LDA | ||

| ADD | ||

| BRZ | ||

| OUT | ||

| HLT | ||

| Операнд 1 | ||

| Операнд 2 |

Перед запуском программы в СК необходимо занести адрес ячейки ОП, содержащей первую выполняемую команду программы, то есть 300.

Этапы выборки и декодирования команды, формирование адреса следующей команды были рассмотрены ранее (рис. 3.3, 3.4). На рисунке 3.5 представлен алгоритм выполнения программы, загрузка счетчика команд и декодирование команд программы в алгоритме опущены, на рисунке 3.6 приведена функциональная схема ВМ с указанием соответствующих сигналов управления, вырабатываемых МПА.

Исполнение операции загрузки аккумулятора. Команда LDA 400 обеспечивает занесение в аккумулятор содержимого ячейки ОП с адресом 400 (выполнение микрокоманд 1-3 на рис 3.6).

Исполнение операции сложения. Команда ADD 401 ( выполнение микрокоманд 1, 2, 4, 5 на рис 3.6).обеспечивает суммирование содержимого аккумулятора с содержимым ячейки 401 ( вторым операндом ). Результат сложения остаётся в аккумуляторе (микрокоманда 6). Одновременно с этим в АЛУ формируются признаки результата.

Исполнение операции условного перехода. Для изменения порядка выполнения программы используются команды условного и безусловного перехода (команда BRZ 304).Адрес перехода хранится в адресном поле команды. Команда анализирует хранящийся в РПрз признак (флаг) нулевого результата. При нулевом значении флага (условие перехода не выполнено) естественный порядок выполнения программы не нарушается (микрокоманда 7), при единичном значении флага в СК заносится содержимое РА (микрокоманда 8), т.е. значение 304.

Исполнение операции вывода. Команда OUT 5 обеспечивает вывод содержимого аккумулятора в периферийное устройство, подключённое к порту вывода с номером 5. Для выполнения команды по СУ РАДВВ (микрокоманда 9) адресная часть команды из РА поступает на вход дешифратора номера порта ввода/вывода для выбора требуемого порта. В следующем такте по сигналу Выв содержимое аккумулятора передается на подключенное к этому порту ПУ.

Исполнение команды останова. Команда HLT обеспечивает приостановку программы, т.е. завершает вычисления в программе. При этом вырабатывается сигнал Ост, извещающий операционную систему о завершении текущей программы.

3.4 Система прерываний.

|

|

|

o Ситуация, требующая каких – либо действий (реакции) микропроцессора при возникновении определенного события, называется прерыванием (interrupt).

Необходимую реакцию на события обеспечивает система прерывания.

o Под системой прерывания понимают комплекс аппаратных и программных средств, обеспечивающих выявление и обработку прерываний.

Аппаратные прерывания обеспечивают реакцию процессора на события, происходящие асинхронно по отношению к исполняемому коду программы. Процессоры семейства х86 поддерживают таблицу, содержащую определения до 256 процедур обслуживания прерываний (таблица векторов прерываний, размещается в начальных ячейках оперативной памяти).

Прерывания делятся на следующие категории:

· Внешние аппаратные прерывания (маскируемые и немаскируемые)– возникают в результате событий вне МП (нажатие клавиши клавиатуры).

· Внутренние аппаратные прерывания – вырабатываются самимпроцессором или сопроцессором (попытка деления на нуль).

· Программно-вызываемые прерывания – инициируются выполняемой программой (любые функции ввода – вывода информации, которые требуют сервисных услуг DOS).

Последний тип прерываний в прямом смысле прерыванием не является, поскольку представляют собой лишь специфический способ вызова процедур – не по адресу, а по номеру в таблице.

Обработка прерываний сводится к приостановке исполнения программы, вместо которой начинает выполняться программа, называемая обработчиком прерываний. После её реализации выполнение прерванной программы может быть продолжено, что зависит от типа прерывания.

Основные действия обработчика прерываний сводятся к следующему:

· Условия возникновения прерывания проверяются процессором на границе инструкций. Это означает, что все шинные операции текущей инструкции будут завершены до начала обработки прерывания.

· Процессор сохраняет в стеке слово состояния (регистры флагов, кодового сегмента, указатель следующей инструкции), сбрасывает флаг разрешения прерываний (IF) и вызывает процедуру обработки, точка входа в которую описана в таблице прерываний, хранящейся в ОЗУ.

· Выполнение процедуры обработки. Процедура обработки завершается инструкцией (IRET), по которой из стека восстанавливаются автоматически сохраненные регистры (в регистре флагов прерывания разрешены).

· Процессор начинает выполнение инструкции, следующей за той, после которой исполнялось прерывание.

Если имеется только одно устройство ввода-вывода, то сложностей с обработкой прерываний не возникает. Однако в реальных условиях существует некоторая вероятность, что во время выполнения процедуры обработки прерывания одного устройства другое устройство ввода-вывода тоже захочет произвести свое прерывание. Для разрешения подобной ситуации каждому из устройств приписывается определенный приоритет (высокий для более критичных и низкий для менее критичных устройств). Центральный процессор тоже должен иметь приоритеты, которые определяются по одному из полей слова состояния программы.

Если выполняется процедуры обработки прерывания с приоритетом n, то попытка другого устройства с более низким приоритетом будет игнорироваться, пока процедуры обработки прерывания не завершится и пока центральный процессор не возвратиться к выполнению программы более низкого приоритета. С другой стороны, прерывания, поступающие от устройств с более высоким приоритетом, должны выполняться без задержек.

Со времен процессора 8088 все процессоры Intel имеют два уровня (приоритета) прерываний: маскируемые и немаскируемые прерывания. Немаскируемые прерывания обычно используются только для сообщения об очень серьезных ситуациях, например об ошибках четности в памяти. Все устройства ввода- вывода используют одно маскируемое прерывание.

Глава 4. Память.

Организация памяти.

4.1.1. Основные принципы.

Память компьютера предназначена для кратковременного и долговременного хранения информации – кодов команд и данных. Информация в памяти хранится в двоичных кодах, каждый бит – элементарная ячейка памяти - может принимать значения «0» или «1». Каждая ячейка памяти имеет свой адрес, однозначно её идентифицирующий в определенной системе координат. Минимальной адресуемой ячейкой хранения информация в памяти обычно является байт, состоящий, как правило, из 8 бит.

Существуют процессоры и компьютеры с разрядностью обрабатываемого слова не кратной 8 (например: 5, 7, 9 …), и их байты не восьмибитные. Обычно длина машинного слова составляет от 16 до 64 бит. Последовательные байты имеют адреса 0, 1, 2 и т.д. при этом старшие байты слова имеют больший адрес, чем младшие (адресом слова является адрес его младшего байта). Это так называемый обратный порядок байтов, он стал использоваться в 8088 процессоре с шиной данных в один байт.

Со времени появления больших (по размеру) компьютеров сложилось деление памяти на внутреннюю и внешнюю. Под внутренней подразумевалась память, расположенная внутри процессорного «шкафа» (или плотно к нему примыкающая). Классификация памяти применительно к ПК:

§ процессорная память – наиболее скоростной вид памяти (регистры, кэш-память первого уровня) обычно размещается на общем кристалле с центральным процессором, регистры общего назначения вообще считаются частью ЦП;

§ внутренняя память – электронная (полупроводниковая) память, устанавливаемая на системной плате или на платах расширения. К внутренней памяти относят основную память, кэш-память второго и последующих уровней;

§ внешняя память – медленные запоминающие устройства большой емкости, реализованные в виде устройств с различными принципами хранения информации и обычно с подвижными носителями. Память называют внешней, поскольку к ядру ВМ она подключаются аналогично устройствам ввода/вывода.

В настоящее время в состав внешней памяти входят устройства магнитной (дисковой и ленточной) памяти, оптической и магнитооптической памяти, память на звуковой плате, память у принтера и т.д., то есть память периферийных устройств. Устройства внешней памяти могут размещаться как в системном блоке компьютера, так и в отдельных корпусах.

Для процессора непосредственно доступной является внутренняя память, доступ к которой осуществляется по адресу, заданному программой. Большинство компьютеров имеют линейное адресное пространство, которое простирается от адреса 0 до обычно 232 байтов или 264 байтов. Для внутренней памяти характерен одномерный (линейный) адрес, который представляет собой одно двоичное число определенной разрядности.

Внутренняя память подразделяется на оперативную, информация которой может изменяться процессором в любой момент времени, и постоянную, информацию которую процессор может только считывать. Когда предполагается, что программа будет находиться в памяти постоянно, она обычно располагается в постоянном запоминающем устройстве (ПЗУ, ROM - R ead O nly M emory - память только для считывания). ПЗУ обычно является кристаллом интегральной микросхемы с неизменяемой программой.

Оперативная память - это основная часть внутренней памяти, служит для хранения информации и для дальнейшей ее передачи процессору, жесткому диску, другим внешним устройствам. Она располагается в специальных разъемах на материнской плате. В оперативной памяти хранятся программы и данные, с которыми работает центральный процессор. Оперативная память обозначают как RAM (Random Access Memory - память с произвольным доступом). Понятие произвольного доступа означает, что можно обращаться к ячейкам оперативной памяти, начиная с любого адреса в любом порядке, причем как по чтению, так и по записи.

Оперативная память изготавливается в виде микросхем, крепящихся на специальных пластинах. При включении ВМ операционная система загружается в оперативную память, затем в нее загружаются программы приложения (например Word) и данные (например документы). Центральный процессор управляет загрузкой программы, данных в оперативную память и далее работает с данными, находящимися в оперативной памяти, а не на жестком диске. Если требуются данные с жесткого диска, то информация предварительно загружается в оперативную память, после обработки ЦП она вначале загружается в оперативную память и затем переносится на жесткий диск. То есть центральный процессор работает с инструкциями и данными, которые находятся в оперативной памяти, а все другие устройства (диски, магнитная лента, модемная связь и пр.) действуют через нее.

Внешняя память адресуется более сложным образом - каждая её ячейка имеет свой адрес внутри некоторого блока, который, в свою очередь, имеет многомерный адрес. Во время физических операций обмена данный блок может быть считан или записан только целиком. В случае одиночного дискового накопителя адрес блока будет трехмерным: номер поверхности (головки), номер цилиндра и номер сектора. В современных накопителях этот трехмерный адрес часто заменяют линейным номером – логическим адресом блока, а его преобразованием в физический адрес занимается внутренний контроллер накопителя. Поскольку дисковых накопителей в компьютере может быть несколько, то в адресации дисковой памяти участвует и номер накопителя, и номер канала интерфейса. С такой сложной системой адресации процессор справляется только с помощью программного драйвера, в задачу которого в общем случае входит копирование некоторого блока данных из оперативной памяти в дисковую и обратно. Дисковая память является внешней памятью с прямым доступом, что подразумевает возможность обращения к блокам (но не ячейкам) в произвольном порядке. Память на ленточных носителях имеет последовательный способ доступа. В ней информация хранится в виде блоков фиксированной или переменной длины, в пределах одного носителя эти блоки имеют последовательные адреса. Для доступа к какому-либо блоку устройство должно найти маркер начала ленты (тома), после чего последовательным холостым чтением блока за блоком дойти до требуемого места и только тогда производить сами операции обмена данными.

|

|

|

Особенности сооружения опор в сложных условиях: Сооружение ВЛ в районах с суровыми климатическими и тяжелыми геологическими условиями...

Индивидуальные очистные сооружения: К классу индивидуальных очистных сооружений относят сооружения, пропускная способность которых...

Архитектура электронного правительства: Единая архитектура – это методологический подход при создании системы управления государства, который строится...

История развития пистолетов-пулеметов: Предпосылкой для возникновения пистолетов-пулеметов послужила давняя тенденция тяготения винтовок...

© cyberpedia.su 2017-2024 - Не является автором материалов. Исключительное право сохранено за автором текста.

Если вы не хотите, чтобы данный материал был у нас на сайте, перейдите по ссылке: Нарушение авторских прав. Мы поможем в написании вашей работы!