Триггер- это элементарная ячейка памяти, которая может хранить 2 состояния: либо «0» либо «1». Переход из одного состояния в другое осуществляется скачком. Уровень сигнала на прямом выходе триггера определяется его составляющими в конкретный момент времени.

!!!Построение RS – триггера на ИЛИ-НЕ элементах

Для этого в таблице соответствия неопределенные состояния заменим 0-ми. Составим карту Карно:

Для данного RS – триггера сигнал R=S=1, является запрещенным, а R=S=0 хранение предыдущего состояния триггера. В триггере реализуется прямая логика, т.е. 1-а на R устанавливает RS – триггер в 0-ое состояние.

Синхронные RS – триггеры содержат код синхронизации и сигнал на информационные входы триггера может быть записан только тогда, когда значение входа синхронизации равно 1-е.

Вход синхронизации также позволяет согласовывать работу триггера с

другими элементами схем.

Синхронный двухтактный RS – триггер

Триггер - это элементарная ячейка памяти, которая может хранить 2 состояния: либо «0» либо «1». Переход из одного состояния в другое осуществляется скачком. Уровень сигнала на прямом выходе триггера определяется его составляющими в конкретный момент времени.

Функциональная схема синхронного RS – триггера:

В данной схеме присутствует так называемый вход синхронизации C.

Для двухтактного синхронного RS –триггера управление ведется по заднему фронту входа синхронизации и смена сигнала на входе триггера происходит только в том случае если значение счетного входа равно 1-це, если T=0, то смена состояния триггера на происходит.

Т – триггер

Триггер- это элементарная ячейка памяти, которая может хранить 2 состояния: либо «0» либо «1». Переход из одного состояния в другое осуществляется скачком. Уровень сигнала на прямом выходе триггера определяется его составляющими в конкретный момент времени.

Данный вид триггеров реализует функцию сложения по модулю 2-а, а также на каждые 2-а входных сигнала на счетном входе «T» получаем один выходной сигнал.

Схема асинхронного, двухтактного T – триггера:

Предположим, что предыдущее состояние триггера было нулевое, соответственно ан прямом выходе Q=0, а на инверсном  . В этом случае единичный уровень сигнала поступает на вход «S», нулевой на «R», если при этом T=1, то происходит запись 1-цы в первую ступень триггера (т.е. 1,2,3,4).

. В этом случае единичный уровень сигнала поступает на вход «S», нулевой на «R», если при этом T=1, то происходит запись 1-цы в первую ступень триггера (т.е. 1,2,3,4).

При перемене сигнала на счетном входе «T», т.е. T=0, происходит смена сигнала на выходе второй ступени (т.е. 5,6,7,8), и на прямом выходе T –триггера появляется 1-а.

Управление ведется по заднему фронту.

Д- триггер

Триггер- это элементарная ячейка памяти, которая может хранить 2 состояния: либо «0» либо «1». Переход из одного состояния в другое осуществляется скачком. Уровень сигнала на прямом выходе триггера определяется его составляющими в конкретный момент времени.

!!!D – триггер (триггер с задержкой по времени)

Асинхронные D –триггеры являются повторительными, поэтому для практической реализации функции с задержкой времени используются однотактные и двухтактные D –триггеры.

Управление ведется по переднему фронту единичного сигнала входа синхронизации. Максимальная задержка сигнала однотактного D – триггера на выходе  сигнала на входе.

сигнала на входе.

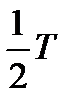

Двухтактный синхронный D – триггер отличается от однотактного тем, что задержка по времени на Т.

JK – триггер

Триггер- это элементарная ячейка памяти, которая может хранить 2 состояния: либо «0» либо «1». Переход из одного состояния в другое осуществляется скачком. Уровень сигнала на прямом выходе триггера определяется его составляющими в конкретный момент времени.

Может реализовывать все функции предыдущих триггеров.

Главное отличие JK – триггера: не имеет запрещенных состояний.

1 – хранение 0-я;

2 – подтверждение 0-я;

3 – установка 1-цы;

4 – переход в противоположное состояние;

5 – хранение 1-цы;

6 – переход в 0-ое состояние;

7 – подтверждение 1-цы;

8 – переход в противоположное состояние;

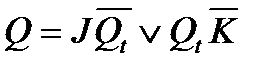

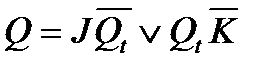

Карта Карно для JK – триггера:

Сигнал на выходе триггера в последующий момент времени изменяется на противоположный, если J=1, или равен предыдущему если K=0, если J=K=1, то триггер работает в режиме счетного триггера, если размыкается обратная связь, то триггер работает в режиме синхронного RS – триггера, если на J и K одновременно подавать противоположные сигналы, то триггер работает в режиме D – триггера.

Незадействованные входы элементов & являются свободными для наращивания схемы.

11)Регистры последовательный и параллельный

Регистр – этот узел ЭВМ предназначенный для хранения кода слова, и выполнения над хранимым словом ряда операций.

Регистры строятся на триггерах.

Количество разрядов регистров равно количеству триггеров, входящих в его состав.

ü Параллельный регистр – предназначен для хранения кода слова, и передача слова в другой регистр;

ü Последовательный регистр – предназначен для последовательного сдвига слова влево или вправо;

Трехразрядный параллельный регистр на базе однотактных D – триггеров.

Q=x0*V

Q1=x1*V

Q2=x2*V

Информационный вход V- запись кода слова

Установка «0»- подача «1» на данный вход обнуляет все разряды.

Данный регистр носит название однофазного регистра, т.к. запись слова происходит по одному информационному входу «V».

Время срабатывания данного регистра определяется как сумма времени срабатывания триггера и времени срабатывания элемента «И».

Т

р=Т

тр+Т

&

Ттр – время срабатывания триггера

Т& – время срабатывания элемента &

Для увеличения быстродействия регистров, используются регистры с парафазным входом, где каждому разряду соотв. 2 информационных входа, которые являются взаимно инверсными, что приводит к однозначности при установке всех разрядов регистра.

Трехразрядный последовательный сдвигающий регистр построенный на синхронных D – триггерах

R – установка триггеров в 0-ое состояние

ОС – обратная связь.

С – номер такта, Q0,Q1,Q2 – входы регистра.

При каждом тактовом импульсе происходит сдвиг кода слова вправо.

Для сохранения информации в регистре при ее передачи в другой регистр вводится обратная связь, и вместе с записью информации в следующий регистр происходит восстановление информации в исходный регистр.

Сдвигающие регистры могут быть реверсивными, т.е. осуществлять сдвиг информации как влево так и вправо в зависимости от сигнала в цепи управления.

. В этом случае единичный уровень сигнала поступает на вход «S», нулевой на «R», если при этом T=1, то происходит запись 1-цы в первую ступень триггера (т.е. 1,2,3,4).

. В этом случае единичный уровень сигнала поступает на вход «S», нулевой на «R», если при этом T=1, то происходит запись 1-цы в первую ступень триггера (т.е. 1,2,3,4).

сигнала на входе.

сигнала на входе.