Лабораторная работа №1

Тема: Знакомство с программой WorkBench и исследование логических элементов.

Цель: Научится работать с программой WorkBench и исследовать логических элементов.

Задание 1. Ознакомиться с основными компонентами программы

Для операций с компонентами на общем поле Electronics Workbench выделены две области: панель компонентов и поле компонентов (рис. 1. 1).

Рисунок 1.1 Окно программы Electronics Workbench

Панель компонентов состоит из пиктограмм полей компонентов, поле компонентов -из условных изображений компонентов. Щелчком мышью на одной из одиннадцати пиктограмм полей компонентов, расположенных на панели, можно открыть соответствующее поле. На рис. 1. 1 открыто поле компонентов источников (Sources). Расположение элементов в полях ориентировано на частоту использования компонента. Для описания компонентов более логичным является разделение их по типам, чему мы будем следовать в дальнейшем, давая в каждом случае ссылку на поле, в котором расположен компонент. При работе может быть открыто только одно поле компонентов. Перейдем теперь к описанию имеющихся в программе компонентов. В библиотеки элементов программы Electronics Workbench входят аналоговые, цифровые и цифро-аналоговые компоненты. Все компоненты можно условно разбить на следующие группы: • базовые компоненты, • источники, • линейные компоненты, • ключи, • нелинейные компоненты, • индикаторы, • логические компоненты, • узлы комбинационного типа, • узлы последовательного типа, • гибридные компоненты.

Источники (Sources):

заземление

заземление

Компонент «заземление» имеет нулевое напряжение и таким образом обеспечивает исходную точку для отсчета потенциалов. Не все схемы нуждаются в заземлении для моделирования. Однако, любая схема, содержащая: • операционный усилитель, • трансформатор, • управляемый источник, • осциллограф, должна быть обязательно заземлена, иначе приборы не будут производить измерения или их показания окажутся неправильными.

генератор тактовых импульсов

генератор тактовых импульсов

Генератор вырабатывает последовательность прямоугольных импульсов. Можно регулировать амплитуду импульсов, коэффициент заполнения (скважность) и частоту следования импульсов. Отсчет амплитуды импульсов генератора производится от вывода, противоположного выводу "+".

Базовые компоненты (Basic):

соединяющий узел

соединяющий узел

Узел применяется для соединения проводников и создания контрольных точек. К каждому узлу может подсоединяться не более четырех проводников. После того, как схема собрана, можно вставить дополнительные узлы для подключения приборов.

источник сигнала «логическая единица»

источник сигнала «логическая единица»

При помощи этого источника устанавливают уровень логической единицы в узле схемы.

ключ, управляемый клавишей (клавиша задаѐтся в Key) Индикаторы (Indicators):

ключ, управляемый клавишей (клавиша задаѐтся в Key) Индикаторы (Indicators):

пробник логического уровня

пробник логического уровня

Пробник определяет логический уровень (0 или 1) в конкретной точке схемы. Если исследуемая точка имеет уровень логической 1, индикатор загорается красным цветом. Уровень логического нуля свечением не отмечается. На вкладке Choose Prob в меню Component Properties можно изменить цвет свечения пробника.

Логические элементы (Logic Gates):

логическое НЕ

логическое НЕ

Элемент логическое НЕ или инвертор изменяет состояние входного сигнала на противоположное. Уровень логической 1 появляется на его выходе, когда на входе не 1, и наоборот. Таблица истинности:

логическое И

логическое И

Элемент И реализует функцию логического умножения. Уровень логической 1 на его выходе появляется в случае, когда на один и на другой вход подается уровень логической единицы. Таблица истинности:

логическое ИЛИ

логическое ИЛИ

Элемент ИЛИ реализует функцию логического сложения. Уровень логической 1 на его выходе появляется в случае, когда на один или на другой вход подается уровень логической единицы. Таблица истинности

исключающее ИЛИ

исключающее ИЛИ

Двоичное число на выходе элемента исключающее ИЛИ является младшим разрядом суммы двоичных чисел на его входах. Таблица истинности:

элемент И-НЕ

элемент И-НЕ

Элемент И-НЕ реализует функцию логического умножения с последующей инверсией результата. Он представляется моделью из последовательно включенных элементов И и НЕ. Таблица истинности элемента получается из таблицы истинности элемента И путем инверсии результата. Эквивалентная модель элемента: Таблица истинности:

элемент ИЛИ-НЕ

элемент ИЛИ-НЕ

Элемент ИЛИ-НЕ реализует функцию логического сложения с последующей инверсией результата. Он представляется моделью из последовательно включенных элементов ИЛИ и НЕ. Его таблица истинности получается из таблицы истинности элемента ИЛИ путем инверсии результата. Таблица истинности:

исключающее ИЛИ-НЕ

исключающее ИЛИ-НЕ

Данный элемент реализует функцию "исключающее ИЛИ" с последующей инверсией результата. Он представляется моделью из двух последовательно соединенных элементов: исключающее ИЛИ и НЕ. Таблица истинности:

Инструменты (Instruments):

логический преобразователь

логический преобразователь

Служит для исследования логических схем, можно производить анализ логических схем: строить таблицы истинности и получать логические выражения. С его помощью можно также производить синтез логических схем, т.е. по таблице истинности получить логическое выражения, а затем схему.

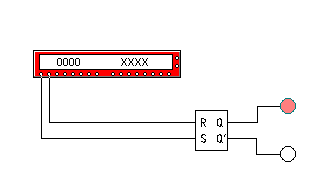

Задание: составить схему (рис. 1.2). В последующих схемах заменить элементы и проверить таблицы истинности.

Рис. 1.2. Схема подключения элемента

Задание 2. Исследование логического элемента Исключающего ИЛИ с помощью аналитического анализатора.

1. Собрать схему, состоящую из логического элемента Исключающее ИЛИ и аналитического преобразователя, как показано на рисунке

Рисунок 2.1 Вид рабочего поля

2. Двойным щелчком по схеме анализатора открыть диалоговое окно

3. Сгенерировать таблицу истинности, щелкнув по кнопке

4. Получить булево выражение, щелкнув по кнопке  Это выражение приводится на дополнительном дисплее,

Это выражение приводится на дополнительном дисплее,

расположенном в нижней части лицевой панели, в виде двух слагаемых, соответствующих выходному сигналу ИСТИНА (сигнал логической единицы на выходе OUT). Сопоставление полученного выражения с таблицей истинности убеждает нас в том, что таких комбинаций действительно две, если учесть, что в полученном выражении приняты следующие обозначения: А'=0 — инверсия А=1, B'=0 — инверсия В=1, знак + соответствует логической операции ИЛИ.

Задание 3. Выполнить анализ следующих логических элементов: И, ИЛИ, ИЛИ-НЕ, И-НЕ, Исключающее ИЛИ-НЕ

Лабораторная работа №2

Задание 1. Синтез логических схем

С помощью логического преобразователя можно проводить не только анализ логических устройств, но и их синтез. Допустим, что нам требуется составить схему и булево выражение для логического элемента, у которого выходная комбинация в таблице истинности не такая, как на рис. 2.1, а 1101. Для внесения необходимых изменений отмечаем курсором в столбце OUT подлежащий изменению символ, изменяем его с помощью клавиатуры и затем, перемещаясь по столбцу клавишами управления курсором, изменяем по необходимости символы в других строках. После внесения всех изменений последовательно нажимаем на клавиши  ,

,  ,

,

Синтезированное логическое устройство показано в верхнем левом углу рис. 3,1, а его булево выражение — на дополнительном дисплее.

В более общем случае для выполнения синтеза целесообразно действовать следующим образом. Щелчком курсора по иконке логического преобразователя непосредственно на линейке приборов раскрываем его лицевую панель. Активизируем курсором клеммы-кнопки А, В...Н (начиная с А), количество которых равно количеству входов синтезируемого устройства. Вносим необходимые изменения в столбец OUT и после нажатия на панели преобразователя указанных выше клавиш управления получаем результат в виде схемы на рабочем поле программы и булево выражение в дополнительном дисплее.

Рис. 3.1. Рабочее поле после синтеза схемы

В заключение заметим, что для двухвходовых элементов можно увеличить количество входов до восьми, открывая двойным щелчком по значку компонента диалоговое окно (рис. 3.2). По умолчанию в этом окне указано минимально возможное число входов, равное двум.

| Вход А

| Вход В

| Вход C

| Вход D

| Выход Y

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

| |

|

|

|

|

|

|

Рис. 3.2 Диалоговое окно для изменения количества входов Задание 2. Выполнить синтез схемы, имеющей таблицу истинности:

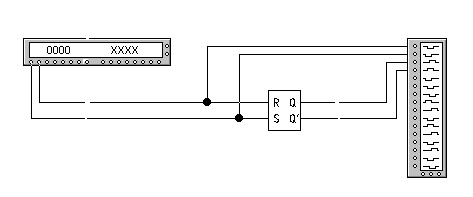

Лабораторная работа №3

Задание №1. Исследование шифратора

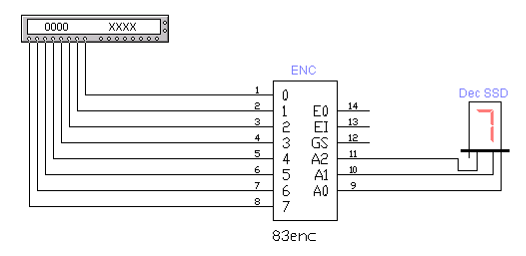

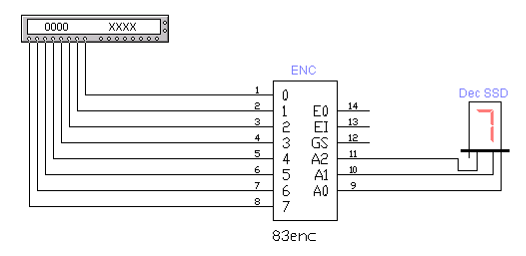

1) Соберите схему, показанную на рисунке 4.1

Рис. 4.1. Схема включения шифратора В ней используются следующие элементы:

Рис. 4.1. Схема включения шифратора В ней используются следующие элементы:

шифратор (ENC) Generic 8-to-3 Enc; генератор слов

дешифрующий семисегментный индикатор (Dec SSD)

При моделировании необходимо обратить внимание на реализацию принципа приоритета, при этом следует учесть, что все входы и выходы — инверсные (в программе EWB они ошибочно показаны прямыми).

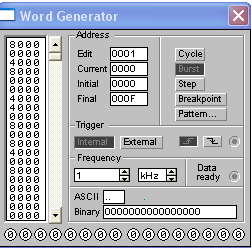

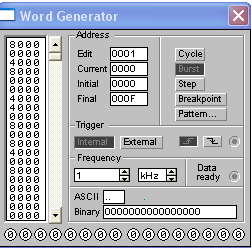

2) Сделайте двойной щелчок по генератору слов и занесите соответствующие коды в поле Binary в адреса с 0000 по 0007. Запустите модель в пошаговом режиме (кнопка Step). Генератор слов показан на рис.

4.2. Занесите полученные на табло результаты в таблицу истинности

Таблица истинности

Рис. 4.2. Вид генератора слов.

| Входы

| Выходы

|

|

|

|

|

|

|

|

|

| Табло

| A2

| A1

| A0

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Задание №2. Исследование дешифратора

1) Соберите схему, показанную на рисунке 4.3

Рис. 4.3. Схема включение дешифратора В ней используются следующие элементы:

Рис. 4.3. Схема включение дешифратора В ней используются следующие элементы:

дешифратор (DEC) Generic 3-to-8 Dec; 8 пробников логического уровня;

источник сигнала «логическая единица»; заземление;

6 соединяющих узлов;

4 ключа, управляемые клавишей (кнопка Switch на панели Basic).

Ключи могут быть замкнуты или разомкнуты при помощи управляющих клавиш на клавиатуре. Имя управляющей клавиши можно ввести с клавиатуры в диалоговом окне, появляющемся после двойного щелчка мышью на изображении ключа.

2) Занесите полученные результаты моделирования в таблицу истинности. Выясните, для чего нужен вход G1.

Лабораторная работа №4

Задание №1. Получение таблиц истинности триггеров

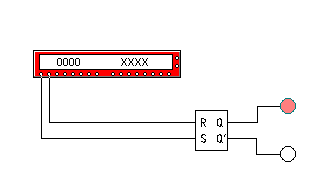

1) Создайте схему, показанную на рисунке 8.1.

Рис. 8.1. Схема для исследования RS-триггера

В схеме к входам триггера подключен генератор слова и светодиодные индикаторы к выходам.

2) Получить таблицу истинности триггера, подавая на входы различные комбинации (минимум их 6). Двойным щелчком по генератору слов открыть диалоговое окно и занести необходимые слова. Установите адрес начала (Initial) в 0000 и адрес конца (Final) в 0005(для 6 вариантов) Работать с генератором слов нужно в пошаговом режиме (кнопка STEP). Результаты занести в таблицу:

| № п/п

| Входы

| Выходы

|

| R

| S

| Q

| Q’

|

|

|

|

|

|

|

Задание №2. Построение диаграмм

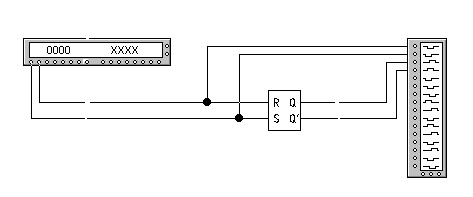

1) Собрать схему, показанную на рисунке 8.2.

Рис. 8.2. Схема включения RS-триггера

В схеме используется генератор слов (Word Generator) и логический анализатор (Logig Analyzer)

2) Двойным щелчком по генератору слов откройте диалоговое окно и задайте 16 слов, как показано на рис. 8.3. Установите адрес начала (Initial) в 0000, а адрес конца (Final) в 000F. Щелкните по кнопке Burst, что подаст на входы триггера последовательно все 16 слов.

Рис. 8.3. Диалоговое окно генератора слов

3) Откройте двойным щелчком логический анализатор. Убедитесь в правильности получения результатов.

Задание №3 Исследование счѐтчиков

Счетчик - устройство для подсчета числа входных импульсов. Число, представляемое состоянием его выходов по фронту каждого входного импульса, изменяется на единицу. Счетчик можно реализовать на нескольких триггерах. В суммирующих счетчиках каждый входной импульс увеличивает число на его выходе на единицу, в вычитающих счетчиках каждый входной импульс уменьшает это число на единицу.

1) Собрать схему, показанную на рисунке 9.1.

Рис. 9.1. Схема трѐхразрядного суммирующего счѐтчика

2) Дважды щѐлкните по источнику импульсов и установите частоту 1 Гц, закройте диалоговое окно.

3) Понаблюдайте за изменением индикатора.

4) Выключите схему и отредактируйте еѐ, чтобы получить вычитающий счѐтчик.

Вычитающий счѐтчик можно получить двумя способами:

а) Считывать выходные сигналы счетчика не с прямых, а с инверсных выходов триггеров;

б) Изменить структуру связей в счетчике: подавать на счетный вход следующего триггера сигнал не с инверсного, а с прямого выхода предыдущего.

5) Подсоедините вместо семисегментного индикатора логический анализатор, как показано на рисунке 9.2.

6) Дважды щѐлкните по источнику импульсов и установите частоту 2

КГц.

7) Двойным щелчком по анализатору откройте диаграммы и запустите

схему. Через несколько секунд остановите работу схемы.

8) Зарисуйте и проанализируйте диаграммы суммирующего и вычитающего счѐтчиков.

Рис. 9.2. Схема счетчика для анализа диаграмм

Задание №2. Изучение работы делителя частоты

Счетчик должен иметь 5 состояний, которые в простейшем случае образуют последовательность: {О, 1, 2, 3, 4}. Циклическое повторение этой последовательности означает, что коэффициент деления счетчика равен 5.

Схема такого счѐтчика изображена на рисунке 9.3

Рис. 9.3. Схема счѐтчика с коэффициентом деления 5

1) Нарисуйте схему рисунка 8.3.

2) Сделайте двойной щелчок на источнике импульсов и установите частоту 1 Гц.

3) Включите схему и понаблюдайте за индикатором.

Лабораторная работа №5

Тема: Исследование ОЗУ.

Задание №1. Исследование оперативного запоминающего устройства

1) Нарисовать схему, показанную на рисунке 12.1.

Рис. 12.1. Схема ячейки памяти

При записи в ячейку памяти (см. рис. 12.1) на соответствующей разрядной шине устанавливается 1 или 0, на входе WR/RD' устанавливается сигнал 1 и после стробирования счетчика или дешифраторов адреса сигналом CS (на адресных входах X и Y сигнал 1) срабатывают элементы U1, U2. Положительный перепад сигнала с элемента U2 поступает на тактовый вход D-триггера U4, в результате чего в нем записывается 1 или 0 в зависимости от уровня сигнала на его D-входе.

При чтении из ячейки памяти на входе WR/RD устанавливается 0, при этом срабатывают элементы U1, U3, U5 и на вход РАЗРЕШЕНИЕ ВЫХОДА буферного элемента U6 поступает разрешающий сигнал, в результате чего сигнал с Q-выхода D-триггера передается на разрядную шину DO. Для проверки функционирования ячейки памяти используется генератор слова (рис. 12.2).

2) Занести в генератор слова комбинации из таблицы 12.1.

3) Заполнить таблицу 12.1 и определить: какая операция выполняется при каждой комбинации – чтение 1 (0) или запись 1 (0)?

Таблица 12.1 Результат эксперимента

Лабораторная работа №1

Тема: Знакомство с программой WorkBench и исследование логических элементов.

заземление

заземление генератор тактовых импульсов

генератор тактовых импульсов соединяющий узел

соединяющий узел источник сигнала «логическая единица»

источник сигнала «логическая единица» ключ, управляемый клавишей (клавиша задаѐтся в Key) Индикаторы (Indicators):

ключ, управляемый клавишей (клавиша задаѐтся в Key) Индикаторы (Indicators): пробник логического уровня

пробник логического уровня логическое НЕ

логическое НЕ логическое И

логическое И логическое ИЛИ

логическое ИЛИ исключающее ИЛИ

исключающее ИЛИ элемент И-НЕ

элемент И-НЕ элемент ИЛИ-НЕ

элемент ИЛИ-НЕ исключающее ИЛИ-НЕ

исключающее ИЛИ-НЕ логический преобразователь

логический преобразователь

Это выражение приводится на дополнительном дисплее,

Это выражение приводится на дополнительном дисплее, ,

,  ,

,

Рис. 4.1. Схема включения шифратора В ней используются следующие элементы:

Рис. 4.1. Схема включения шифратора В ней используются следующие элементы:

Рис. 4.3. Схема включение дешифратора В ней используются следующие элементы:

Рис. 4.3. Схема включение дешифратора В ней используются следующие элементы: