КЛАССИФИКАЦИЯ

Степень интеграции

В зависимости от степени интеграции применяются следующие названия интегральных схем:

· малая интегральная схема (МИС) — до 100 элементов в кристалле,

· средняя интегральная схема (СИС) — до 1000 элементов в кристалле,

· большая интегральная схема (БИС) — до 10 тыс. элементов в кристалле,

· сверхбольшая интегральная схема (СБИС) — более 10 тыс. элементов в кристалле.

Ранее использовались также теперь уже устаревшие названия: ультрабольшая интегральная схема (УБИС) — от 1-10 млн. до 1 млрд. элементов в кристалле[9][10] и, иногда, гигабольшая интегральная схема (ГБИС) — более 1 млрд. элементов в кристалле. В настоящее время, в 2010-х, названия «УБИС» и «ГБИС» практически не используются, и все микросхемы с числом элементов более 10 тыс. относят к классу СБИС.

Технология изготовления

Гибридная микросборка STK403-090, извлечённая из корпуса

· Полупроводниковая микросхема — все элементы и межэлементные соединения выполнены на одном полупроводниковом кристалле (например, кремния, германия, арсенида галлия, оксида гафния).

· Плёночная интегральная микросхема — все элементы и межэлементные соединения выполнены в виде плёнок:

· толстоплёночная интегральная схема;

· тонкоплёночная интегральная схема.

· Гибридная микросхема (часто называемая микросборкой), содержит несколько бескорпусных диодов, бескорпусных транзисторов и(или) других электронных активных компонентов. Также микросборка может включать в себя бескорпусные интегральные микросхемы. Пассивные компоненты микросборки (резисторы, конденсаторы, катушки индуктивности) обычно изготавливаются методами тонкоплёночной или толстоплёночной технологий на общей, обычно керамической подложке гибридной микросхемы. Вся подложка с компонентами помещается в единый герметизированный корпус.

· Смешанная микросхема — кроме полупроводникового кристалла содержит тонкоплёночные (толстоплёночные) пассивные элементы, размещённые на поверхности кристалла.

Вид обрабатываемого сигнала

· Аналоговые.

· Цифровые.

· Аналого-цифровые.

Аналоговые микросхемы — входные и выходные сигналы изменяются по закону непрерывной функции в диапазоне от положительного до отрицательного напряжения питания.

Цифровые микросхемы — входные и выходные сигналы могут иметь два значения: логический ноль или логическая единица, каждому из которых соответствует определённый диапазон напряжения. Например, для микросхем типа ТТЛ при напряжении питания +5 В диапазон напряжения 0…0,4 В соответствует логическому нулю, а диапазон от 2,4 до 5 В — логической единице; для микросхем ЭСЛ-логики при напряжении питания −5,2 В диапазон от −0,8 до −1,03 В — логической единице, а от −1,6 до −1,75 В — логическому нулю.

Аналого-цифровые микросхемы совмещают в себе формы цифровой и аналоговой обработки сигналов, например, усилитель сигнала и аналого-цифровой преобразователь.

Интегральные микросхемы характеризуются следующими основными параметрами:

· Напряжением питания Un.

· Мощностью потребления энергии элементом от источника питания Рп (в заданном режиме).

· Помехоустойчивостью ип0м, наибольшее напряжение помехи на входе ИС, которое не вызывает.нарушения правильности работы элемента.

Классификация счетчиков

Цифровые счетчики классифицируются следующим образом:

– по коэффициенту (модулю счета):

· двоичные (бинарные);

· двоично-десятичные (декадные);

· с другим основанием счета;

· с произвольным постоянным модулем;

· с переменным модулем;

– по направлению счета:

· суммирующие;

· вычитающие;

· реверсивные;

– по способу организации внутренних связей:

· с последовательным переносом;

· с комбинированным переносом;

· с параллельным переносом;

· кольцевые.

Классификационные признаки независимы и могут встречаться в разных сочетаниях: суммирующие счетчики бывают как с последовательным, так и с параллельным переносом, и могут иметь двоичный, десятичный или иной коэффициент счета.

Для двоичного счетчика, зная номера триггеров и состояния выходов Q, можно определить записанное в счетчик двоичное число М= Qm ´2(m -1)+ Qm –1´2(m -2)+...+ Q 1´20, где m – номер триггера; 20 – вес первого (младшего разряда); 21 – второго,...; 2(m -1) – вес m -го разряда.

Введением дополнительных логических связей – обратных и прямых – двоичные счетчики могут быть обращены в недвоичные. Наибольшее распространение получили десятичные (декадные) счетчики, работающие с привычным Ксч=10. Десятичный счет осуществляется в двоично-десятичном коде (двоичный – по коду счета, десятичный – по числу состояний).

Десятичные счетчики организуются из четырех разрядных двоичных счетчиков. Избыточные шесть состояний исключаются введением дополнительных связей.

Универсальные регистры

В сериях ИС и библиотеках БИС/СБИС программируемой логики имеется много вариантов регистров. Среди них есть многорежимные (многофункциональные) или универсальные, способные выполнять набор микроопераций. Так, например, универсальный регистр может обеспечивать параллельный прием и выдачу данных, сдвиг параллельно записанного слова влево или вправо, поразрядный ввод слова, как это осуществляется в регистрах сдвига, и выдачу этого слова на выход в параллельном коде, сброс всей записанной информации. Многорежимность достигается композицией в одной и той же схеме частей, необходимых для выполнения различных операций. Управляющие сигналы, задающие вид выполняемой операции, активизируют необходимые для этого части схемы. На рис. 3.37 показано условное обозначение типового универсального регистра. Входы D служат для параллельной записи восьмиразрядного слова данных, а выходы Q – для его выдачи. Возможна последовательная поразрядная загрузка слова со сдвигом всех разрядов влево или вправо. Через вход DSR осуществляется поразрядная загрузка слова через нулевой разряд со сдвигом всего записываемого слова в сторону старших разрядов. Вход DSL обеспечивает загрузку слова через седьмой разряд со сдвигом в сторону младших разрядов. Входы S0 и S, – управляющие. Вход S0 разрешает сдвиг влево, а вход S1 – вправо. Вход R обеспечивает асинхронный сброс всех разрядов регистра, т.е. его "обнуление", вход С – синхронизирующий. Выводы U cc и GND служат для подключения к микросхеме напряжения питания.

Рис. 3.37. Универсальный регистр

Суммирующие счётчики

Простейшим счётчиком является Т-триггер, считающий до 2-х, то есть осуществляющий счёт и хранение не более 2-х сигналов.

Счётчик, образованный цепочкой из n триггеров сможет подсчитать в двоичном коде 2n импульсов. Число n определяет количество разрядов двоичного числа, которое может быть записано в счётчик. Число 2n называется модулем или коэффициентом счёта:

KСЧ = 2n

Схема простейшего 4-х разрядного счётчика приведена на рисунке 60,а. Принцип работы счётчика проиллюстрирован временными диаграммами, приведёнными на рисунке 60,б.

Рисунок 60 Схема двоичного суммирующего счётчика а)

и временные диаграммы его работы б).

Первый разряд счётчика переключается с приходом каждого входного импульса, что соответствует алгоритму работы Т-триггера. На каждые два входных импульса Т-триггер формирует один выходной импульс.

Второй разряд переключается в состояние «1» после прихода каждого 2-го импульса.

Третий разряд — после прихода каждого 4-го импульса.

Четвёртый разряд — после прихода каждого 8-го импульса.

Таким образом, единичные значения сигналов на выходах триггеров регистра появляются с приходом 1, 2, 4, 8 импульсов, что соответствует весовым коэффициентам двоичного кода. Поэтому с выходов триггеров регистра можно прочитать параллельный двоичный код числа импульсов, поступивших на его вход. Например, после прихода 5 импульсов единичные значения установятся на выходах Q1 и Q3(см. пунктирную линию на рисунке 60,б), что соответствует коду числа 5: 0101B. Аналогично, после прихода 13-и импульсов на выходах триггеров установится код 1101B.

Если число входных импульсов NВХ > KСЧ, то при NВХ=KСЧ происходит переполнение счётчика, после чего счётчик возвращается в нулевое состояние и повторяет цикл работы.

После каждого цикла счёта на выходе последнего триггера возникают перепады напряжения, то есть формируется один импульс. Это свойство определяет второе назначение счётчиков — деление числа входных импульсов.

Если входные сигналы периодичны и следуют с частотой fВХ, то частота fВЫХ:

fВЫХ = fВХ / KСЧ

В этом случае коэффициент счёта определяется как коэффициент деления и обозначается KДЕЛ.

У счётчика в режиме деления частоты используется сигнал только последнего триггера, а промежуточные состояния остальных триггеров не учитываются.

Всякий счётчик может быть использован как делитель частоты.

Структура 2D

В структуре 2D (см. рисунок на следующей странице) запоминающие элементы ЗЭ организованы в прямоугольную матрицу размерностью М = k x m, где М – информационная емкость памяти в битах; k – число хранимых слов; m – их разрядность.

Дешифратор адресного кода DC при наличии разрешающего сигнала CS (Chip Select) активизирует одну из выходных линий, разрешая одновременный доступ ко всем элементам выбранной строки, хранящей слово, адрес которого соответствует номеру строки. Элементы столбца соединены вертикальной линией – внутренней линией данных (разрядной линией, линией записи/считывания). Элементы столбца хранят одноименные биты всех слов. Направление обмена определяется усилителями чтения/записи под воздействием сигнала R/W (Read – чтение, Write – запись).

Структура типа 2D применяется лишь в ЗУ малой информационной емкости, т.к. при росте емкости проявляется несколько ее недостатков, наиболее очевидным из которых является чрезмерное усложнение дешифратора адреса (число выходов дешифратора равно числу хранимых слов).

Структура 3D

Структура 3D позволяет резко упростить дешифраторы адреса с помощью двухкоординатной выборки запоминающих элементов. Принцип двухкоординатной выборки поясняется на примере ЗУ типа ROM (см. рисунок на следующей странице), реализующего только операции чтения данных.

Здесь код адреса разрядностью n делится на две половины, каждая из которых декодируется отдельно. Выбирается запоминающий элемент, находящийся на пересечении активных линий выходов обоих дешифраторов. Таких пересечений будет как раз

2N/2 X 2n/2 = 2n

Суммарное число выходов обоих дешифраторов составляет

2n/2 + 2n/2 = 2n/2+1,

что гораздо меньше, чем 2n при реальных значениях n.

Уже для ЗУ небольшой емкости видна эта существенная разница: для структуры 2D при хранении 1К слов потребовался бы дешифратор с 1024 выходами, тогда как для структуры типа 3D нужны два дешифратора с 32 выходами каждый. Недостатком структуры 3D в первую очередь является усложнение элементов памяти, имеющих двухкоординатную выборку.

Структуры типа 3D имеют также довольно ограниченное применение, поскольку в структурах типа 2DM сочетаются достоинства обеих рассмотренных структур – упрощается дешифрация адреса и не требуются запоминающие элементы с двухкоординатной выборкой.

Структура 2DM

ЗУ структуры 2DM (2D модифицированная) (см. следующий рисунок) для матрицы запоминающих элементов с адресацией от дешифратора DCx имеет как бы характер структуры 2D: возбужденный выход дешифратора выбирает целую строку. Однако в отличие от структуры 2D, длина строки не равна разрядности хранимых слов, а многократно ее превышает. При этом число строк матрицы уменьшается и, соответственно, уменьшается число выходов дешифратора. Для выбора одной из строк служат не все разряды адресного кода, а их часть An-1...Ak. Остальные разряды адреса (от Аk-1 до А0) используются, чтобы выбрать необходимое слово из того множества слов, которое содержится в строке. Это выполняется с помощью мультиплексоров, на адресные входы которых подаются коды Аk-1...А0. Длина строки равна m2k, где m - разрядность хранимых слов. Из каждого "отрезка" строки длиной 2k мультиплексор выбирает один бит. На выходах мультиплексоров формируется выходное слово По разрешению сигнала CS, поступающего на входы ОЕ управляемых буферов с тремя состояниями, выходное слово передается на внешнюю шину.

На предыдущем рисунке для большей наглядности структура 2DM показана на примере ROM. На следующем рисунке структура 2DM в более общем виде показана для ЗУ типа RAM с операциями чтения и записи. Из матрицы М по-прежнему счи-тывается "длинная" строка.

Данные в нужный отрезок этой строки записываются (или считываются из нее) управляемыми буферами данных BD, воспринимающими выходные сигналы второго дешифратора DCY, и выполняющими не только функции мультиплексирования, но и функции изменения направления передачи данных под воздействием сигнала R/W.

10. Методика синтеза и параметры компараторов.

Синтез компаратора

Компаратор – это цифровое устройство, предназначенное для сравнения двух цифровых сигналов. Исходя из трех комбинаций (А=Б, А>Б, А<Б) на выходе получаем три сигнала.

таблица истинности для компаратора:

| X1

| X0

| Z1

| Z2

| =

| >

| <

|

| 0 0 0 0

| 0 0 0 0

| 0 0 1 1

| 0 1 0 1

| 1

| | 1 1 1

|

| 0 0 0 0

| 1 1 1 1

| 0 0 1 1

| 0 1 0 1

| 1

| 1

| 1 1

|

| 1 1 1 1

| 0 0 0 0

| 0 0 1 1

| 0 1 0 1

| 1

| 1 1

| 1

|

| 1 1 1 1

| 1 1 1 1

| 0 0 1 1

| 0 1 0 1

| 1

| 1 1 1

| |

Карта Карно для равенства (=)

| x1x0 z1z0

| 00

| 01

| 11

| 10

|

| 00

| 1

| | | |

| 01

| | 1

| | |

| 11

| | | 1

| |

| 10

| | | | 1

|

=

=

=  ;

;

Для (X>Z)

| x1x0 z1z0

| 00

| 01

| 11

| 10

|

| 00

| | 1

| 1

| 1

|

| 01

| | | 1

| 1

|

| 11

| | | | |

| 10

| | | 1

| |

=

=

=  ;

;

Для (X<Z)

| x1x0 z1z0

| 00

| 01

| 11

| 10

|

| 00

| | | | |

| 01

| 1

| | | |

| 11

| 1

| 1

| | 1

|

| 10

| 1

| 1

| | |

,

,  ,

,

Найдя вход Q2 мы его инвертируем, т.к.  вместо 4 элементов «И-НЕ» применяем один инвертор. Соблюдается схема только тогда, когда

вместо 4 элементов «И-НЕ» применяем один инвертор. Соблюдается схема только тогда, когда  .

.

Параметры, характеризующие качество компараторов, можно разделить на три группы: точностные, динамические и эксплуатационные.

Компаратор характеризуется теми же точностными параметрами, что и ОУ.

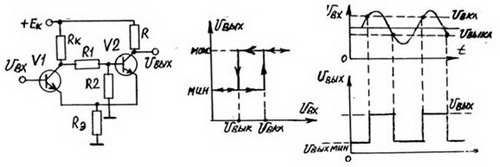

Основным динамическим параметром компаратора является время переключения tп. Это промежуток времени от начала сравнения до момента, когда выходное напряжение компаратора достигает противоположного логического уровня. Время переключения замеряется при постоянном опорном напряжении, подаваемом на один из входов компаратора и скачке входного напряжения Uвх, подаваемого на другой вход. Это время зависит от величины превышения Uвх над опорным напряжением. На рис. 8 приведены переходные характеристики компаратора mА710 для различных значений дифференциального входного напряжения Uд при общем скачке входного напряжения в 100мВ. Время переключения компаратора tп можно разбить на две составляющие: время задержки tз и время нарастания до порога срабатывания логической схемы tн. В справочниках обычно приводится время переключения для значения дифференциального напряжения, равного 5мВ после скачка.

Рис. 108. Переходная характеристика компаратора мА710 при различных превышениях скачка входного напряжения Uд над опорным: 1 – на 2 мВ; 2 – на 5 мВ; 3 – на 10 мВ; 4 – на 20 мВ

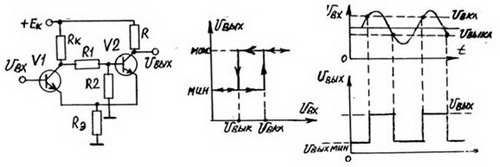

Рассмотренные компараторы с двухпороговым уровнем принято называть компараторами с гистерезисом или триггерами Шмитта(ТШ). Существуют многочисленные схемные модификации ТШ. В простейшем эмиттерно-связанном ТШ на n-p-n БПТ(рис.) достигается два порога срабатывания Uвкл и Uвыкл. Схема передаточная, характеристика и форма входного и выходного напряжений представлены на рис. 3.6 а, б, в.

а) б) в)

Рис. 3.6. Схема,передаточная характеристика

и графики работы ТШ

Помимо генератора прямоугольных импульсов, ТШ применяют в качестве АО и пороговых детекторов.

Триггерные спусковые схемы используются в качестве основных узлов импульсных релаксационных генераторов (одновибраторов, мультивибраторов (МВ), генераторов линейно-изменяющегося напряжения (ГЛИН), блокинг-генераторов (БГ) и т. д.), подробно рассмотренных в специальной литературе по импульсной технике.

Мультиплексоры

Мультиплексор служит для объединения в единый транспортный поток цифровых потоков от различных источников – кодеров сжатия, выходов других мультиплексоров, выходов приемников – декодеров и т.д. Приходящие сигналы могут иметь разную временнýю базу (то есть формироваться с несколько различающимися тактовыми частотами), и задача мультиплексора – сформировать асинхронный поток с сохранением синхронизирующей информации каждого из компонентов.

Принцип действия мультиплексора основан на свойствах буфера памяти – информация записывается в него с одной тактовой частотой, а считывается с другой, более высокой частотой. Если представить себе цепочку последовательно соединенных буферов, синхронизированных таким образом, что выходные пачки импульсов не перекрываются во времени, это и будет мультиплексор.

Основным параметром мультиплексора считается выходная скорость транспортного потока, которая у большинства моделей составляет55…60 Мбит/с. Существуют и образцы со скоростью до 100 Мбит/с. Разумеется, устанавливаемая на выходе скорость потока должна быть по крайней мере не ниже суммы скоростей всех объединяемых потоков. Превышение скорости выходного потока компенсируется введением нулевых пакетов на выходе мультиплексора.

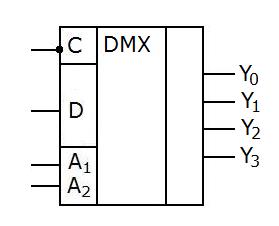

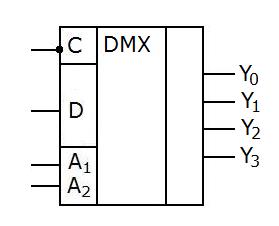

Демультиплексором называется функциональный узел компьютера, предназначенный для коммутации (переключения) сигнала единственного информационного входа D на один из n информационных выходов. Номер выхода, на который в каждый такт машинного времени подается значение входного сигнала, определяется адресным кодом A0,A1…,Am-1. Адресные входы m и информационные выходы n связаны соотношением n2m. В качестве демультиплексора может быть использован дешифратор DC. При этом информационный сигнал подается на вход разрешения Е (от англ. enable – разрешение). Стробируемый демультиплексор с информационным входом D, адресными входами А1, А0 и стробирующим входом С показан на рисунке 2.1. Демультиплексор выполняет функцию, обратную функции мультиплексора. Применительно к мультиплексорам и демультиплексорам пользуются так же термином «селекторы» данных.

Демультиплексоры используют для коммутации отдельных линий и многоразрядных шин, преобразования последовательного кода в параллельный. Как и мультиплексор, демультиплексор включают в себя дешифратор адреса. Сигналы дешифратора управляют логическими вентилями, разрешая передачу информации только через один из них (рис.1.1)

RS-триггер асинхронный

Асинхронный RS-триггер с инверсными входами

Асинхронный RS-триггер с инверсными входами

Асинхронный RS-триггер на элементах 2ИЛИ-НЕ.

Асинхронный RS-триггер на элементах 2ИЛИ-НЕ.

Условное графическое обозначение асинхронного RS-триггера.

Условное графическое обозначение асинхронного RS-триггера.

RS-триггер, или SR-триггер (от англ. Set/Reset — установить/сбросить) —асинхронный триггер, который сохраняет своё предыдущее состояние при неактивном состоянии обоих входов и изменяет своё состояние при подаче на один из его входов активного уровня. При подаче на оба входа активного уровня состояние триггера вообще говоря неопределённо, но в конкретных реализациях на логических элементах оба выхода принимают состояния либо логического нуля, либо логической 1. В зависимости от конкретной реализации активным входным уровнем может быть как логическая 1, так и логический 0. Так, в RS-триггере выполненном на 2 элементах 2И-НЕ активным входным уровнем является логический 0.

RS-триггер синхронный

| C

| S

| R

| Q(t)

| Q(t+1)

|

|

| x

| x

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| не определено

|

|

|

|

|

| не определено

|

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1.

Алгоритм функционирования синхронного RS-триггера можно представить формулой

{\displaystyle Q(t+1)={\overline {R}}\cdot \left(~Q(t)+S~\right)+x\cdot S\cdot R,}где x — неопределённое состояние.

Аналогично, триггер с доопределённым состоянием (Rs или rS) допускает наличие двух активных сигналов на момент тактирования, и переключается согласно тому сигналу, который для него является приоритетным.

Условное графическое обозначение синхронного RS-триггера.

Условное графическое обозначение синхронного RS-триггера.

Схема синхронного RS-триггера на элементах 2И-НЕ.

Схема синхронного RS-триггера на элементах 2И-НЕ.

D-триггеры

D-триггеры также называют триггерами задержки(от англ. Delay).

D-триггер синхронный

Пример условного графического обозначения (УГО) D-триггера с динамическим синхронным входом С и с дополнительными асинхронными инверсными входами S и R

D-триггер (D от англ. delay — задержка [13][14][15], либо от data [16] — данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом С информация записывается в течение времени, при котором уровень сигнала C=1. В триггерах с динамическим входом С информация записывается только в течение перепада напряжения на входе С. Динамический вход изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы (прямой динамический вход), то триггер срабатывает по фронту входного импульса, если от неё (инверсный динамический вход) — по срезу импульса. В таком триггере информация на выходе может быть задержана на один такт по отношению к входной информации.Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

·

Условное графическое обозначение D-триггера со статическим входом синхронизации С

D-триггер двухступенчатый

В одноступенчатом триггере имеется одна ступень запоминания информации, при этом, в состоянии записи триггер "прозрачен", т.е. все изменения на входе триггера повторяются на выходе триггера, что может привести к ложным срабатываниям устройств стоящих после триггера. В двухступенчатом триггере две ступени. Вначале информация записывается в первую ступень, все изменения на входе триггера во вторую ступень до сигнала перезаписи не попадают, затем, после перехода D-триггера первой ступени в режим хранения, информация переписывается во вторую ступень и появляется на выходе, что позволяет избежать состояния "прозрачности". Двухступенчатый триггер обозначают ТТ. Если первая ступень двухступенчатого D-триггера выполнена на статическом D-триггере, то двухступенчатый D-триггер называют двухступенчатым D-триггером со статическим управлением, а если на динамическом D-триггере, то двухступенчатый D-триггер называют двухступенчатым D-триггером с динамическим управлением.

T-триггеры[править | править вики-текст]

Т-триггер (от англ. Toggle — переключатель) часто называют счётным триггером, так как он является простейшим счётчиком до 2.

Т-триггер асинхронный[править | править вики-текст]

Асинхронный Т-триггер не имеет входа разрешения счёта - Т и переключается по каждому тактовому импульсу на входе С.

T-триггер синхронный[править | править вики-текст]

Условное графическое обозначение (УГО) синхронного T-триггера с динамическим входом синхронизации С на схемах.

Синхронный Т-триггер [17], при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер можно построить на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе.

Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К.

В двухступенчатом (Master-Slave, MS) D-триггере инверсный выход Q соединяется со входом D, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение Q, то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

JK-триггер

JK-триггер с дополнительными асинхронными инверсными входами S и R

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное, т.е. выполняется операция инверсии (чем он отличается от RS-триггеров с доопределённым состоянием, которые строго переходят в логический ноль или единицу, независимо от предыдущего состояния). Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — отключение) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации, поскольку понятие «одновременности» для асинхронных сигналов уже само по себе, в самом определении, содержит неопределённость поведения по типу гонки состояний (опять же, у Rs- и rS-триггеров этой проблемы нет, потому что они не осуществляют инверсию, а просто подчиняются тому сигналу, который для них приоритетен).

Теоретически, построение асинхронного JK-триггера по сути означало бы построение RS-триггера с динамическими входами, когда фронт сигнала J(S) переключает триггер в логическую единицу, а фронт сигнала K(R) — в ноль, даже если при этом уровень сигнала J продолжает сохраняться, и наоборот. Разумеется, «одновременность» переключения тут прямо запрещена и требует интервалов, определяемых паспортным быстродействием триггера. Триггер со статическим тактированием может вести себя похожим образом при сохранении высокого уровне на входе тактирования в момент переключения входов.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К

Алгоритм функционирования JK-триггера можно представить формулой

{\displaystyle Q(t+1)={\overline {Q}}(t)\cdot J+Q(t)\cdot {\overline {K}}.}

Условное графическое обозначение JK-триггера со статическим входом С

Простые логические элементы (НЕ, ИЛИ, И). Система параметров логических элементов.

- «НЕ» (NOT) – функция отрицания (инверсии сигнала). Потому его чаще называют - «инвертор». Графически, инверсия обозначается пустым кружочком вокруг вывода элемента (микросхемы). Обычно кружок инверсии ставится у выхода, но в более сложных логических элементах, он может стоять и на входе. Графическое обозначение элемента «НЕ» и его таблица истинности представлены на рисунке слева.

У элемента «НЕ» всегда один вход и один выход. По таблице истинности следует, что при наличии на входе элемента логического нуля, на выходе будет логическая единица. И наоборот, при наличии на входе логической единицы, на выходе будет логический ноль. Цифра «1» внутри прямоугольника обозначает функцию «ИЛИ», её принято рисовать и внутри прямоугольника элемента «НЕ», но это ровным счётом ничего абсолютно не значит.

Обозначение D1.1 означает, что D - цифровой логический элемент, 1 (первая) - номер микросхемы в общей схеме, 1 (вторая) - номер элемента в микросхеме. Точно также расшифровываются и другие логические элементы.

Часто, чтобы отличить цифровые микросхемы от аналоговых микросхем, применяют обозначения из двух букв: DD – цифровая микросхема, DA – аналоговая микросхема. В последующем, мы не будем заострять внимание на это обозначение, а вернёмся лишь тогда, когда это будет необходимым.

Самой распространённой микросхемой «транзисторно-транзисторной логики» (ТТЛ), выполняющей функцию «НЕ», является интегральная микросхема (ИМС) К155ЛН1, внутри которой имеется шесть элементов «НЕ». Нумерация выводов этой микросхемы

- «И» (AND) – функция сложения (если на всех входах единица, то на выходе будет единица, в противном случае, если хотя бы на одном входе ноль, то и на выходе всегда будет ноль). В алгебре-логике элемент «И» называют «конъюнктор». Графическое обозначение элемента «2И» и его таблица истинности представлены слева.

Название элемента «2И» обозначает, что у него два входа, и он выполняет функцию «И». На схеме внутри прямоугольника микросхемы рисуется значок «&», что на английском языке означает «AND» (в переводе на русский - И).

По таблице истинности следует, что на выходе элемента «И» будет логическая единица только в одном случае - когда на обоих входах будет логическая единица. Если хотя бы на одном входе ноль, то и на выходе будет ноль.

Самой распространённой микросхемой «транзисторно-транзисторной логики» (ТТЛ), выполняющей функцию «2И», является интегральная микросхема (ИМС) К155ЛИ1, внутри которой имеется четыре элемента «2И». Нумерация выводов этой микросхемы показана справа.

Для того, чтобы вам было понятнее что такое «2И», «3И», «4И», и т.д., приведу графическое обозначение и таблицу истинности элемента «3И».

По таблице истинности следует, что на выходе элемента «3И» будет логическая единица только в том случае - когда на всех трёх входах будет логическая единица. Если хотя бы на одном входе будет логический ноль, то и на выходе элемента также будет логический ноль. Самой распространённой микросхемой ТТЛ, выполняющей функцию «3И», является микросхема К555ЛИ3, внутри которо

=

= ;

; =

= ;

; ,

,  ,

,

.

.

Асинхронный RS-триггер с инверсными входами

Асинхронный RS-триггер с инверсными входами Асинхронный RS-триггер на элементах 2ИЛИ-НЕ.

Асинхронный RS-триггер на элементах 2ИЛИ-НЕ. Условное графическое обозначение асинхронного RS-триггера.

Условное графическое обозначение асинхронного RS-триггера. Условное графическое обозначение синхронного RS-триггера.

Условное графическое обозначение синхронного RS-триггера. Схема синхронного RS-триггера на элементах 2И-НЕ.

Схема синхронного RS-триггера на элементах 2И-НЕ.