Табличный ФП типа LUT представляет собою запоминающее устройство, хранящее значения искомых функций, считываемые по адресу-аргументу. Запоминающее устройство с организацией 2m × n имеет m адресных входов и n выходных линий. В таком запоминающем устройстве можно хранить таблицу для считывания n функций от m переменных. В память можно записывать любые числа, и, следовательно, разрядные столбцы этих чисел могут воспроизводить любые функции m переменных. Время вычисления результата не зависит от воспроизводимой функции и равно времени считывания слова из памяти.

Второй тип ФБ — схема, основой которой служат программируемые мультиплексоры. В этих ФБ выходная величина описывается некоторой порождающей функцией, соответствующей использованию всех входов схемы как информационных. При программировании на некоторые входы задаются константы 0 и 1, разные сочетания которых порождают целый спектр возможностей воспроизведения логических функций.

Третий тип ФБ — "мелкозернистые" блоки, составленные из транзисторных пар, выделяемых из цепочек транзисторов с n - и р-каналами. Из таких пар собираются логические элементы.

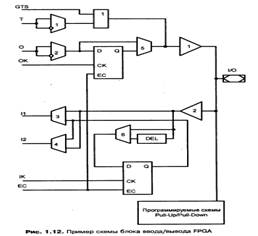

Типичную структуру ФБ FPGA с триггерной памятью конфигурации микросхемы семейства Spartan фирмы Хilinх (см. рис.).

В функциональных блоках этих микросхем логические преобразования выполняются тремя LUT-блоками (функциональными преобразователями ФП) G, F и Н. Преобразователи G, F— программируемые запоминающие устройства (ЗУ) с организацией 16x1, способные воспроизводить любые функции четырех переменных, значения которых могут быть переданы на выходы Y и X через мультиплексоры 4 и 6 при соответствующем их программировании (через линии верхних входов мультиплексоров).

Через верхний вход мультиплексора 1 и нижний вход мультиплексора 2 функции G и F могут быть поданы на ФП-Н (ЗУ с организацией 8x1) для образования "функции от функций" с целью получения результирующей функции, зависящей от более чем четырех аргументов. К третьему входу ФП-Н подключен входной сигнал H1, так что Н =f(G, F, HI). Аргументами для ФП-Н, поступающими от мультиплексоров 1 и 2, в зависимости от их программирования может быть не только набор G, F, H1, но также наборы G, H1, DIN; SR, H1, DIN; SR, H1, F. Линии DIN и SR используются либо для передачи в триггер непосредственно входных данных и сигнала установки/сброса (Set/Reset), либо как входы ФП-Н.

Пример схемы функционального блока FPGA

Перечисленные ресурсы логической части ФБ позволяют воспроизводить:

- любую функцию с числом аргументов до 4 включительно плюс вторую такую же функцию плюс любую функцию с числом аргументов до трех; - любую функцию 5 аргументов (одну);

- любую функцию 4 аргументов и одновременно некоторые функции 6 аргументов, некоторые функции с числом аргументов до 9.

Сигналы H1, DIN, SR, ЕС являются для ФБ входными, они подаются на его внутренние схемы через группу из четырех мультиплексоров MUX "4—1" (на рис. не показаны), к которым подключены 4 линии внешней шины управления С1...С4.

Это позволяет распределять сигналы H1, DIN, SR и ЕС по линиям С1...С4 в любом желаемом варианте.

Мультиплексоры 3...6 направляют те или иные сигналы данных управления на триггеры 1 и 2. Триггеры могут использоваться для фиксации и хранения выходных сигналов функциональных преобразователей или же работать независимо от них. Входной сигнал ФБ DIN может быть прямым входом для любого триггера. Сигнал H1 тоже можно передавать любому триггеру, но через ФП Н, что вносит в цепь его передачи некоторую задержку.

Оба триггера имеют общие входы СК тактирования от сигнала К, разрешения тактирования ЕС и установки/сброса SR. Внутренние программируемые цепи в схеме триггера (на рис. не показаны) позволяют индивидуально программировать полярность тактирующего сигнала СК. Сигнал ЕС синхронизирован с сигналом СК, сигнал SR асинхронный и для каждого триггера с использованием внутренних цепей триггера программируется как сигнал установки или сброса. Этот сигнал определяет состояние, в котором окажется триггер после процесса конфигурации микросхемы. Конфигурация определяет и характер воздействия на триггеры импульсов GSR (Global SR) и SR при работе схемы.