Индивидуальные и групповые автопоилки: для животных. Схемы и конструкции...

История создания датчика движения: Первый прибор для обнаружения движения был изобретен немецким физиком Генрихом Герцем...

Индивидуальные и групповые автопоилки: для животных. Схемы и конструкции...

История создания датчика движения: Первый прибор для обнаружения движения был изобретен немецким физиком Генрихом Герцем...

Топ:

Проблема типологии научных революций: Глобальные научные революции и типы научной рациональности...

Когда производится ограждение поезда, остановившегося на перегоне: Во всех случаях немедленно должно быть ограждено место препятствия для движения поездов на смежном пути двухпутного...

Выпускная квалификационная работа: Основная часть ВКР, как правило, состоит из двух-трех глав, каждая из которых, в свою очередь...

Интересное:

Лечение прогрессирующих форм рака: Одним из наиболее важных достижений экспериментальной химиотерапии опухолей, начатой в 60-х и реализованной в 70-х годах, является...

Национальное богатство страны и его составляющие: для оценки элементов национального богатства используются...

Искусственное повышение поверхности территории: Варианты искусственного повышения поверхности территории необходимо выбирать на основе анализа следующих характеристик защищаемой территории...

Дисциплины:

|

из

5.00

|

Заказать работу |

|

|

|

|

В вычислительной технике в основном используются принципы однотактной либо двухтактной синхронизации, которые обеспечивают разный уровень предсказуемости поведения вычислительного устройства.

В вычислительном устройстве можно выделить группы регистров и триггеров, которые образуют уровни, причем при их соответствующем тактировании. Информация передается от одного уровня к другому, претерпевая по пути обработку в логических схемах.

Принцип двухтактной синхронизации применяется только тогда, когда защитный промежуток между фазами достаточно велик, а это приводит к существенному уменьшению быстродействия вычислительного устройства.

Если в вычислительном устройстве используется RS либо другие асинхронные триггеры, а также схемы с защелками, то такие схемы нужно отнести к схемам с 2-хтактной синхронизацией. При реализации проекта ПЛИС двойная синхронизация практически никогда не применяется.

Двухтактная синхронизация относится к асинхронному управлению. Другим случаем такого управления яв-ся асинхронный сброс триггера вычислительного ус-ва. Если сигнал сброса не согласован по времени с синхросигналом, или если в схеме используется несколько сигналов сброса, то она может функционировать некорректно.

При однотактной синхронизации все триггеры выполнены как синхронные и тактируются фронтом одного синхросигнала.

20 Состав и назначение библиотеки IEEE.

Библиотека IEEE представляет собой стандарт для всех фирм поставщиков систем автоматизированного проектирования микросхем, включая программы симуляции, верификации и синтеза.

Использование типов, функций и процедур этой библиотеки позволяет надежно выявить максимальное количество ошибок в проекте на большинстве этапов его разработки. Пакеты этой библиотеки обычно не транслируются, они в оптимизированном виде уже встроены в симуляторы и компиляторы. Это позволяет выполнять моделирование с max скоростью.

|

|

1.Пакеты std _ logic _ arith, std _ logic _ unsigned, std _ logic _ signed.

Эти пакеты предназначены для стандартизации и упрощения программирования и моделирования вычислительных устройств, в которых выполняются арифметические операции, а также для обеспечения последующего их синтеза. Кроме этого определены также функции преобразования типов.

2.Пакеты numeric _ bit и numeric _ std.

Отличаются между собой тем, что в первом стандарте функции и типы объявлены базовым типом bit, а во втором над базовым типом std_logic.

3. Пакеты math_real, math_complex.

Предназначены для разработки вычислительных устройств в которых производятся математические вычисления различной сложности. В первом определены константы, элементарные функции и процедуры для работы с операндами типа real, во втором пакете – для работы с комплексными числами, что необходимо в алгоритмах цифровой обработки сигнала.

4. Пакет std _ logic _ textio предназначен для файлового ввода вывода данных при моделировании.

5. Пакеты vital_primitives, vital_timing.

Содержат атрибуты, типы, константы, функции и процедуры для разработки поведенческих моделей сверхбольших интегральных схем на уровне вентилей.

Исп. компон. элемента «И» и оператор конструкции компонента

Задача №1

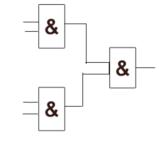

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. При описании архитектуры используйте компонент элемента “И” и оператор конструкции компонента.

Решение

-- Интерфейс “И”

entity entity_and is

port (in1, in2: in bit;

q: out bit);

end entity_and;

-- Архитектура “И”

architecture architecture_and of entity_and is

begin

q<=in1 and in2;

end architecture_and;

-- Интерфейс основного компонента

entity entity_main is

port (i1, i2, i3, i4: in BIT;

QQ: out BIT);

end entity_main;

-- Архитектура основного компонента

|

|

architecture architecture_main of entity_main is

component entity_and

port (in1, in2: in BIT;

q: out BIT);

end component;

signal q1,q2: BIT;

begin

label1: entity_and

port map (i1,i2,q1);

label2: entity_and

port map (i3,i4,q2);

label3: entity_and

port map (q1,q2,QQ);

end architecture_main;

Исп комп эл «И» и «И-НЕ»

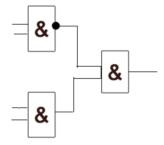

Задача №2

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. При описании архитектуры используйте компонент элемента “И” и “И-НЕ” и оператор конкретизации компонента.

Решение

- Интерфейс “ И ”

entity entity_and is

port (in1, in2: in BIT;

q: out BIT);

end entity_and;

-- Архитектура “ И ”

architecture architecture_and of entity_and is begin

q<=in1 and in2;

end architecture_and;

-- Интерфейс “ И - НЕ ”

entity entity_and_not is

port (in1, in2: in BIT;

q: out BIT);

end entity_and_not;

-- Архитектура “ И - НЕ ”

architecture architecture_and_not of entity_and_not is begin

q<= not (in1 and in2);

end architecture_and_not;

-- Интерфейс основного компонента

entity entity_main is

port (i1, i2, i3, i4: in BIT;

QQ: out BIT);

end entity_main;

-- Архитектура основного компонента

architecture architecture_main of entity_main is

component entity_and

port (in1, in2: in BIT; q: out BIT);

end component;

component entity_and_not

port (in1, in2: in BIT; q: out BIT);

end component;

signal q1,q2: BIT;

begin

label1: entity_and_not port map (i1,i2,q1);

label2: entity_and port map (i3,i4,q2);

label3: entity_and port map (q1,q2,QQ);

end architecture_main;

3 Используйте генератор generate

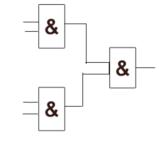

Задача №3

Опишите на языке VHDL интерфейс и архитектуру объекта, схема которого представлена на рисунке. При описании архитектуры используйте генератор generate.

Решение

-- Интерфейс “И”

entity entity_and is

port (in1, in2: in BIT; q: out BIT); end entity_and;

-- Архитектура “И”

architecture architecture_and of entity_and is begin

q<=in1 and in2;

end architecture_and;

-- Интерфейс основного компонента

entity entity_main is

port (inp: in BIT_VECTOR(1 to 4);

QQ: out BIT);

end entity_main;

-- Архитектура основного компонента

architecture architecture_main of entity_main is

component entity_and port (in1, in2: in BIT; q: out BIT); end component;

signal qi: BIT_VECTOR(1 to 2);

begin

q1: for i in 0 to 1 generate

label1: entity_and port map (inp(i+1),inp(i+2),qi(i+1));

end generate;

label2: entity_and port map (qi(1), qi(2),QQ);

end architecture_main;

|

|

|

Семя – орган полового размножения и расселения растений: наружи у семян имеется плотный покров – кожура...

Биохимия спиртового брожения: Основу технологии получения пива составляет спиртовое брожение, - при котором сахар превращается...

Папиллярные узоры пальцев рук - маркер спортивных способностей: дерматоглифические признаки формируются на 3-5 месяце беременности, не изменяются в течение жизни...

История развития хранилищ для нефти: Первые склады нефти появились в XVII веке. Они представляли собой землянные ямы-амбара глубиной 4…5 м...

© cyberpedia.su 2017-2024 - Не является автором материалов. Исключительное право сохранено за автором текста.

Если вы не хотите, чтобы данный материал был у нас на сайте, перейдите по ссылке: Нарушение авторских прав. Мы поможем в написании вашей работы!