Отличительные особенности RISC-архитектуры процессоров.

RISC (restricted (reduced) instruction set computer — компьютер с сокращённым набором команд) — архитектура процессора, в которой быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание инструкций между несколькими исполнительными блоками).

Характерные особенности RISC-процессоров:

● Одинакова длина команд.

● Единый формат команд. Или, по крайней мере, использование не более двух-трех форматов.

● Операндами всех арифметических и логических команд могут быть только регистры.

● Команды выполняют только простые действия.

● Выполнение любой команды производится не дольше, чем за один такт.

● Большой регистровый файл (32 или большее число регистров по сравнению с 8-16 регистрами в CISC).

● Только простая адресация.

Отличительные особенности CISC-архитектуры процессоров.

CISC (Complex instruction set computer — компьютер с полным набором команд) концепция проектирования процессоров, которая характеризуется следующим набором свойств:

● нефиксированное значение длины команды;

● арифметические действия кодируются в одной команде;

● небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Для CISC-процессоров характерно:

● сравнительно небольшое число регистров общего назначения (16 регистров у классических CISC-архитектур);

● большое количество машинных команд, некоторые из которых нагружены семантически аналогично операторам высокоуровневых языков программирования и выполняются за много тактов;большое количество методов адресации;

● большое количество форматов команд различной разрядности;

● преобладание двухадресного формата команд;

● наличие команд обработки типа регистр-память.

Сложность архитектуры и системы команд x86 остается и является главным фактором, ограничивающим производительность процессоров на ее основе.

Архитектуры памяти: гарвардская и фон-Неймана. Особенности и сочетание с архитектурой процессорного ядра (RISC, CISC). Архитектура памяти МК ATtiny2313: регистры общего назначения, область ввода/вывода, ОЗУ, память программ.

В архитектуре фон-Неймана применяется однородная память микропроцессора. В эту память могут записываться различные программы. При этом специальная программа-загрузчик работает с ними как с данными. Затем управление может быть передано этим программам и они уже начинают выполнять свой алгоритм. При подобном подходе к управлению микропроцессором удается достигнуть максимальной гибкости микропроцессорной системы.

В качестве недостатка архитектуры фон-Неймана можно назвать возможность непреднамеренного нарушения работоспособности системы (программные ошибки) и преднамеренное уничтожение ее работы (вирусные атаки).

RISC использует только гарвардскую архитектуру.

Архитектура AVR содержит два основных вида памяти:

● Память данных;

● Память программ.

Кроме того, микросхема ATtiny2313 имеет EEPROM-память для долговременного хранения данных. Все три вида памяти представляют собой непрерывные области с линейно возрастающими адресами.

Системная перепрограммируемая Flash-память программ.

Микросхема содержит 2 Кбайт встроенной перепрограммируемой памяти для хранения программ. Так как все команды, используемые в AVR, имеют размер 16 или 32 бита, память организована как 1Kx16.

Память данных SRAM.

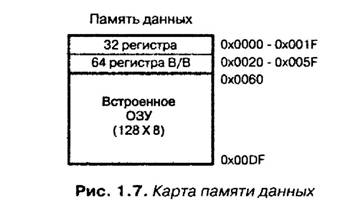

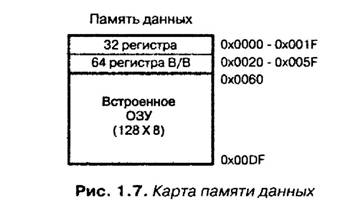

Всего адресное пространство ОЗУ содержит 224 ячейки, которые заняты:

➢ Файлом регистров общего назначения;

➢ Дополнительными регистрами ввода-вывода;

➢ Внутренней памятью данных.

Первые 32 ячейкисовмещены с файлом РОН. Следующие 64 ячейки – стандартная область, где располагаются все регистры ввода-вывода. И лишь оставшиеся 128 ячеек составляют внутреннюю память данных.

Регистры R26-R31 (X, Y, Z) служат указателями адреса при всех операция с косвенной адресацией.

К регистры R0-R31 можно также обращаться непосредственно по адресу в адресном пространстве (0x00-0x31) R0==0x00,R20==0x20.

При прямой адресации указывается полный адрес байта данных.

При косвенной адресации со смещением можно охватить до 63 ячеек, начиная с текущего базового адреса, на который указывает содержимое регистра Y или Z.

При использовании косвенной адресации с автоматическим преддекрементом и автоматическим постдекрементом после каждой операции чтения (записи) памяти изменяется адрес, записанный в регистр X, Y или Z.

Для всех способов адресации доступны все 32 регистра общего назначения, 64 регистра ввода-вывода и 128 байтов памяти данных SRAM.

Память данных EEPROM.

Микросхема ATtiny2313 содержит 128 байтов EEPROM-памяти.Она организована как отдельное адресное пространство для хранения данных, в котором каждый байт может быть отдельно прочитан или записан.

Последовательный интерфейс USI. Построение многопроцессорных систем, подключение периферийных устройств (микросхемы памяти, АЦП, ЦАП и пр.) через периферийный интерфейс SPI (один из режимов работы USI).

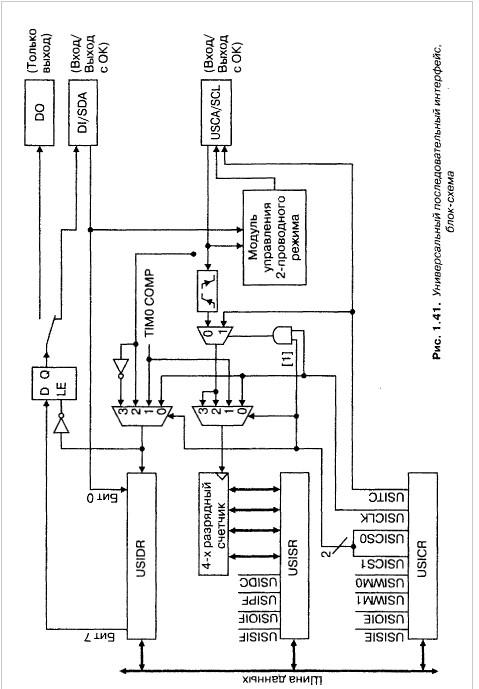

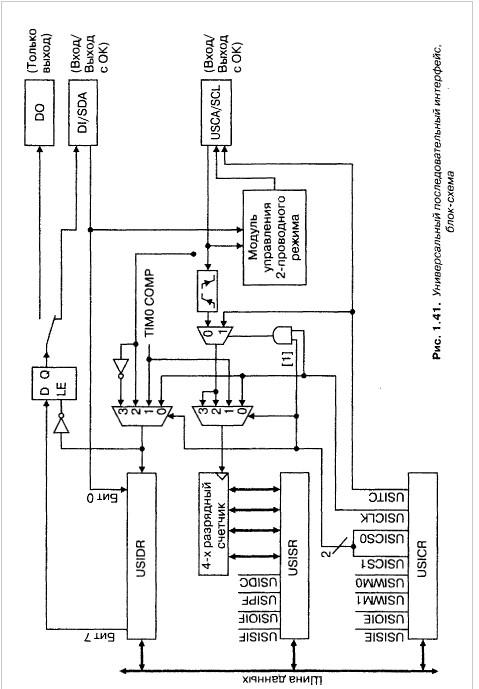

Универсальный последовательный интерфейс является основным средством последовательной передачи данных. Используя минимальное программное обеспечение, интерфейс USI позволяет достигать значительно более высоких скоростей передачи информации и использует меньше программной памяти, чем решения, основанные только на программном способе формирования канала связи.

Интерфейс USI имеет следующие основные особенности:

➢ двухпроводный синхронный режим передачи данных (Master или Slave, fSCLmax = fCK/16);

➢ трехпроводный синхронный режим передачи данных (Master, fSCKmax = fCK/2, Slave fSCKmax = fCK/4);

➢ прием данных с использованием прерывания;

➢ автоматическое пробуждение из режима Idle;

➢ в двухпроводном режиме: пробуждение из всех режимов сна, кроме Power-down;

➢ проверка стартового условия в двухпроводном режиме с возможностью вызова прерывания.

ПРИМЕРЫ ПОСТРОЕНИЕ МНОГОПРОЦЕССОРНЫХ СИСТЕМ, ПОДКЛЮЧЕНИЕ ПЕРЕФЕРИЙНЫХ УСТРОЙСТВ С ПОМОЩЬЮ SPI

19. Структура программы для МК (таблица векторов прерываний, подпрограмма инициализации, основной программный цикл, обработчики прерываний).

Вариант 1:)

Таблица векторов прерываний это первые 19 байт программы. Это значит, что при некотором прерывании контроль будет передан соответствующему адресу в начале программы. Например при переполнении WDT контроль будет передан по адресу 0x12 (фактически rcall 0x12). Также в момент передачи контроля на стек будет записан адрес возврата, по которому контроль вернется после выполнения команды RETI.

Основной программный цикл - это цикл, который запускается после RESET’а. RESET – самое первое прерывание, которое вылетает, когда контроллер включается или когда на ногу RESET приходит 1. Цикл реализуется обычно командой rjmp в самом начале программы. Эта команда передает управление дальше по программе (аналог main()).

Обработчики прерываний – процедуры, которые заканчиваются командой reti. Например:

Таблица прерываний:

...

reti

rjmp OBRABOTCHIK

reti

...

...

OBRABOTCHIK:

Код обработчика прерывания

reti

Такая структура позволяет задавать “функции” которые выполняются по прерываниям.

Вариант 2:)

Ниже приведена типичная структура для программ AVR ассебмлера.

* Комментарии, заголовок где идёт описание, копирайты и прочая погань.

* Заголовочная информация, определение констант, подключение внешних файлов, определение макросов и др.

* Код начала программы

* Основная структура программы

Заголовочная информация

В заголовке мы указываем включаемые файлы, тип устройства, определения имён для регистров, определение констант.

Тип процессора определяется подключаемым файлом, в этом файле прописаны адреса регистров ввода вывода, прерываний, расположение встроенной памяти SRAM и EEPROM. Файлы называются по имени чипа, например для Atmega8535 - m8535def.inc.

В заголовочном файле также определены регистры XH, XL, YH, YL, ZH and ZL. Они нужны для определения частей 16-ти разрядных указателей X, Y or Z. Все порты так же определены в данном файле, например PORTA представлено его HEX значение. Имена портов соответствую описаниям в Datashet. Так же определены единичные биты портов. Например для доступа 5 го бита порта C используется PINC5, и так же соответствует фирменному описанию.

Другие вещи которые должны быть включены в заголовке программы это определение регистров, например

.DEF FLAJOK = R16; переименование регистра

Там же, в заголовке программы определяются используемые константы Например частота тактового генератора, что позволит при изменении параметров тактового генератора не менять все части программы

.EQU fq = 4000000; частота тактового генератора

Код начала программы

В начале кода по адресу 0x0000 находиться вектор сброса, т.е. место куда перейдёт программа после включения питания или сигнала RESET. Сразу за этим адресом с адреса 0x0002 начинается таблица векторов прерываний. Выглядит это приблизительно так

.CSEG

.ORG $0000

rjmp Main; Вектор сброса

reti; Прерывание 1

reti; Прерывание 2

Отличительные особенности RISC-архитектуры процессоров.

RISC (restricted (reduced) instruction set computer — компьютер с сокращённым набором команд) — архитектура процессора, в которой быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание инструкций между несколькими исполнительными блоками).

Характерные особенности RISC-процессоров:

● Одинакова длина команд.

● Единый формат команд. Или, по крайней мере, использование не более двух-трех форматов.

● Операндами всех арифметических и логических команд могут быть только регистры.

● Команды выполняют только простые действия.

● Выполнение любой команды производится не дольше, чем за один такт.

● Большой регистровый файл (32 или большее число регистров по сравнению с 8-16 регистрами в CISC).

● Только простая адресация.