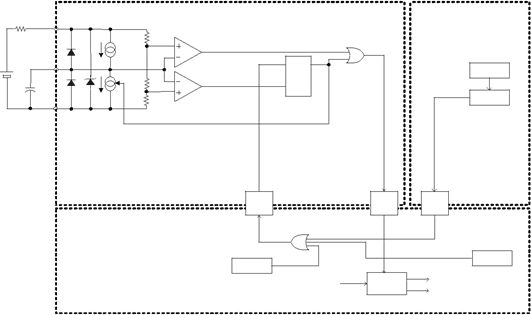

| VAA

|

|

|

|

|

|

| Vth1

| `

|

|

|

|

|

|

| COMP1

|

|

|

|

|

| CSD

|

| OC

| S

| Q

|

|

|

|

|

|

|

|

| `

|

|

|

|

|

| Ct

| COMP2

|

| R

|

|

|

|

|

|

|

|

|

| Vth2

|

|

|

|

|

|

| VSS

|

|

|

|

|

|

UVLO(VB)

OC DET (H)

| HV

| FLOATING INPUT

| HV

|

| HV

| FLOATING HIGH SIDE

|

|

| LEVEL

|

| LEVEL

|

| LEVEL

|

|

|

| SHIFT

|

| SHIFT

|

| SHIFT

| LOW SIDE

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| OC DET (L)

|

|

| UVLO(VCC)

|

| SD

|

|

|

|

|

|

| PWM

| DEAD TIME

|

| HO

|

|

|

|

|

| LO

|

|

|

|

|

|

| `

|

|

|

|

|

|

|

|

|

|

Figure 8 Shutdown Functional Block Diagram

Управление защитой

| Блок управления внутренней защитой диктует

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1

|

| VAA

| CSH

| 16

|

|

|

|

| рабочий режим, нормальный, или выключение,

|

|

|

|

|

|

| GND

| VB

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2

|

| 15

|

|

|

|

| используя вход CSD pin. В режиме выключения, IC

|

|

|

|

|

|

| IN-

| HO

|

|

|

|

|

|

|

|

|

| 3

|

| 14

|

|

|

|

| заставляет LO и HO вывести 0V относительно COM и

|

|

|

|

|

|

| COMP

| VS

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4

|

| 13

|

|

|

|

| VS соответственно, чтобы отключить MOSFET.

|

|

|

|

|

|

| CSD

| VCC

|

|

|

|

|

| Ct

|

|

|

| 5

|

| 12

|

|

|

|

|

|

|

|

|

| VSS

| LO

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Вывод CSD обеспечивает пять функций.

|

|

|

|

| 6

|

| 11

|

|

|

|

|

|

|

|

|

| VREF

| COM

|

|

|

|

|

|

|

|

|

| 7

|

| 10

|

|

|

|

| 1.

| Таймер задержки включения питания

|

|

|

|

|

|

| OCSET

| DT

|

|

|

|

|

|

|

|

|

|

|

| 8

|

| 9

|

|

|

|

| 2.

| Таймер само-сброса

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3.

| Остановка работы

| |

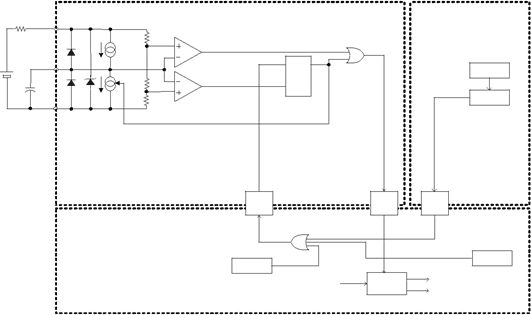

Figure 9 Self Reset Protection Configuration

|

4. Конфигурация с запиранием от защит

5. Остановка состояния выхода (host I/F)

| Вывод CSD не может быть параллельным другому

|

Проектирование Ct

|

|

|

|

|

|

| IRS2092 (S).

| Конденсатор Ct используется для.

|

|

|

| программирования времени tRESET и tSU.

|

|

| | | | |

|

Само-сброс защиты

|

| · tRESET это время, прошедшее с момента,

|

|

|

| когда микросхема перешла в режим

|

|

|

|

|

|

|

|

| Помещенный конденсатор между CSD и VSS

|

| выключения, до момента возобновления работы IC.

|

|

|

| tRESET должен быть достаточно продолжительным,

|

|

| IRS2092(S) сбрасывается после завершения

|

|

|

|

| чтобы избежать перегрева полевых МОП-транзисторов из за повторяющейся

|

|

| режима выключения.

|

|

|

|

| последовательности отключения и возобновления

|

|

|

|

|

|

|

|

| После события OCP вывод CSD разряжает

|

| работы во время перегрузки. В большинстве

|

|

|

| приложений минимальное рекомендуемое время

|

|

| напряжение Ct VCSD вниз до нижнего порога

|

|

|

|

| tRESET составляет 0,1 секунды..

|

|

| Vth2 чтобы сбросить внутреннюю блокировку выключения. Затем IRS2092 (S) начинает

|

|

|

|

| · tSU это промежуток времени между работой ИС в

|

|

| заряжать Ct в попытке возобновить работу.

|

|

|

| Когда напряжение на контакте CSD поднимается

|

| режиме выключения до момента, когда IC

|

|

|

| отключает режим выключения, чтобы начать

|

|

| выше верхнего порогового значения Vth1, ИС

|

|

|

|

| нормальную работу.

|

|

| возобновляет нормальную работу.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Значение Ct для tRESET и tSU определяют следующие уравнения:

| t RESET

| =

|

| Ct × V DD

| [s]

|

|

| 1.1× I CSD

|

|

|

|

|

|

|

| t SU =

| Ct × V DD

|

| [s]

|

|

| 0.7 × I CSD

|

|

|

|

|

|

| Где

| ICSD = the ток заряда / разряда на

|

|

| CSD pin

|

|

|

|

|

|

|

|

| VDD

| = Блуждающее входное

|

|

|

| напряжение относительно питания VSS.

|

|

| | | | | | | | |

Завершение работы

IRS2092 (S) может быть отключен внешним SD-сигналом выключения. На рисунке 10 показано, как добавить внешний канал разрядки для выключения ШИМ.

| 1

| VAA

| CSH

| 16

|

|

|

| GND

| VB

|

|

|

| 2

| 15

|

|

|

| IN-

| HO

|

|

|

| 3

| 14

|

|

|

| COMP

| VS

|

|

|

| 4

| 13

|

|

|

|

| 1

| VAA

| CSH

| 16

|

|

|

|

| 2

| GND

| VB

| 15

|

|

|

| <10k

| 3

| IN-

| HO

| 14

|

|

|

|

|

|

|

|

|

|

|

| 4

| COMP

| VS

| 13

|

|

|

|

| 5

| CSD

| VCC

| 12

|

|

| SD

|

| 6

| VSS

| LO

| 11

|

|

|

|

|

|

|

|

| 7

| VREF

| COM

| 10

|

|

|

|

| 8

| OCSET

| DT

| 9

|

|

Figure 11 Latched Protection with Reset Input