В разработанной архитектуре существуют следующие взаимодействия между функциональными блоками:

- Взаимодействие между блоком приема кадра и блоком адресации;

- Взаимодействие между блоком приема кадра и блоком арбитра;

- Взаимодействие между блоком приема кадра и блоком отправки данных.

Взаимодействие между блоком приема кадра и блоком адресации осуществляется с помощью флага наличия пакета, по шине передачи адреса отправки(SA) и адреса назначения (DA). Взаимодействие осуществляется следующим образом:

1. Каждый блок приема кадра имеет флаг наличия пакета. Данный флаг сигнализирует блоку арбитра MAC – адресов о том, что начался приём

2. При появление флага наличия пакета блок арбитра добавляет конкретный блок приема в очередь обращения к таблице MAC – адресов.

3. При наступление очереди конкретного блока приема арбитр передает модулю таблицы MAC – адресов значение адреса назначения данного пакета. Если есть конкретный адрес порта, то он передается модулю приема. Если нет, то данный пакет является широковещательным и передается по всем портам.

4. Затем модулю таблицы передается значение адреса отравки и модуль сохраняет номер порта, с которого был принят данный пакет.

Взаимодействие между блоком приема и арбитража осуществляется при помощи флагов наличия пакета на отправку и шины данных определяющих расположение пакета в памяти и размера пакета. Взаимодействие осуществляется следующим образом:

1. Блок отправки пакета при приеме и обработке пакета (определения его длины и адреса назначения) передает данные модулю очереди FIFO и выставляет флаг наличия пакета на отправку модулю арбитража.

2. Блок арбитража при появлении флага наличия пакета, проверяет идет ли передача данных на конкретный порт. Если передача данных не идет, то блок арбитража считывает длину пакета данных и указатель пакета в памяти. В противном случае, если передача данных идет, блок арбитража формирует очередь и ожидает окончания передачи предыдущего пакета.

3. Следующим действием блок арбитра инициализирует передачу данных по шине согласно стандарту Avalon – ST. Выбор данного интерфейса обусловлен необходимостью увеличения скорости считывания данных с памяти RAM по сравнению скорости записи, которая определяется стандартом GMII. Сделать это можно двумя способами: увеличением частоты считывания данных либо увеличением разрядности шины передачи данных. Поскольку увеличение может критично сказаться при реализации выбранной архитектуры, может потребоваться более «скоростная» микросхема, то логичным будет является вариант повысить разрядность шины данных. Также необходимо учесть возможность наличия широковещательных пакетов и возможности передачи пакета на все порты. Особенности интерфейса Avalon-ST (наличие сигналов валидности передаваемого байта и разрядность до 256 бит) позволяют осуществить передачу данных между блоками.

Описание модулей

1) Receiver- Модуль приёма кадра;

На вход этого модуля поступают данные по интерфейсу GMII поступают:

- i_clk – тактовый сигнал;

- i_data - 8 бит данных (из кадра, захваченного WireShark);

- i_dv – валидность данных (разрешение на запись);

- i_er – сигнализирует об ошибке.

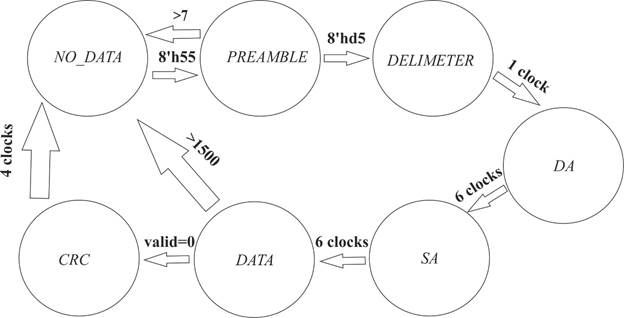

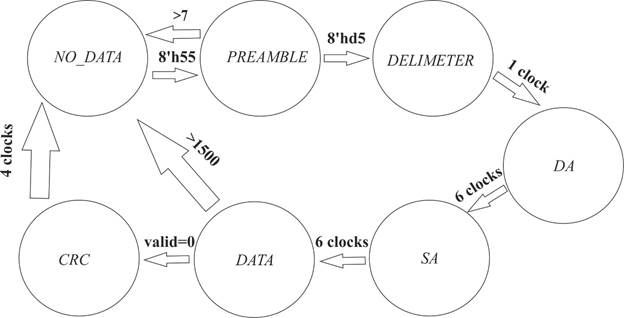

Модуль приёма представляет собой конечный автомат, в котором 7 состояний. Он отслеживает текущее поле кадра. В данном модуле данные задерживаются на 4 такта.

Первое состояние – NO_DATA, остальные – поля кадра Ethernet стандарта IEEE 802.3.

Рисунок 2.7 – Граф автомата приёмника

Состояние NO_DATA – автомат выходит из него в Preamble, когда приходит первый байт преамбулы - 8’h55.

Preamble – преамбула. Если она длиннее чем 7 байт, то автомат возвращается в состояние NO_DATA. Когда приходит байт - 8’hD5 – автомат переключается в состояние Delimeter.

Delimiter – через 1 байт переходит в состояние SA.

DA – адрес назначения - через 6 байт переходит в состояние DA.

SA - адрес источника - через 6 байт переходит в состояние DATA.

DATA – поле данных кадра. Если поле данных длиннее чем 1500 байтов, то это ошибка и автомат переключается в состояние NO_DATA.

CRC – поле контрольной суммы. Также тут происходит проверка контрольной суммы. Для этого была использована готовую функцию для подсчёта CRC, предоставленную компанией “МИКРАН”. Проверка проходила по следующему алгоритму: параллельно с приёмом пакета, начиная с поля DA до CRC данные обрабатываются функцией; если после этого получился остаток 32’hC704DD7B, то контрольная сумма подсчитана верно. В противном случае –

это ошибка.

У этого модуля 7 выходов:

- o_rx_dv_4cd, o_rx_d4cd, o_rx_er_4cd - поступают те же входные данные (i_dv, i_data, i_er), но задержанные на 4 такта;

- o_fsm_state – состояние автомата;

- o_fsm_state_changed – сигнал о смене состояния автомата;

- osa – адрес источника, для записи в таблицу маршрутизации;

- osa_new – сигнал о том, что приходит новый пакет.

Чтение SA происходит сразу с приёмника кадра.

2) Модуль RAM - Копирование пакета в память;

Модуль соединён с выходами приёмника. На него поступают:

- i_rx_data - данные;

- i_dv;

- i_er;

- i_fsm_state – состояние приёмника;

Модуль тоже представляет собой конечный автомат, его работу можно представить графом на рисунке 2.8.

Рисунок 2.8 – Граф конечного автомата модуля записи в память

В память записываются данные, соответствующие всем состояниям, кроме NO_DATA, Preamble, Delimeter. Делиметр выступает сигналом для записи. Запись прекращается, когда сигнал i_dv переходит в состояние логического нуля. Если i_er = 1 (неправильная контрольная сумма), то кадр удаляется.

Память выполнена в виде кольцевого буффера - т.е когда она заполнилась, указатель записи идёт в самое начало.

Кроме записи в память RAM модуль выполняет следующую функцию:

Когда - DA, модуль ищет этот адрес в таблице маршрутизации. Если он находит его, то модуль считывает номер порта из таблицы.

3) FIFO буфер:

После того, как кадр записался в память, информация о его длине и указатель на начало кадра передаётся в одно из 3 FIFO. Их 3, так как, к примеру, данные с 0 порта могут быть переданы на 1,2,3 порт.

4) Таблица для MAC-адресов:

Данная таблица имеет 214 адресов. В ячейки кладутся номер порта и время, которое хранится этот номер. Через 5 минут после записи ячейка очищается. Адресация проводится по последним 14 битам MAC адреса.

В этом модуле 3 входа:

- i_port_num – номер порта;

- i_SA – через этот вход с приёмника поступают SA, а затем регистрируется и записывается номер порта;

- i_DA – адрес получателя, который приходит с предыдущего модуля RAM. Как только приходит DA, этот MAC адрес ищется в таблице и на выход подаётся номер порта.

5) MAC арбитр:

Данный модуль обеспечивает поочерёдный доступ приёмников к таблице MAC-адресов путём поочерёдного опроса на наличие новых пакетов.

6) Transmitter - Модуль формирования кадра.

Этот модуль представляет собой конечный автомат, в котором 8 состояний. Первое состояние указывает на паузу, когда формирование нового кадра не происходит. Остальные 6 состояний соответствуют формированию соответствующих полей кадра Ethernet IEEE 802.3.

Заключение

По итогам прохождения практики достигнуты следующие результаты:

1. Изучены части стандарта протокола Ethernet и структура его кадра. Были изучены основы языка Verilog.

2. Разработана архитектура коммутатора с 4 портами на основе коммутационной матрицы с арбитражем (на виртуальных очередях).

3. На языке Verilog написано 50% модулей из разработанной архитектуры, а именно: блок приема кадра, включающий в себя модель приема кадра, модуль двухпортовой памяти и модуль очередей, блок адресации, включающий в себя модуль таблицы MAC-адресов и логику записи в таблицу, частично разработан модуль передатчика пакета.

4. Начат процесс соединения модулей коммутатора, имеется рабочая входная часть коммутатора.